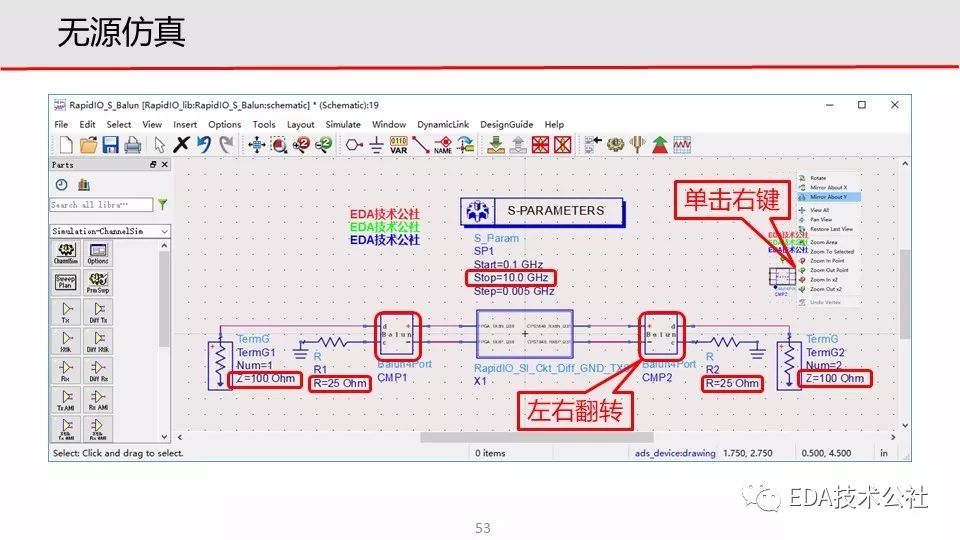

一、参考前文的前仿真S参数无源链路搭建方法,使用SIPro/PIPro提取的走线S参数符号,搭建后仿真无源仿真链路原理图,并按下图所示修改相关参数。

二、单击快捷图标栏的齿轮图标启动仿真,仿真完毕后,参考前文的前仿真中回波损耗和TDR阻抗曲线图提取方法提取后仿真的回波损耗和TDR阻抗曲线图。

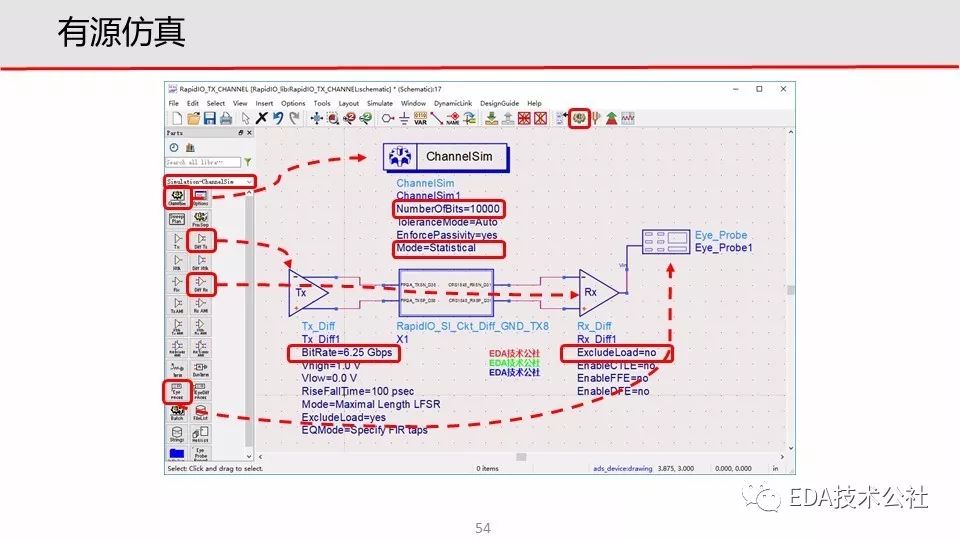

三、参考前文的前仿真有源链路搭建方法,搭建后仿真有源链路原理图,并按下图所示修改相关参数,眼图模板的设置方法一并参考前文。

四、单击快捷图标栏的齿轮图标启动仿真,仿真完毕后,参考前文的前仿真中眼图的提取方法提取后仿真的眼图。

至此,一个简单的串行链路后仿真就完成了,根据不同信号的标准规范要求,对曲线图进行分析,并留有一定的余量,如有不满足,则需要优化PCB文件上的走线、过孔或器件参数。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4318文章

23079浏览量

397436 -

串行

+关注

关注

0文章

237浏览量

33832

原文标题:ADS操作系列之串行链路后仿真

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

构建JESD204B链路的步骤

是:代码组同步 (CGS)、初始信道对齐序列 (ILAS) 和用户数据。今天我将探讨在 TX 与 RX 之间必然会出现的信号发送技术,完成构建有效链路所需的必要步骤。假设您已经在 TX 与 RX 之间

发表于 09-13 09:55

基于高速串行数字技术的JESD204B链路延时设计

描述JESD204B 链路是数据转换器数字接口的最新趋势。这些链路利用高速串行数字技术提供很大的益处(包括增大的信道密度)。此参考设计解决了

发表于 11-21 16:51

高速时钟如何驱动串行链路?

的时钟)。高速时钟如何驱动串行链路?我应该在哪里连接?以上来自于谷歌翻译以下为原文Hi all, I want to connect twoFreeware ML605 boards

发表于 02-13 06:22

构建JESD204B链路的步骤

(CGS)、初始信道对齐序列 (ILAS) 和用户数据。今天我将探讨在 TX 与 RX 之间必然会出现的信号发送技术,完成构建有效链路所需的必要步骤。假设您已经在 TX 与 RX 之间建立了所需的电气

发表于 11-21 07:18

MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统

MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统接口

概述

MAX9249串行器带有LVDS系统接口,采用Maxim吉比特

发表于 03-28 09:17

•1145次阅读

MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统

MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统接口

概述

MAX9249串行器带有LVDS系统接口,采

发表于 05-20 08:51

•835次阅读

MAX9265吉比特多媒体串行链路串行器

在MAX9265串行链路(GMSL)串行接口功能的LVDS系统和高带宽数字内容保护(HDCP)的DVD和蓝光™视频和音频数据加密千兆多媒体内容保护。与任何支持HDCP GM

发表于 01-19 09:37

•1159次阅读

JNEye链路分析工具支持迅速评估高速Altera FPGA和SoC中的高速串行链路性能

Altera公司今天发布JNEye链路分析工具,提供验证和电路板级全套设计工具。JNEye支持设计人员迅速方便的评估高速Altera FPGA和SoC中的高速串行链

发表于 09-14 15:10

•1416次阅读

串行链路后仿真操作步骤

串行链路后仿真操作步骤

评论