Vivado® Design Suite 提供两种方法可加速产品上市进程,提高工作效率。可构建 Vivado 布局布线。在任何设计阶段处理任何类型的 ECO 问题,并可加快运行时间,确保时序收敛进程。

增量编译:使用增量编译满足最后时刻 HDL 变动需求,仅针对已变动逻辑进行布局布线,从而可节省时间。

P&R 数据重复使用为时序驱动,可在不影响性能的情况下,加速运行时间。

平均速度比标准布局布线快 1 倍。

设计收敛保存可减少并加速迭代。

器件编辑器:使用器件编辑器通过强大的图形界面,以外科手术般的高精度编辑布局布线设计。

手工辅助布线可提供各种建议布线,在避免猜测与犯错的情况下,加速达到目标的进程。

广泛的交叉探测可帮助用户便捷管理逻辑至物理的分配。

设计变动记录为 Tcl 命令,有利于回放与脚本处理。

增量编译相对于器件编辑还是容易一些。本文主要讲述增量编译方法。

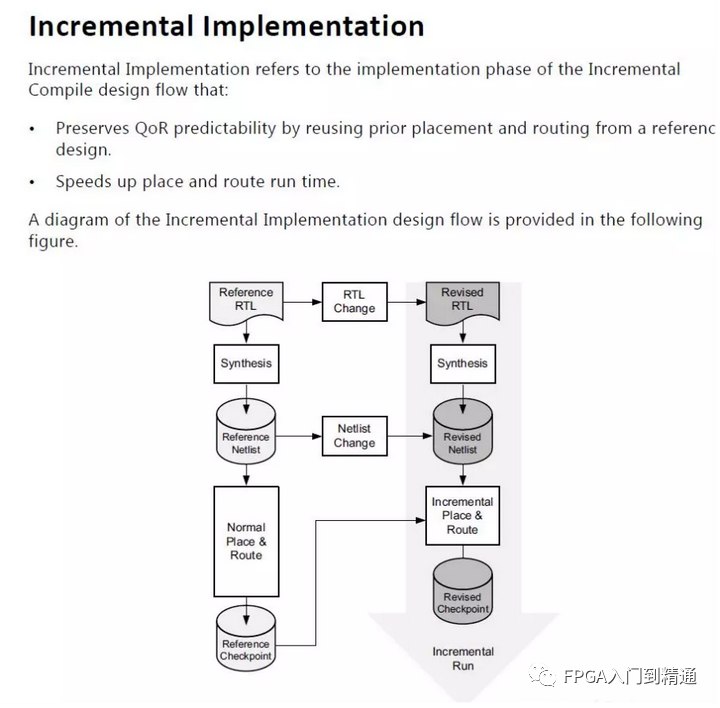

当RTL代码修改较少时,使用增量编译功能可以提高工程的编译速度,Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

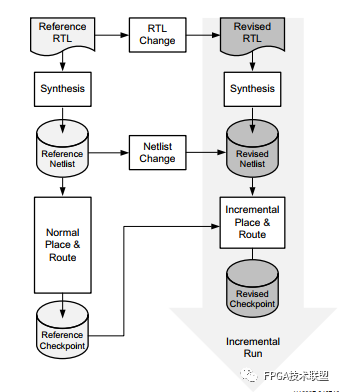

增量编译的流程如下:

增量编译是以已经编译和布局布线后的DCP文件为基础,当我们需要做微小的改动是,便可以使用增量编译来实现。这里微小改动主要包括有:

RTL代码的微小修改

网表的微小修改,比如增加或者改变ILA

需要注意的是:这里微小的改懂是指与当前设计相比变化非常小,其相似度大于95%时,增量编译的效果最好。而相似度小于75时,工具的增量编译就失效了。有时候一些全局变量修改,网表的改动是非常大的,总线位宽的变化,网表的改动也非常大。

增量编译设置:

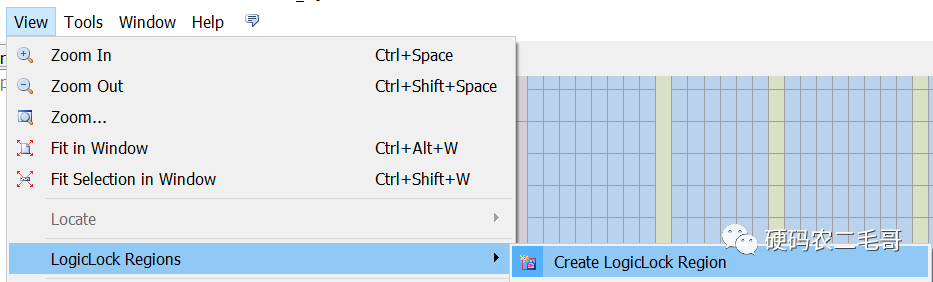

在项目模式下:在Vivado里面,使能IncrementalCompile的方式非常简单,在Impl run上右键选择“Set Incremental Compile…”,然后设置相应的参考dcp文件即可。

在非项目模式下:

在 opt_design 后运行以下命令:

%read_checkpoint -incremental reference_routed.dcp

-

RTL

+关注

关注

1文章

385浏览量

59759 -

编辑器

+关注

关注

1文章

805浏览量

31162

原文标题:增量编译(Incremental Compile)提高Vivado编译效率

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

谁能缩短大容量FPGA的编译时间?增量式编译QIC!

Vivado中的Incremental Compile增量编译技术详解

Vivado Design Suite 2015.3新增量编译功能介绍

Vivadoz中增量编译与设计锁定

Vivado里如何手动调整编译顺序

Vivado增量编译的基本概念、优点、使用方法以及注意事项

浅谈Vivado编译时间

每次Vivado编译的结果都一样吗

讲述增量编译方法,提高Vivado编译效率

讲述增量编译方法,提高Vivado编译效率

评论