当面对一个项目计划时,你最后一次听到“需要多长时间就花多长时间”或者“如果第一次不成功,不要担心,你总能搞定的”这些话大概是什么时候的事?很可能从来就没有过。随着FPGA变得越来越强大,处理的任务范围也越来越广,缩短设计周期并且最小化风险变得前所未有的重要。

Pentek公司作为一家商用现货(COTS)FPGA的数据处理和采集产品制造商,通常是FPGA技术与最终用户应用之间的接口。这使得Pentek处于支持客户作为工程合作伙伴的独特位置,其最终共同目标是解决他们的最终需求。 Pentek已经学到了很多关于如何缩短设计周期和最小化客户风险的知识。 以下是Pentek及其客户发现的有价值的一系列策略。

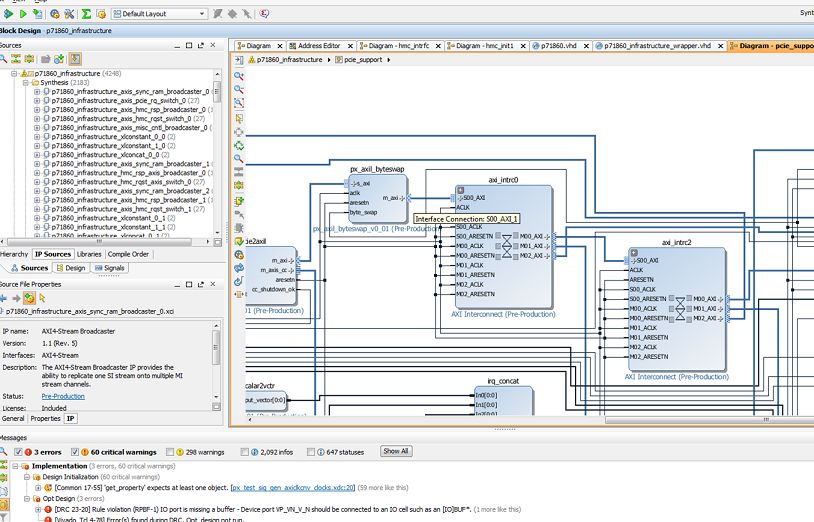

1. 利用FPGA设计工具Pentek公司推出的每一款基于FPGA的产品交付时都附带一整套功能包,作为IP来进行安装。尽管这些产品可以直接用来实现数据采集和处理的解决方案,但是大多数用户都会安装自己自定义的IP来进行特定应用的处理。Pentek公司推出的FPGA设计工具集搭配Zynq UltraScale+ RFSoC会提供所有生产用的IP以及一些通用功能的IP库,用户在搭建自己设计时可以用到。这些IP集成模块可以轻松的导入Xilinx Vivado设计工具,所有IP都支持AXI4协议并且可以无缝对接Xilinx提供的IP资源。这可以让我们快速访问整个设计,不用再去学习新的工具或者了解IP设计定义,从而节省了项目启动时间。

图1:利用Xilinx和Pentek向导模块组合开展的FPGA设计

2. 使用厂家提供的IP功能虽然每个用户的设计都是不同的,但是所需的许多功能都是相似的,每一款硬件产品所提供的IP不仅支持硬件特性,比如A/D转换板卡的数据采集或者D/A转换板卡的波形发生器,而且还支持一些比较常见的高级功能,原本这些功能可能是由硬件来处理的。Pentek公司推出的基于Zynq UltraScale+ RFSoCs的产品支持以下功能库:• 数据采集用于抓取和传输A/D数据• 波形生成,将数据传输给D/A或者读取存储在内存中的波形数据• 用于雷达测试应用的雷达啁啾声和信号发生器• A/D校正功能• 100GigE UDP引擎• DMA引擎用于高速数据流设计

在每种情况下用户都可以通过编辑提供的VHDL源代码来使用这些IP功能,在所有情况下从竞争的角度来看经过测试的IP加速了产品开发并且降低了风险。

3. 简化从开发到部署的流程Pentek公司推出的Quartz系列采用的是Zynq UltraScale+ RFSoCs,而且都是基于QuartzXM,它是一款紧凑的模块系统,包括了Zynq UltraScale+ RFSoC所需的所有电路设计。

图2:Model 6001 QuartzXM RFSoC模块化系统

这个设计背后的想法很简单:解决模块电路设计和PCB方面面临的最大挑战,并且保证Zynq UltraScale+ RFSoC最佳的vwin 和数字性能。当这款模块设计完成并且经过验证,Pentek公司可以扩展为各种接口形式的模块,比如PCIe和3U VPX。

图3:Model 5950,3U VPX RFSoC模块板卡(拆下盖子显示的是QuartzXM)

虽然以标准的形式提供这种设计非常重要,但是用户所能看到的最大好处是可以在有限的空间或者不满足标准形式应用部署Zynq UltraScale+ RFSoC。Pentek公司提供的工具集包含所需的电气、机械和散热设计指导,让客户能够为QuartzXM设计自己的承载板卡。将如此多的功能封装在QuartzXM模块中,用户可以从一款经过验证的Zynq UltraScale+ RFSoC平台开始,专注于更简单的承载板卡设计。此外它还提供了一套标准的、低成本的、易于操作的原型开发流程,用户可以根据自己情况选择PCIe接口的Quartz模块,或者使用3U VPX形式的模块,还提供低成本的Model 8257开发模块共用户选择。开发好应用程序IP和软件之后,在需要时可以通过设计定制的载板将解决方案部署到系统中,因为这两个系统的硬件核心是相同的,所有IP和软件可以在不做任何更改的情况下从开发移植到部署系统中,所以这些设计技术都大大降低了风险,缩短了开发时间。

4. 提供工程师对工程师的支持方式,确保产品的成功即使提供最好的产品文档也抵不上工程师对工程师的对话交流,这对于设计的整个周期可以最小化风险同时节省时间。Pentek公司推出的所有产品都提供免费的终身技术支持服务,如果出现问题客户可以随时联系到Pentek公司的工程师。

设计周期时间和降低风险是整个项目过程中非常真实重要的一部分,尽管风险永远是开发创新过程中固有的一部分,Pentek公司的态度是认为降低风险缩短设计周期与为客户提供最高性能和创新产品是同等重要的事情。

-

FPGA

+关注

关注

1628文章

21728浏览量

602946 -

Xilinx

+关注

关注

71文章

2166浏览量

121286 -

Zynq-7000

+关注

关注

3文章

144浏览量

36821

原文标题:借助Zynq UltraScale+ RFSoCs缩短设计周期同时最小化风险

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SOLIDWORKS二次开发参数化设计工具 慧德敏学

晶圆制造生产周期时间的概念及意义

安森美系统设计工具介绍

利用FPGA设计工具减少设计周期时间和降低风险

利用FPGA设计工具减少设计周期时间和降低风险

评论