在智能机性能越来越强悍的今天,最核心的处理器就变得尤为重要。其实从上世纪70年代起,处理器发展的速度就没有停下来过,从最初的180nm工艺到现在的14nm、7nm工艺,可以说制作工艺的进步带给了CPU更多进化的可能。

然而到了7nm以后,很多在 1Xnm大放异彩的半导体公司都在7nm制程处遭遇到了苦头,AMD御用代工厂商GF宣布无限期延期7nm制程工艺,英特尔的10nm制程更是跳票到2019年。目前仅剩下的7nm工艺也只有台积电能够在现阶段实现量产。今天与非网小编就来与大家探讨一些关于7nm工艺制程的问题。

也许有的看官还云里雾里,等会儿,先告诉我这个XX nm到底是啥意思?别急,下面就来说了。

XX nm制造工艺是什么概念?芯片的制造工艺常常用90nm、65nm、40nm、28nm、22nm、14nm来表示。现在的CPU内集成了以亿为单位的晶体管,这种晶体管由源极、漏极和位于他们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流通断的作用。

所谓的XX nm其实指的是,CPU上形成的互补氧化物金属半导体场效应晶体管栅极的宽度,也被称为栅长。

栅长越短,则可以在相同尺寸的硅片上集成更多的晶体管——Intel曾经宣称将栅长从130nm减小到90nm时,晶体管所占面积将减小一半;在芯片晶体管集成度相当的情况下,使用更先进的制造工艺,芯片的面积和功耗就越小,成本也越低。

栅长可以分为光刻栅长和实际栅长,其中光刻栅长是由光刻技术所决定的。

由于在光刻中光存在衍射现象以及芯片制造中还要经历离子注入、蚀刻、等离子冲洗、热处理等步骤,因此会导致光刻栅长和实际栅长不一致的情况。

另外,同样的制程工艺下,实际栅长也会不一样,比如虽然三星也推出了14nm制程工艺的芯片,但其芯片的实际栅长和Intel的14nm制程芯片的实际栅长依然有一定差距。

实现7nm制程工艺为什么这么困难?在讨论7nm制程难度的时候,我们需要普及一个量子力学上的概念,这样子可以有助于我们理解为什么低制程的成本急剧提升,那就是量子隧穿效应。

在量子力学里,量子隧穿效应指的是,像电子等微观粒子能够穿入或穿越位势垒的量子行为,尽管位势垒的高度大于粒子的总能量。在经典力学里,这是不可能发生的,但使用量子力学理论却可以给出合理解释。

如果通俗点来讲,就是说制程工艺到一定程度下,电路与电路之间的距离降低到一定程度就会出现量子隧穿效应,这些电子呈现的是一种我们所不知道的规律进行运动,于是这些不可控制的电子造成了半导体的漏电率急剧上升,有太多的能源被浪费在控制电子运动上,自然不能发挥晶体管应该有的性能,宏观上表现为处理器的发热量增加,但是性能没有太大的变化。

然后我们再来讨论一下现阶段有哪些存在的问题:

首先从本质上来说,7nm已经是物理极限。缩短晶体管栅极的长度可以使CPU集成更多的晶体管或者有效减少晶体管的面积和功耗,并削减CPU的硅片成本。

正是因此,CPU生产厂商不遗余力地减小晶体管栅极宽度,以提高在单位面积上所集成的晶体管数量。

不过这种做法也会使电子移动的距离缩短,容易导致晶体管内部电子自发通过晶体管通道的硅底板进行的从负极流向正极的运动,也就是漏电。而且随着芯片中晶体管数量增加,原本仅数个原子层厚的二氧化硅绝缘层会变得更薄进而导致泄漏更多电子,随后泄漏的电流又增加了芯片额外的功耗。

其次,工艺的精度已经趋近于传统***的极限,极紫外***还无法用于大规模量产。传统***的波长为193nm,通过浸液的方式可以使波长进一步缩短,再加上多次曝光的辅助,已经走到了14nm。可是到了7nm,这种方法光刻出来的线条误差越来越大,越来越难以控制。我们可以通过下图对比传统***和极紫外***的实际效果图,可以看出,传统光刻的方法误差确实很大。这种情况下,想要良率满足要求是极为困难的。

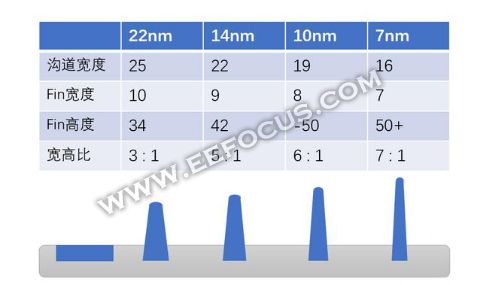

线宽逼近极限带来的电阻电容增大变得不可忽视,我们知道同样材质的前提下,越细的导线电阻越大。因此当工艺进入7nm,线上电阻已经变得非常大,Intel不得已采用贵技术钌来解决这个问题。除此之外,由于FinFET的Fin越来越小,控制其流过的电流也越来越困难。因此,不得已采用了增加Fin的高度来增强控制,可是这样又带来晶体管的电容更大从而速度变慢。下图展示了不同工艺的晶体管的各种参数,可以看出随这工艺升级,Fin的宽高比越来越大。

EDA工具支持的支持尚不完善,虽然每代工艺都会遇到此类问题,但是14nm/7nm工艺恰逢EDA工具尤其是后端设计工具更新换代,两个主流软件厂商均发布了所谓的次世代EDA工具。各种引擎的升级导致工具的bug数直线上升,而工艺带来的的挑战需要工具不断升级并增加性的功能,助长了工具开发和使用方面的挑战。

设计上的难度大幅增加,各个芯片设计公司希望通过工艺升级获得更高的性能,更低的功耗和更小的芯片面积。可是7nm在设计方面提出了更高的挑战。为了满足工艺厂商的生产规则,在设计阶段增加了大量的硬性规则,给芯片设计尤其是后端设计增加的很大难度。比如使用金属层上,对于底层金属,几乎是只能按照特定的pattern和方向使用,变通性大大降低。

7nm擂台,参与者仅剩三家

目前还在追求7nm制程工艺的厂商仅剩台积电,英特尔以及三星三家厂商。芯片代工讲究的是规模效应,前期投入的资金需要通过大量的芯片来平摊巨额的研发成本,同时芯片代工行业也是一个商业行为,企业追求是利润,如果没有利润,赔本的买卖相信大家都不愿意长期干下去。

在这个赢者通吃的行业中,像台积电凭借着率先实现的7nm工艺获得了大量的订单,而AMD也已经宣布未来的Zen 2和Navi显卡将会让台积电进行代工,海量的订单满足了台积电的7nm胃口,自然可以分摊巨额研发费用,同时还能赚取大量的利润进行更进一步的制程工艺中来,这种良性循环也让台积电的财报节节攀升。

作为拥有完整IC设计的三星和英特尔自然拥有大量的芯片需求来满足自己的芯片代工行业。即使没有代工,他们同样可以自主满足7nm工艺制程的产能。

而其他的芯片代工企业恐怕就过得不那么舒服了,例如格罗方德先进制程制造公司,没有了AMD最新的Zen 2以及Navi显卡的订单,自然推广7nm制程的动力就小了很多。没有订单也没有利润,导致没有足够的研发资金投入到先进制程工艺的研发中去。这样周而复始,自然也就退出了芯片行业的竞争中来。而整个芯片行业也伴随着门槛的提升处于寡头化的情形,除非有黑科技大幅降低先进制程的制造成本,玩得转现在和未来芯片代工的最终还是那几个科技巨头。

三大巨头的7nm制程现状

据悉,台积电预计将在2019年3月底开始量产7nmEUV工艺,EUV全称Extreme Ultraviolet Lithography,也就是极紫外光刻。此举将推动台积电的7nm芯片总销量占比提升至25%。同时消息人士指出,台积电有望在2019年第二季度开始5nm风险试产,值得一提的是,5nm的整个代际都将基于EUV工艺部署。台积电首席执行官CC Wei此前也透露,预计将在2019年上半年流片5nm,并在2020年上半年量产。

为与台积电一较高下,三星 7nm 不走寻常套路,也就是像台积电所选择的作法,使用 DUV机台,但通过多重曝光的方式搞定,后期再导入 EUV 机台来降低成本并提高性能。三星一开始就会导入 EUV ,目标是把 7nm工艺的成本控制一步到位,创造更好的市场诱因。

然而 EUV 机台的调整难度极高,三星虽然前些时候宣布有所突破,但2018年主要还是试产,自家 7nm Exynos 方案虽有机会在 2018 年底提早量产,但因为预期良率低,肯定还是满足不了自家手机的需求,因此还是有一大部分的芯片必须求助高通,而高通此时与苹果几乎同时抢进台积电的产能,相较于三星的窘迫,凭借台积电的优秀良率与产能布局,对三星和其他客户的需求也就更能从容应付。

根据三星高管所说,他们在2019年下半年会量产7nm EUV工艺,2021年则会量产更先进的3nm GAA工艺。

而牙膏厂英特尔,目前10nm工艺还没量产,要到今年底才能首先出货移动版10nm冰湖处理器,2020年才有可能大规模量产桌面版、服务器版,但是下下代7nm EUV工艺会吸取10nm工艺上的教训,不会盲目追求高指标,量产进度会比10nm更顺利(希望如此),而工厂建设、设备安装调试需要两三年的时间,英特尔的7nm EUV工艺量产要到2021-2022年才有可能了。

目前在制造工艺上,中国与世界先进工艺节点依然存在较大差距。对于现在的中国半导体产业而言,是花费巨大人力物力财力去探索突破7nm物理极限,还是将现有工艺实现量产是值得郑重考虑的问题。在与非网小编看来,相对于耗费大量资源去研发新材料突破7nm物理极限,还不如脚踏实地地解决现实问题。

-

cpu

+关注

关注

68文章

10854浏览量

211567 -

晶体管

+关注

关注

77文章

9682浏览量

138073 -

制程工艺

+关注

关注

0文章

43浏览量

9434

原文标题:在7nm以后的世界,谁在尽头等你?

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

XX nm制造工艺是什么概念?实现7nm制程工艺为什么这么困难?

XX nm制造工艺是什么概念?实现7nm制程工艺为什么这么困难?

评论