简介

直接数字合成(DDS)技术正在迅速发展,但直接合成UHF和微波输出频率尚不实用或经济上可行。目前最先进的商用DDS IC(如300 MHz AD9852单通道和AD9854正交完整DDS芯片)可为低VHF频谱提供可用输出,约为120 MHz。 DDS和输出DAC的采样速度限制构成了主要瓶颈;基本DDS输出信号不得大于采样频率的一半。 ADI公司的下一代高速DDS IC将以900 MHz采样率和360 MHz可用基波输出来挑战这些限制。

为了利用UHF和微波频率的DDS属性,DDS通常与锁相环(PLL)集成或在混频器中上变频。不幸的是,使用PLL的乘法会影响信号完整性,频率分辨率和灵活性。此外,使用混频器将DSB(双边带)信号上变频到更高频率的单边带可能需要困难或不可能的输出滤波以及高质量的固定频率本地振荡器(LO)。用于克服这些缺点的方法通常需要多个PLL或混频器/滤波器/振荡器级。

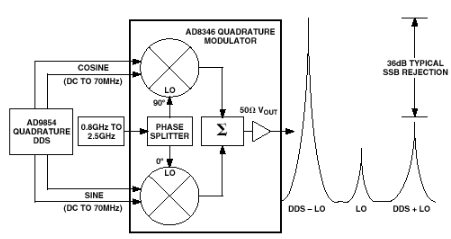

以下是单级上升的改进且经济的方法使用上述AD9854正交完整DDS和新器件AD8346正交调制器将频率转换为800至2500 MHz的频率,相位精度在1度以内,幅度平衡在1900年内在0.2 dB以内兆赫。上变频抑制载波单边带信号在整个频率范围内显示> 36 dB典型的LO抑制和不需要的边带频率。此外,所有 DDS信号质量得以保留,而不需要的上变频产品则被最小化。对于许多应用来说,36 dB抑制就足够了,这种4000倍的无用信号功率抑制将大大降低输出滤波器的复杂性,或者提高在要求更高的应用中进行有效滤波的可行性。

要在上边带和下边带之间进行选择,只需在AD8346调制器输入引脚上反转或交换正交DDS信号,I代表Q,Q代表I。 AD9854 DDS具有多种调制模式(AM,FM,PSK和FSK)。除灵活的单频信号外,还通过提供数字和vwin 通信功能,增强了该应用的实用性。

正交DDS信号的上变频只是AD8346正交调制器可以实现的一个例子。事实上,它可以上转换任何正交模拟基带信号(直流到70 MHz),具有类似的边带抑制。

正交SSB上变频

AD8346正交调制器提供令人印象深刻的SSB上变频性能,允许基带信号直接调制800 MHz至2.5 GHz的本地振荡器(LO)频率,通常36 dB抑制冗余边带和LO频率。上变频信号可以是跳频,扩频或静止的;在允许的输入带宽内未调制或宽带调制。对于上变频由DDS合成的正交信号,图1中的框图显示了AD9854输出信号如何应用于AD8346差分“基带调制”输入,以便在LO频率附近进行SSB上变频。

在正交上变频中,两个混频器由正弦和余弦LO驱动,这些LO内部源自用户提供的单端高质量振荡器。混频器输入正弦和余弦基带信号(滤波后的DDS输出信号),以便在固定LO周围对称地进行上变频。两个混频器输出在内部相加,以添加同相分量并抑制混频器输出的正交分量。最终结果(无需额外滤波)是抑制载波,单边带,-10dBm和50欧姆阻抗的电压输出,其频率可以是LO和基带信号的和或差,加上抑制的残余LO和相反的边带。

正交调制需要精确的相位关系,这不是一个新概念。五十年前,正交调制的首要用途之一是产生单边带无线电话信号;它被称为“阶段化方法”。然而,“滤波器方法”变得优选,因为用模拟方法不能容易地在可观的带宽上保持正交相位关系。这两种方法主要用于低IF频率,目的是消除冗余边带并消除“载波”。

AD9854 DDS产生数字精确正交输出信号(典型值)精度为十分之一(十度),从直流到> 120 MHz,使用300 MHz时钟源。在图1所示的示例中,如果适当地分频,则可以从高质量LO导出时钟。 AD8346的正交相位误差在800至2500 MHz输出范围内通常为1度。这些器件包含一个“芯片组”,可以很好地用于许多宽带数字和模拟通信方案,从扩频到电视。

一个更完整的解释,包括模拟和数字正交调制和SSB上转换的基本数学分析,可以在Doug Smith撰写的文章“信号,样品和材料:DSP教程(第1部分)”中找到。 1998年3月/ 4月,发行 QEX:通信实验论坛杂志。欲了解更多信息,请联系美国无线电中继联盟,225 Main Street,Newington,CT 06111,http://www.arrl.org/qex.

要更好地了解正交上转换的优点,比较两种常用的产生UHF和微波DDS信号的方法可能是有益的: DDS / PLL倍频和单级混频器上变频。

PLL / DDS乘法

DDS信号到UHF和微波频率的PLL倍增很容易且经济地完成,但是要付出代价:DDS提供的优势几乎会在所有理想的属性中降低,包括相位噪声规范,新频率采集时间,频率分辨率和无杂散动态范围(SFDR)。确实存在降低信号劣化的PLL / DDS /混频器/滤波器的组合,但是这种多级实现的复杂性和成本可能是不可容忍的。图2显示了典型的DDS / PLL实现。

PLL输出相位噪声是一种明显且容易观察到的现象;它的放大倍数会降低性能,与PLL的倍增系数成比例(以dB表示,20 log F out / F in )。例如,如果将10 MHz处的DDS信号的频率乘以100以从PLL产生1 GHz的输出,则PLL环路带宽内的输出相位噪声将比原始输入信号大约40 dB。此外,PLL环路带宽内的杂散信号或“杂散”将增加相同的量。这可能导致不可接受的杂散电平比DDS输入信号高出40dB

频谱图很容易显示DDS信号的相位噪声在乘以后会受到多大影响图2中的PLL电路为×64。图3显示了14 MHz时PLL的DDS输入信号,图4显示了896 MHz的PLL倍频DDS信号。宽噪声“裙边”是降级相位噪声的标志。

为了说明PLL倍增对杂散电平的影响,调制DDS信号以产生丰富的低水平的马刺接近基础。图5显示了馈入PLL的调制DDS信号,而图6显示了PLL的30 kHz环路带宽内的这些杂散如何被放大。请注意,距离载波> 60 kHz,杂散幅度不受影响。相位噪声没有改变,也没有任何其他参数被改变。

除了相位噪声,定时抖动和杂散电平降级之外,许多其他所需的DDS属性,包括频率捷变和分辨率,都会受到PLL倍频的不利影响。即使频率分辨率也会比DDS分辨率差N倍,新频率采集将受到PLL建立时间的限制(可能比DDS高出10,000倍)。

DDS /混频器上变频

设计人员可以选择的更好的选择是使用混频器将DDS信号上变频到UHF /微波频率。上变频不会显着增加杂散电平或相位噪声。此外,频率捷变和分辨率不受影响。要克服的最大障碍是存在双边带(DSB)输出:LO + DDS和LO - DDS,以及发生的任何LO馈通。

图7,显示200抑制载波(LO)的频谱区域,单上变频混频器输出,证明了上转换的这个问题。两个边带相距50 MHz,LO馈通在两者之间的中间频率为1.04 GHz。这种50 MHz的扩展仅为1 GHz输出频率的5%。过滤信号以去除不需要的边带和LO馈通将非常困难。如果输出频率增加到2 GHz,则可能使事情变得复杂到过滤不切实际的程度。为了克服这个问题,设计人员传统上采用混合和滤波的多个阶段来产生DSB信号,在UHF /微波处具有更大的边带间距,这将更容易过滤,但成本和复杂性要高得多。

DDS上变频实验室结果

在实验室中使用AD9854和AD8346的评估板完成了SSB上变频器的正交实现。需要对AD8346评估板进行修改,以接受AD9854评估板提供的滤波,正交,单端信号。还需要增加输出电压电平,以满足AD8346的输入要求。图8中显示了实验室连接和修改的示意图。修改如下:

添加两个1:16中心抽头阻抗升压变压器(小型电路T16) -6T)将单端正交信号转换为差分信号,并提供1:4的升压电压。使用中心抽头的次级允许将1.2 V的直流偏移电压添加到差分信号,以符合AD8346的输入偏置要求。

在每个变压器输出端添加1000欧姆的终端电阻。

添加一个1.2伏直流偏置源,由两个硅二极管组成,这些二极管通过一个2000欧姆的限流电阻从3.3伏电源电压正向偏置。连接到I和Q通道变压器次级绕组的中心抽头。

此设置的测试验证了正交输入时AD8346数据手册中的性能预期来自AD9854的信号经过适当调整,以补偿正交相位误差和I& Q幅度不平衡。见图9和图10。

I& D中的错误。在信号退出AD9854 IC之后,通过滤波器,不相等的电缆和PCB走线长度,变压器差异等引入了Q正交相位关系 - 。系统相位误差无法通过编程更改来纠正AD9854。其输出以精确的正交固定。通过调整AD9854至AD8346评估板的电缆长度,可以纠正相位误差。使用AD9854的12位独立正弦和余弦(I& Q)数字幅度乘法器级可以校正幅度不等式。

图9显示了以1.05 GHz为中心的AD8346输出频谱的200 MHz段。 DDS“调制”上边带和下边带信号在LO的任一侧在1.04 GHz处看到25 MHz。在抑制的上边带(USB)和有利的下边带(LSB)幅度之间指示-40dB的差异。 40 dB差分相当于功率比约为1万比1。这种边带抑制水平表示大约1度的输入信号相位失配。

1.015 GHz下边带(LSB)的近视图(图10)表现出色信号完整性。它与图4中的PLL倍增信号进行了惊人的比较。如前所述,可以交换正交调制器的正弦和余弦DDS信号,使互补边带更受青睐。

LO馈通幅度(-36 dB)大于此设置中的抑制边带。 LO馈通电平不受DDS I和D的相位或幅度的影响。 Q输入信号。为了降低LO馈通的重要性,I&的电压电平降低。每个差分输入引脚的Q输入信号应最大化(1V p-p)。

结论

正交调制是DDS上转换为UHF和微波频率的完善且经济的方法,不会丢失DDS技术的任何理想属性或损害信号质量。 AD8346正交调制器简化了工艺。这是与AD9854 DDS的“自然”匹配,具有差分正交输出。拥有高品质的LO,UHF&微波SSB输出很容易实现。

AD9854具有多种调制模式,该应用支持微波输出频率的(几乎)完整的AM,FM,PSK,FSK激励器。利用AM抑制载波I&的少量附加信号处理。 Q DDS输出,SSB语音或其他幅度调制方案成为可能。图11显示了IC如何与外部调制源和控制器件互连以执行通信功能。

36 dB(典型值)边带和LO拒绝直接可用于许多应用程序,在要求更高的应用程序中,输出过滤成为一项不那么艰巨的任务。适当调整DDS I& Q信号相位关系和幅度平衡可以进一步增加边带抑制。

虽然它专门设计用于提供适当的输出信号而无需多个DDS来实现此功能,但此处描述的应用中的AD9854并不是组合DDS和正交调制的唯一方法。其他DDS IC,如AD9850,AD9851和AD983x系列,也可用于正交对。如果两个DDS可以同步,则很可能可以使用内部相位偏移电路对它们进行编程以实现正交输出。有关DDS和数字调制器产品的完整列表,以及访问技术说明和数据表,请参阅DDS产品。值得注意的是,AD9854的独立可编程I& Q输出幅度使输出匹配成为一个简单的软件程序。

正交DDS SSB上变频到2GHz以上的相对简单和经济性应该鼓励读者考虑将这种技术添加到他们的曲目中。它保留了微波频率下所有理想的DDS属性,同时大大减少了传统双边带混频器上变频的不良冗余边带。

-

pll

+关注

关注

6文章

776浏览量

135130 -

DDS

+关注

关注

21文章

633浏览量

152630 -

调制器

+关注

关注

3文章

840浏览量

45142

发布评论请先 登录

相关推荐

基于数字上变频器的中频调制器

有关AD9361的上变频

PXI 5610实现上变频信号发送

AD9739上变频功能实现原理是什么?

数字正交上变频器AD9857

基于QDUC的雷达上变频电路的设计

AN-0996: 在点对点微波发射系统中使用正交数字上变频器(QDUC)的优势

正交DDS信号至800至2500MHz频段的单边带上变频

正交DDS信号的上变频基波输出挑战

正交DDS信号的上变频基波输出挑战

评论