说起来,ESP32跟RISC-V这两者对于现在的工程师来说都不陌生,不过这两者搞到一起还是挺让人意外的,但仔细想想又在情理之中。怎么说呢,ESP32可以说是目前全球做创客、做DIY的爱好者最受欢迎的无线通信模块之一,一是因为兼具WiFi/BT功能,其次是价格比较实惠;而RISC-V也是近两年来最受欢迎、最火热的微控制器架构之一,脱胎于精简指令集,又免费开源,这两者的结合也算是水到渠成吧。

有谁还记得2017年推出的HiFive1开发板?就是那个差一点赶上意法半导体STM32F7性能、基于全球第一款采用RISC-V架构的商用SoC Freedom E310-G000(下面都简称FE310)的开发板,由SiFive公司(这个公司也是RISC-V架构指令集的发明者创办的)推出的,而本文即将介绍的这个公司的HiFive1升级版——HiFive1 Rev B,结合ESP32与RISC-V的一款开发板。

HiFive1 Rev B与HiFive1的区别

乍一看的话会发现HiFive1 Rev B与HiFive1最大的区别就是增加了一个ESP32模块,仅仅如此吗?当然不是。

下图是HiFive1,也可以称作1代。开发板上的改变主要如下表所示:

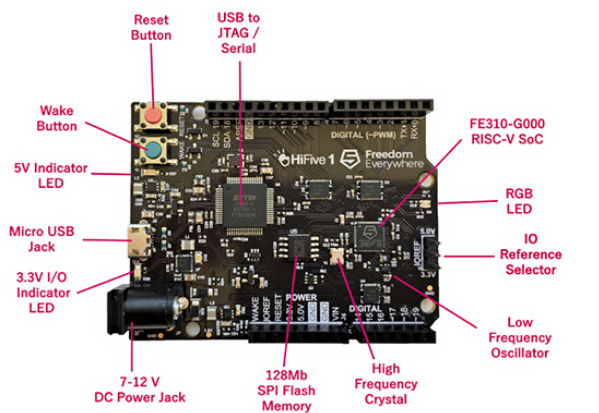

下图是升级版本HiFive1 Rev B。

开发板上的改变主要如下表所示:

核心SoC的升级

开发板搭载的SoC从1代的FE310-G000升级到HiFive1 Rev B版本上的FE310-G002。

这个升级的改进还是显而易见的,FE310-G002增加了对最新RISC-V调试规范0.13,硬件I²C,两个UART的支持,以及在低功耗睡眠模式下对核心轨进行电源门控。与原版FE310一样,FE310-G002采用SiFive的E31 Coreplex处理器,高性能,32位RV32IMAC内核,16KB L1指令缓存,1 KB数据SRAM寄存器和硬件乘法/除法。

FE310运行速度达320+MHz,是市场上速度最快的微控制器之一。

更多外围设备

凭借第二代版本,FE310芯片现在具有内置硬件I²C外设和额外的UART(共两个),这为连接各种第三方传感器,外设模块等其他设备打开了大门。此外,USB调试接口也已升级为Segger J-Link,支持拖放代码下载。

低功耗睡眠模式

FE310-G002具有一个由3.3V供电的常开(AON)电源域。由AON控制,CPU内核电源轨(1.8V)可以在睡眠模式下关闭,并在检测到唤醒事件时打开。

无线连接的加入

HiFive1 Rev B板具有Wi-Fi和蓝牙功能,这要归功于单核ESP32协处理器,它作为FE310-G002处理器的无线调制解调器。

板载存储的改变

值得商酌的是,原本16MB的QSPI NOR Flash变成了4M。虽然说初代的16MB空间过大,即便是换成了4MB,代码的存储空间还是绰绰有余,但是改小总是让人心怀芥蒂,这不是产品,这是开发平台,意味着有很多无限的可能去折腾,总要给用户留有冗余的性能或功能,这样折腾起来才够劲够味道。

One more thing:开源RTL

FE310作为第一款开源的商用RISC-V SoC,SiFive已将FE310 RTL代码贡献给开源社区。现在,我们可以完全看到芯片内部的结构,了解硬件的工作原理,RTL代码让企业或者工程师在FE310的基础上定制自己的SoC,此项措施无疑是SiFive希望鼓励全球企业或者工程师在RISC-V上运行自己开发的软件或者基于RISC-V的新硬件的开源开发。

- 处理器

+关注

关注

68文章

18797浏览量

226341 - 无线通信

+关注

关注

57文章

4386浏览量

143032 - RISC-V

+关注

关注

43文章

2099浏览量

45594

原文标题:ESP32与RISC-V结合——全新升级版本HiFive1 Rev B开发板

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

美高森美和SiFive推出HiFiveUnleashed扩展板 助力Linux软件和固件开发人员首次构建RISC-V PC

ST7MC2revA和B之间的区别是什么?

全球首款基于 RISC-V “HiFiveUnleashed” 单板计算机(SBC)

【沁恒微CH32V307评估板试用体验】探索Rust编程语言的嵌入式开发——基于CH32V307【1】

LMK_Guitar_base_Board_Rev.B_V1R3_B型底板原理图

什么是HiFive1?详细介绍HiFive1开发套件的核心

如何通过HiFive1套件实现快速原型开发

QB-RL78I1BIn-Circuit Emulator 用户手册Rev.1.00

QB-RL78I1BIn-Circuit Emulator 用户手册Rev.1.00

ISO-DONGLE1ZRev.B通信加密狗的硬件布局手册

L-484(Rev.1(Rev.1))软件许可协议

HiFive1 Rev B与HiFive1的区别

HiFive1 Rev B与HiFive1的区别

评论