4月登场的「超大型积体电路国际研讨会」(VLSI-TSA/DAT)是全球半导体产业年度盛事,首场专题演讲邀请到美国IBM华生研究中心研究员沙希迪(Ghavam Shahidi)以「功耗改善减缓,摩尔定律是否已走到尽头?」为题,谈半导体最新制程面临功率改善放缓的问题,并提出建议的解决之道。

1965年提出的摩尔定律(Moore's Law)引领半导体发展超过半世纪,是指芯片上可容纳的电晶体数目,约每隔18个月便会增加一倍,性能也将提升一倍,但近年的互补式金属氧化物半导体(CMOS)先进制程中,最新几代纳米节点的功耗改善程度,已出现明显的放缓,这不禁让人忧心,摩尔定律是否即将走到尽头?

制程推进唯功耗降低才能提高效能

半导体的主流制程CMOS,多年来每推进到一个新的纳米节点,最大的两个效益就是:面积可缩小30%、功耗明显改善。以后者来看,在特定频率下,芯片功耗的降低(每次操作的耗能)是一项重要指标,因为惟有芯片的整体耗能改善,才有机会提升芯片性能,例如:可在芯片的下一代设计中,内建更多核心或新增更多功能。

综观半导体纳米节点的历史数据,早期每一代的纳米制程进化,其功耗与上一代相较,改善的幅度都很大。以Sony游戏主机Playsation 2所采用的250纳米芯片为例,整体芯片的耗能为23瓦,演进了3个世代后,来到90纳米节点,功耗仅须0.5瓦,等于每一个纳米世代较前一代平均节能72%以上。

14纳米制程节能幅度大不如前

然而,在近年几个制程中,节能幅度大不如前。以英特尔的Core i7做为测试标的,第一代Core i7采45纳米制程,第二代Core i7采32纳米制程,两代之间仅实现了32%到50%的能耗下降。

接下来Core i7在2012年进入了22纳米制程,能耗只比32纳米下降了20%至27%。2014年,英特尔又陆续发表采用14纳米的Broadwell及Skylake(分别是第五、第六代的Core i7),结果它与前一代的22纳米相较,功耗仅下降0%至25% ,节能幅度创下最低纪录。直到2017年推出采14++纳米制程的Core i7芯片,节能幅度才增至20%到33%。

观察Core i7从45纳米到14纳米的节能数据可以看出,虽然每一代制程,芯片的面积愈缩愈小,但能够达到的能耗缩减幅度却愈来愈小,尤其在14纳米初期最为明显。近2年进入更先进的10纳米制程,也有类似状况,例如英特尔在2018年5月推出第一个采用10纳米制程的Core i3,其功耗表现跟14纳米制程类似:亦即并未看到功耗大幅降低。

挑战极限可考虑不同半导体架构

这个是否代表摩尔定律已逼近极限?如果芯片在每个新世代的制程无法达到明显的功耗下降,确实会导致芯片效能出现瓶颈,因为芯片能否置入更多核心,能否新增更多功能,都与能耗息息相关。

展望未来,若要改善功耗,关键之一在于必须将半导体元件的电容降低。我认为,不论是业界目前初迈入的7纳米,甚或是未来更先进的纳米制程,也要准备好3种不同架构的选项来改善功耗:一是继续采行鳍式场效电晶体(FinFET)架构,设法将FET的闸极高度降低。

FinFET架构虽蔚为主流,却因闸极底部不导电及闸极过高,造成寄生电容产生,若能解决此一问题,应可见到功耗的改善。二是转向纳米线(Nano-wires)或垂直式FET(Vertical FET)等3D架构,以降低寄生电容和电阻;三是将平面式(Planar)架构纳入考量,例如SOI(绝缘层上硅晶体)的原理是在硅晶体之间,加入绝缘体物质,可使寄生电容减少。

我想大家都很期待,在未来几个更先进的纳米制程,能回复到早期纳米节点功耗大幅降低的景况,这对下世代高效能微处理器来说尤其重要。

-

英特尔

+关注

关注

61文章

9949浏览量

171692 -

半导体

+关注

关注

334文章

27286浏览量

218067

原文标题:挑战摩尔定律极限,可考虑不同半导体架构

文章出处:【微信号:iawbs2016,微信公众号:宽禁带半导体技术创新联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

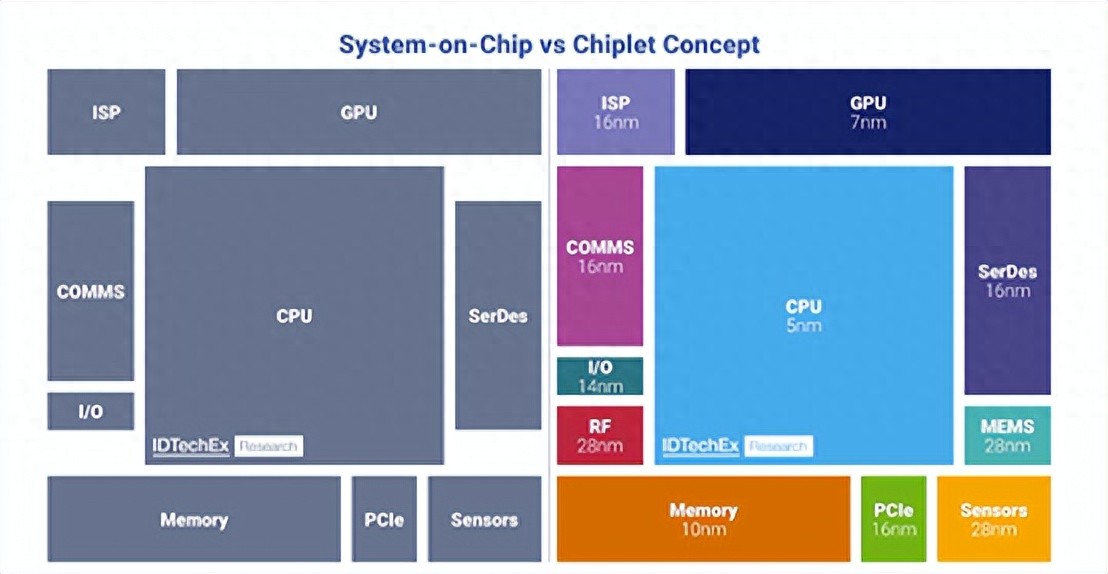

Chiplet或改变半导体设计和制造

Chiplet将彻底改变半导体设计和制造

国产半导体新希望:Chiplet技术助力“弯道超车”!

“自我实现的预言”摩尔定律,如何继续引领创新

半导体发展的四个时代

半导体发展的四个时代

AI在半导体设计和制造中的作用

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

挑战摩尔定律极限 可考虑不同半导体架构

挑战摩尔定律极限 可考虑不同半导体架构

评论