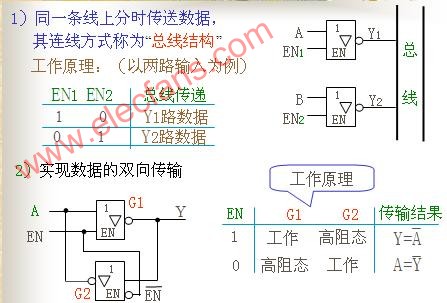

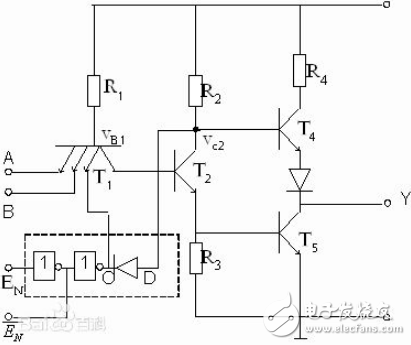

三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

总线

+关注

关注

10文章

2878浏览量

88051 -

三态门

+关注

关注

1文章

34浏览量

18815

发布评论请先 登录

相关推荐

什么是三态门和OC门?

三态门和OC门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑

发表于 05-26 13:01

【梦翼师兄今日分享】 三态门程序设计讲解

等,要求信号为三态类型,也就是我们所说的输入输出(inout)类型。那么,本节梦翼师兄将和大家一起来探讨三态门的用法。项目需求设计一个三态门电路,可以实现数据的输出和总线“挂起”。系统

发表于 12-12 16:11

三态门逻辑功能的Multisim仿真方案

介绍了用Multisim仿真软件分析三态门工作过程的方法,目的是探索三态门工作波形的仿真实验技术,即用Multisim仿真软件中的字组产生器产生三态

发表于 05-06 15:59

•0次下载

三态门如何在FPGA中实现与仿真

三态门在数字电路上可以说是应用的非常广泛,特别是一些总线上的应用,因而,随着数字电路的发展,就避免不了用硬件描述语言在FPGA上来设计实现三态门

发表于 02-08 11:37

•8210次阅读

三态门逻辑电路图大全(三款三态门逻辑电路图)

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态

发表于 03-01 14:03

•7.9w次阅读

FPGA之三态门

FPGA之三态门

评论