在Vivado Implementation阶段,有时是有必要分析一下什么原因导致运行时间(runtime)过长,从而找到一些方法来缩短运行时间。

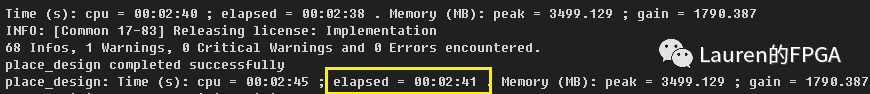

首先,要明确到底哪个阶段耗时过长。Vivado Implementation主要有三个子步骤:opt_design、place_design和route_design。Implementation结束后,会在"

可采用如下一些方法缩短运行时间。

Implementation Strategy

如果只是评估资源利用率,可使用Flow_Quick策略。该策略不是时序驱动的策略,因此可以快速执行Implementation。策略Flow_RuntimeOptimized是时序驱动的策略,可以快速完成Implementation,它是设计性能和运行时间之间一种折中。

检查约束

对于时序约束,我们要求“干净且合理”。所谓“干净”,是指约束完备,不会出现漏约或者约束被覆盖的情形。例如,由于set_clock_groups的优先级高于set_max_delay,这就有可能造成后者的约束被覆盖。所谓“合理”,是指约束的数值是正确的。这在多周期路径约束以及跨时钟域路径约束中会经常碰到,对于这类路径要格外注意。例如,如果多周期路径的hold requirement不是0,那么有可能就是约束不合理;如果跨时钟域路径的path requirement为1ns,这也是不合理的。

此外,在用Tcl命令时,尽可能地去缓存被复用的对象。例如,如果通过get_nets获得的一组nets在后续约束中被反复使用,那么可将get_nets的返回结果赋给一个变量,后续使用时只需调用该变量即可。同时,通过选项-filter找到更准确的对象,例如:对于时序路径,通过属性IS_SEQUENTIAL找到时序单元,从而避免了获得其他一些不期望的结果。

约束路径越具体越节省运行时间,例如:如果set_false_path只使用了-from选项,那么Vivado在搜索这些路径时就会比较耗时。

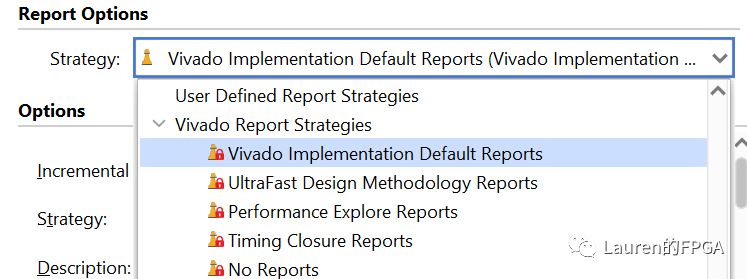

管理生成报告

生成报告也会消耗一些时间。Vivado提供了Report strategy,如下图所示。根据设计分析的需求选择生成报告可节省一定的运行时间。

布线

拥塞对运行时间有很大的影响。因此,如果设计出现了拥塞问题,就要把其作为首要问题去解决。同时,在route_design阶段,使用选项-ultrathreads也可缩短运行时间。

增量编译

如果设计只是有一小部分改动,那么可尝试增量Implementation。这在一定程度上也会缩短运行时间。

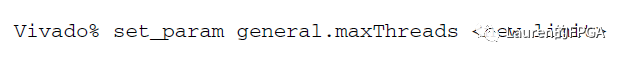

设置多线程

Vivado 2018.x的版本,无论是Synthesis还是Implementation,都可以支持多线程。只需要通过如下命令即可设置线程个数。对于Synthesis,最大线程数为4,对于Implementation,最大线程数为8。

ECO流程

对于微小的改动,例如修改ILA的Debug probes或者把内部net链接到某个Package Pin,都可以采用ECO流程,可以极大地缩短运行时间。ECO具体流程可看这里(替换Debug Probes其实很简单),文档ug904中也有详细介绍。

-

Vivado

+关注

关注

19文章

812浏览量

66470 -

时序驱动

+关注

关注

0文章

4浏览量

1497

原文标题:如何缩短Vivado运行时间

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

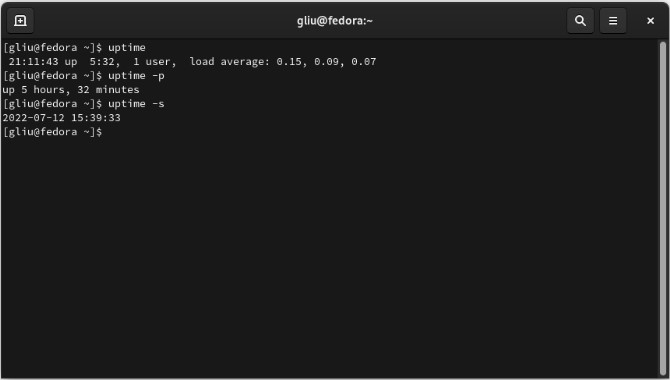

如何检查Linux服务器的运行时间

运行时错误Vivado 2016.2

freertos的任务运行时间怎么设置

电机运行时间进行排列 是分为两个部分来完成这个程序的设计的

如何高效测量ECU的运行时间

浅析STM32代码运行时间的技巧

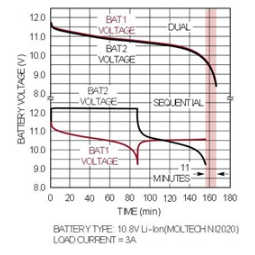

单片双电池电源管理器可延长运行时间并缩短充电时间

ch32v307记录程序运行时间

西门子SCL编程50台电机运行时间累计方法

如何缩短Vivado的运行时间

如何缩短Vivado的运行时间

评论