防止电路闩锁的建议

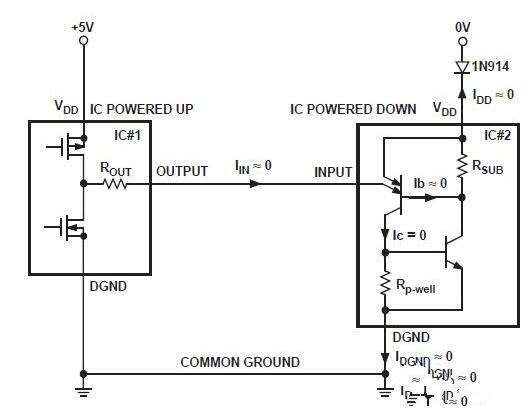

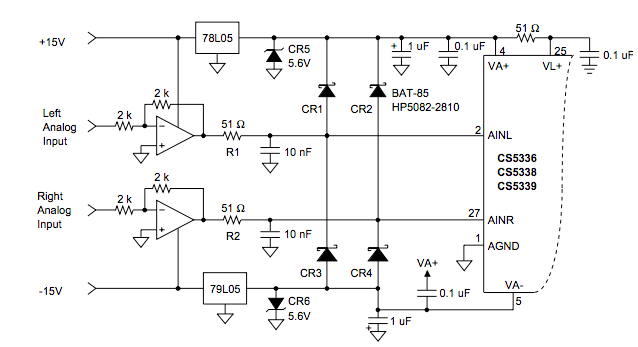

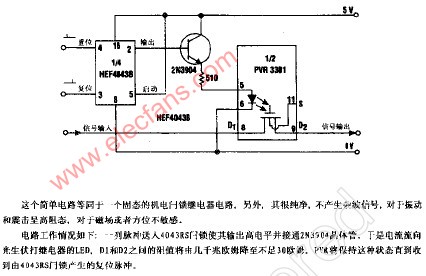

1、如果由于上电排序而发生闩锁,可以利用二极管与VDD串联如果任何时候器件的数字输入或输出都超过VDD,可以在VDD串联二极管(如下图使用1N914)来阻止SCR触发和随后的闩锁产生。这是因为二极管能够防止寄生横向PNP晶体管的基极电流从VDD引脚流出,从而防止SCR触发。

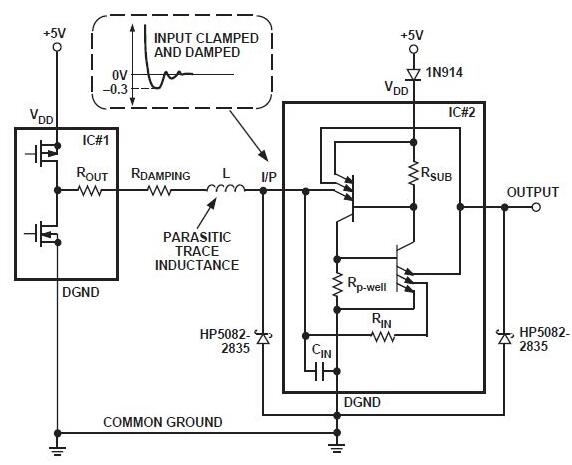

2、将肖特基二极管添加到DGND(数字地)可防止电压不足如果器件的数字输入和输出随时低于DGND,则可以从这些输入或输出连接到DGND的肖特基二极管将有效地将负偏移钳位在-0.3V至-0.4V之间。这可以防止寄生NPN晶体管的发射极与基极结导通,并且还可以防止SCR触发。

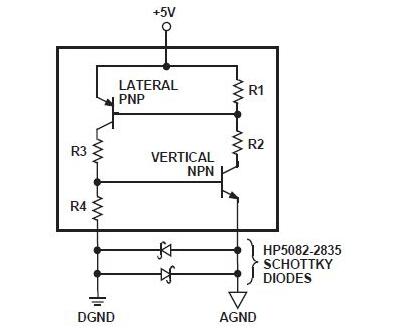

3、在DGND和AGND(vwin 地)之间连接肖特基二极管如果DGND电位偶尔会超过AGND0.3V或更多,则可以在器件两个引脚之间放置肖特基二极管来将阻止相关寄生NPN晶体管的导通。这提供了额外的防止闩锁的保护。此外,与前面提到的反向并联连接的额外二极管可以在另一个方向上将DGND限制到AGND,这大大减少了数字噪声被注入器件的可能性。

闩锁效应介绍

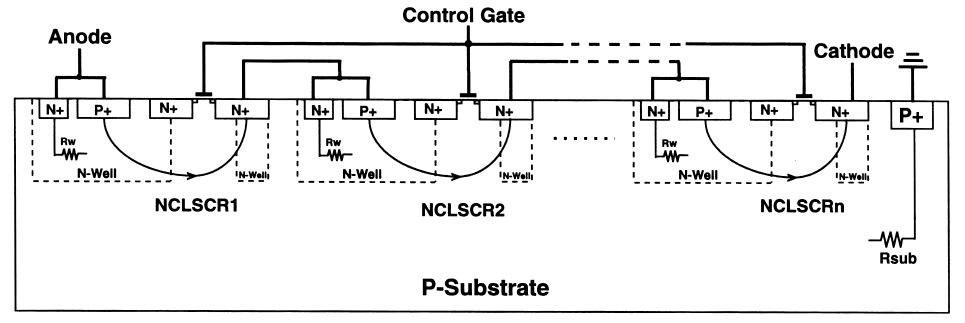

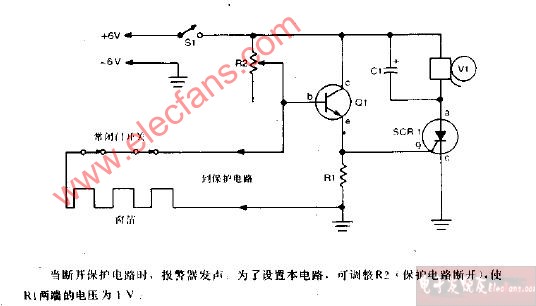

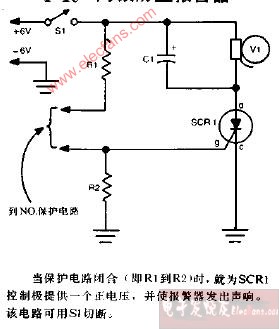

闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。闩锁效应是由NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成正反馈形成闩锁。避免闩锁的方法就是要减小衬底和N阱的寄生电阻,使寄生的三极管不会处于正偏状态。 静电是一种看不见的破坏力,会对电子元器件产生影响。ESD 和相关的电压瞬变都会引起闩锁效应(latch-up),是半导体器件失效的主要原因之一。

如果有一个强电场施加在器件结构中的氧化物薄膜上,则该氧化物薄膜就会因介质击穿而损坏。很细的金属化迹线会由于大电流而损坏,并会由于浪涌电流造成的过热而形成开路。这就是所谓的“闩锁效应”。在闩锁情况下,器件在电源与地之间形成短路,造成大电流、EOS(电过载)和器件损坏。

-

电路

+关注

关注

171文章

5666浏览量

170881 -

闩锁电路

+关注

关注

0文章

2浏览量

8588

发布评论请先 登录

相关推荐

CMOS闩锁测试中的电流脉冲如何加上的?

高速ADC的单粒子闩锁和瞬态

需要多少电流电压来引起闩锁

闩锁代码帮助

防闩锁型开关ADG5412 和ADG5413性能及优势分析

可控硅结构静电防护器件的防闩锁工程

如何防止电路中的闩锁问题

如何防止电路中的闩锁问题

评论