数字缓冲器和三态缓冲器可在数字电路中提供电流放大以驱动输出负载

在之前的教程中,我们研究了通常称为逆变器的数字非门,我们看到NOT门输出状态是其输入信号的补码,反相或反相。

因此,例如,当NOT门的单输入为“HIGH”时,其输出状态不会为“HIGH” ”。当其输入信号为“低”时,其输出状态将不为“低”,换句话说,它“反转”其输入信号,因此称为“逆变器”。

但有时在数字电子电路中我们需要将逻辑门彼此隔离或让它们驱动或切换高于正常负载,例如继电器,螺线管和灯,而无需反转。一种允许我们这样做的单输入逻辑门称为数字缓冲器。

与单输入,单输出逆变器或 NOT TTL 7404的门,它在输出上反转或补充其输入信号,“缓冲器”不执行反转或决策制作功能(如具有两个或更多输入的逻辑门),而是产生与其输出完全匹配的输出输入。换句话说,数字缓冲器没有任何作用,因为它的输出状态等于其输入状态。

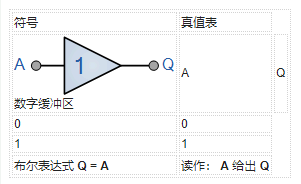

然后数字缓冲器可以被视为应用Boole幂等律的幂等门,因为当输入通过该设备时,其值不是改变。因此数字缓冲区是一个“非反相”设备,因此将给我们布尔表达式: Q = A 。

然后我们可以定义单个逻辑运算输入数字缓冲区为:

“Q为真,仅当A为真时”

换句话说,当输入 A 为真时,缓冲区的输出( Q )状态仅为真(逻辑“1”),否则其输出为假(逻辑“0”)。

单输入数字缓冲区

数字缓冲区也可以通过connectin制作g如下所示,两个 NOT 门。第一个将“反转”输入信号 A ,第二个将“重新反转”它返回到其原始电平,执行输入的双反转。

使用双反转NOT Gates

您可能正在思考,如果数字缓冲区没有反转,那么它的重点是什么?以任何方式改变其输入信号,或做出任何逻辑决定或操作,如 AND 或 OR 门,那么为什么不只是使用一段电线,而这是一个好点。但是,非反相数字缓冲器确实在数字电子产品中有许多用途,其主要优点之一是它提供数字放大。

数字缓冲器可用于将其他栅极或电路级彼此隔离,以防止一个电路的阻抗影响另一个电路的阻抗。数字缓冲器也可用于驱动高电流负载,例如晶体管开关,因为它们的输出驱动能力通常远高于其输入信号要求。换句话说,缓冲器可用于数字信号的功率放大,因为它们具有所谓的高“扇出”能力。

数字缓冲区扇出示例

扇出参数缓冲器(或任何数字IC)的输出驱动能力或逻辑门的输出电流能力给出输入信号的更大功率放大。可能需要将多个逻辑门连接到另一个逻辑门的输出或切换高电流负载(如LED),然后缓冲器将允许我们这样做。

通常输出逻辑门的通常连接到其他门的输入。每个输入都需要来自栅极输出的一定量的电流来改变状态,因此每个额外的栅极连接都会增加栅极的负载。因此,扇出是可以由逻辑门的一个数字缓冲器同时驱动的并行负载的数量。作为电流源,缓冲器可以具有高达同一逻辑系列的20个门的扇出额定值。

如果数字缓冲器具有高扇出额定值(电流源),则必须也有很高的“扇入”等级(当前下沉)。然而,门的传播延迟随着扇入而迅速恶化,因此应该避免扇入大于4的门。

然后输入和输出的数量是有限的。我们可以使用三态缓冲器或三态输出驱动器,而不是可以连接在一起,在我们需要将门彼此去耦的应用中。

“三态”缓冲区“

除了上面看到的标准数字缓冲器之外,还有另一种类型的数字缓冲电路,其输出可以在需要时与其输出电路”电子地“断开。此类缓冲区称为 3状态缓冲区,或更常见的是三态缓冲区。

A 三态缓冲器可以被认为是一个输入控制开关,其输出可以通过外部“控制”或“启用”电子转为“开”或“关”( EN )信号输入。该控制信号可以是逻辑“0”或逻辑“1”类型信号,导致三态缓冲器处于一种状态,允许其输出正常工作,产生所需的输出或另一种状态。状态是它的输出被阻塞或断开。

然后三态缓冲器需要两个输入。一个是数据输入,另一个是启用或控制输入,如图所示。

三态缓冲开关等效

当激活到其第三状态时,它禁用或关闭其输出,产生既不是逻辑“高”或“低”的开路状态,而是提供非常高阻抗的输出状态,高Z,或更常见的 Hi-Z 。然后这种类型的设备有两个逻辑状态输入,“0”或“1”,但可以产生三种不同的输出状态,“0”,“1”或“ Hi-Z ”这就是为什么它被称为“三态”或“三态”器件。

注意,这第三个状态不等于逻辑电平“0”或“1”,而是一个高阻态,其中缓冲器输出与电路的其余部分电断开。因此,没有电流从电源中提取。

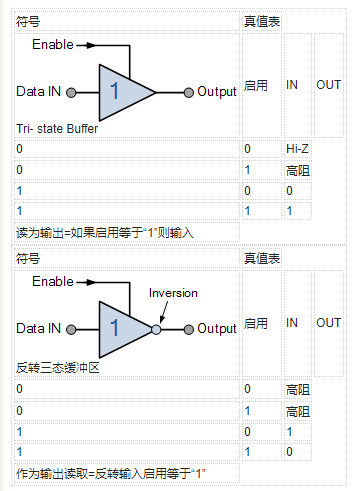

有四种不同类型的三态缓冲器,一组输出通过“Active-HIGH “控制信号产生反相或非反相输出,另一组缓冲器输出由”Active-LOW“控制信号控制产生反相或非反相输出反转输出如下所示。

激活“HIGH”三态缓冲区

高电平三态缓冲器,例如74LS241八进制缓冲器,当逻辑电平“1”应用于其“使能”时被激活控制线和数据从其输入传递到其输出。当使能控制线处于逻辑电平“0”时,缓冲器输出被禁用,输出端出现高阻抗条件 Hi-Z 。

高电平有效三态缓冲器也可以具有反相输出以及高阻态,从而产生高电平有效的三态反相缓冲器,如图所示。

有效“高电平”反相三态-state Buffer

当逻辑电平激活时,高电平有效的反相三态缓冲器(如74LS240八进制缓冲器)的输出被激活“1”应用于其“启用”控制线。输入处的数据传递到输出,但反转产生输入的补码。当逻辑电平“0”的使能线为低电平时,缓冲器输出被禁止,并且在高阻抗条件下, Hi-Z 。

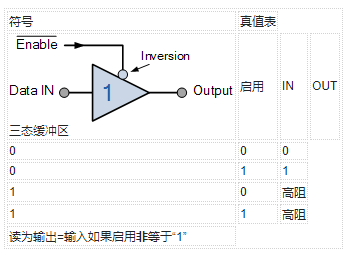

相同的两个三态缓冲器也可以使用低电平有效使能输入实现,如图所示。

激活“低电平”三态缓冲区

低电平有效三态缓冲器与上述相反,当逻辑电平“0”应用于其“时被激活使“控制线。数据从其输入传递到其输出。当使能控制线处于逻辑电平“1”时,缓冲器输出被禁用,输出端出现高阻抗条件 Hi-Z 。

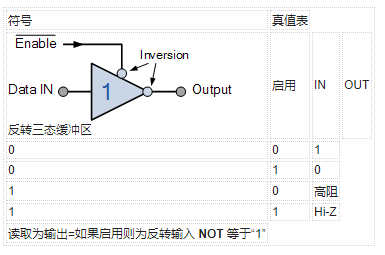

有效“低电平” “反转三态缓冲区

低电平反转三态缓冲区与上述相反,因为当逻辑电平“0”应用于其“启用”控制线时,其输出被启用或禁用。当缓冲区由逻辑“0”使能时,输出是其输入的补码。当使能控制线处于逻辑电平“1”时,缓冲器输出被禁用,输出端出现高阻抗条件 Hi-Z 。

三态缓冲控制

我们已经看到,缓冲器可以在数字电路中提供电压或电流放大,它也可以用于反转输入信号。我们还看到数字缓冲器以三态形式提供,允许输出有效地关断,产生相当于开路的高阻抗状态(Hi-Z)。

三态缓冲器用于许多电子和微处理器电路,因为它们允许多个逻辑器件连接到同一电线或总线,而不会损坏或丢失数据。例如,假设我们有一条数据线或数据总线,其中包含一些内存,外设,I / O或连接到它的CPU。这些设备中的每一个都能够在此单一数据总线上相互发送或接收数据,同时产生所谓的争用。

当多个设备连接在一起时会发生争用,因为有些设备想要将输出驱动为高电平而某些设备为低电平。如果这些设备同时开始发送或接收数据,当一个设备向总线输出逻辑“1”(电源电压)时,可能会发生短路,而另一个设备则设置为逻辑电平“0”或接地,导致短路情况,可能会损坏设备以及丢失数据。

数字信息通过这些数据总线或数据高速公路串行发送,一次发送一次,或者可能由八个(或更多)导线以并联形式连接在一起,例如在微处理器数据总线中,允许多个三态缓冲器连接到同一数据通道,而不会损坏或丢失数据,如图所示。

状态缓冲区数据总线控制

然后,三态缓冲区可用于隔离设备和电路数据总线和彼此。如果几个三态缓冲器的输出电连接在一起,则解码器用于在任何一个时间仅允许一组三态缓冲器有效,而其他器件处于高阻态。连接到4线数据总线的三态缓冲器示例如下所示。

三态缓冲器控制

这个基本示例显示了如何使用二进制解码器在数据集中单独或一起控制多个三态缓冲区。解码器选择对应于其二进制输入的适当输出,只允许一组数据将逻辑“1”或逻辑“0”输出状态传递到总线上。此时,连接到相同总线的所有其他三态输出通过置于高阻抗 Hi-Z 状态而被禁用。

当通过启用线, EN A <将有效HIGH信号施加到三态缓冲器时,数据组“A”中的数据只能传输到公共总线/跨度>。在所有其他时间,它表示有效地与数据总线隔离的高阻抗条件。

同样,当通过 EN <施加使能信号时,数据集“B”仅将数据传递到总线。子>乙 。连接在一起控制数据集的三态缓冲器的一个很好的例子是TTL 74244八进制缓冲器。

还可以连接三态缓冲器“返回到 - 返回“产生所谓的双向缓冲器电路,其中一个”高电平有效缓冲器“并联,但与一个”低电平有效缓冲器“相反。

这里,“启用”控制输入更像是方向控制信号,使得数据既被“读取”又被“发送”到相同的数据总线。在这种类型的应用中,可以使用具有双向开关功能的三态缓冲器,例如TTL 74245。

我们已经看到三态缓冲器是一个非反相器件仅在Enable( EN )引脚的输入为高电平时输出(与其输入相同),否则缓冲器的输出进入高阻态( Hi-Z )状态。三态输出用于许多集成电路和数字系统,而不仅仅用于数字三态缓冲器。

数字缓冲器和三态缓冲器都可用于提供电压或电流放大,从而驱动高负载,如作为继电器,灯或功率晶体管,而不是传统的逻辑门。但是缓冲器也可用于在两个或多个电路之间提供电气隔离。

我们已经看到,如果将多个三态设备连接在一起并且只要选择一个,则可以创建数据总线。任何时候,都没有问题。三态总线允许多个数字设备通过I / O信号和地址解码在同一数据总线上输入和输出数据。

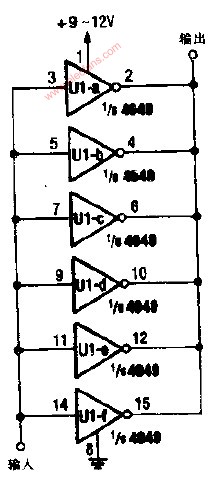

三态缓冲器可用于集成形成四路,十六进制或八进制缓冲器/驱动器,单向和双向形式,更常见的是TTL 74240,TTL 74244和TTL 74245,如图所示。

常用数字缓冲器和三态缓冲器IC包括:

TTL逻辑数字缓冲器

74LS07十六进制非反相缓冲器

74LS17十六进制缓冲器/驱动器

74LS244八路缓冲器/线路驱动程序

74LS245八进制双向缓冲区

CMOS逻辑数字缓冲区

CD4050十六进制非反相缓冲器

CD4503十六进制三态缓冲器

HEF40244三态八进制缓冲器

74LS07数字缓冲区

74LS244八态三态缓冲器

-

电路

+关注

关注

172文章

5901浏览量

172126 -

晶体管

+关注

关注

77文章

9682浏览量

138073

发布评论请先 登录

相关推荐

EVAL-AD9834EBZ,是一款数字控制振荡器,采用相位累加器,正弦查找表和10位DAC

JlinkV10的Vref疑问:输出的3.3V是否可以和板载3.3V连接

单输入逻辑门(数字缓冲器)这些特性你知道吗?

缓冲器,缓冲器是什么?

缓冲器,缓冲器基本原理是什么?

缓冲器的作用是什么

液压缓冲器的优点

松翰单片机--SN8F5702学习笔记(四)ADC

使用IDT时钟缓冲器提升应用设计

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

不同数字缓冲器教程

不同数字缓冲器教程

评论