在放大器电路设计中,你一定被被一些最常见的问题给“坑”过,这里为大家介绍一些最为常见的设计问题,提出了实用的解决方案,供各位侠士参考学习哦~

缺少直流偏置电流回路

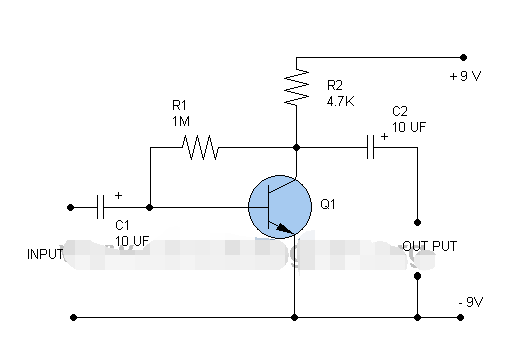

最常见的应用问题之一是在交流耦合运算放大器或仪表放 大器电路应用中,没有为偏置电流提供直流回路。图1 中,一个电容串接在一个运算放大器的同相(+)输入端。这 种交流耦合是隔离输入电压(VIN)中的直流电压的一种简单 方法。这种方法在高增益应用中尤为有用,在增益较高 时,即使是放大器输入端的一个较小直流电压,也会影响 运放的动态范围,甚至可能导致输出饱和。然而,容性耦 合进高阻抗输入端而不为正输入端中的电流提供直流路径 的做法会带来一些问题。

输入偏置电流流经耦合电容,给其充电,直到超过放大器 输入电路的额定共模电压或超过输出限值。根据输入偏置 电流的极性,电容充电或者向正电源电压方向,或者向负 电源电压方向。这个偏置电压会被放大器的闭环直流增益 放大。

这一过程可能较长。例如,对于一个带有场效应晶体管 (FET)输入端的放大器,若其偏置电流为1 pA,通过一个 0.1-μF的电容进行耦合,则其IC充电率I/C为

10–12/10–7 = 10 μV/秒

合600 μV/分。如果增益为100,则输出漂移为0.06 V/分。可 见,如果采用交流耦合示波器做短时间的测试可能无法检 测出这一问题,电路要在数小时后才会发生故障。总之, 避免这一问题是非常重要的。

图2 双电源供电运算放大器输入端交流耦合的正确方法

图2所示即是这一常见问题的一种简单解决方案。此例 中,一个电阻连接在运算放大器的输入端与地之间,从而 为输入偏置电流提供了一个回路。为最小化输入偏置电流 导致的失调电压,在使用双极性运放的时候,考虑运放两 个输入端的匹配问题,通常将R1设为R2和R3的并联值。

但要注意的是,该电阻始终会给电路带来一定噪声,因而 需在电路输入阻抗、所需输入耦合电容大小与电阻引进的 约翰逊噪声之间进行权衡。典型电阻值一般在100,000 Ω至 1 MΩ之间。

类似问题也会影响仪表放大器电路。图3所示的是通过两 个电容进行交流耦合的仪表放大器电路,也没有为输入偏 置电流提供回路。该问题常见于采用双电源供电(图3a)和 单电源供电(图3b)的仪表放大器电路中。

图3 错误的交流耦合仪表放大器电路

如图4所示,如果变压器次级电路中未提供直流到地回 路,这个问题也会发生在利用变压器耦合的电路中。

图5和图6给出了此类电路的简单解决方案。在各输入端与 地之间均添加了一个高值电阻(RA, RB)。对双电源仪表放大 器电路来说,这是一个简单而实用的解决方案。电阻为输 入偏置电流提供了一个放电路径。在双电源示例中,两个 输入端均以地作为参考。在单电源示例中,输入端既可以 地为参考(VCM接地)也可以一个偏置电压为参考,该偏置电 压通常为最大输入电压范围的一半。

同一原理也可用于变压器耦合输入端(图5),除非变压器次 级绕组有中心抽头,该中心抽头既可接地,也可连接至 VCM。在这些电路中,存在一个因电阻和/或输入偏置电流 不匹配导致的较小失调电压误差。为使此类误差最小,可 在仪表放大器的两个输入端之间连接电阻值约为两个电阻 十分之一(但与差分源电阻相比,该值仍较大)的另一个电 阻(从而将两个电阻桥接起来)。

为仪表放大器、运算放大器和ADC提供基准电压

图7所示的是一个单电源电路,是用一个仪表放大器驱动 一个单端模数转换器(ADC)。放大器基准电压源提供零差 分输入时的偏置电压,而ADC基准电压源则提供比例因 子。通常在仪表放大器输出端与ADC输入端之间使用一个 简单的RC低通抗混叠滤波器来降低带外噪声。设计师一般 倾向于采取简单的办法,比如利用电阻分压,来为仪表放 大器和ADC提供基准电压。在某些仪表放大器应用中,这 种方法有可能导致误差。

正确提供仪表放大器基准电压

通常认为仪表放大器基准输入端是高阻抗,因为它是一个 输入端口。因此,设计师可能将高阻抗源,比如电阻分压 器连接至仪表放大器的基准电压引脚。对于某些类型的仪 表放大器,这可能导致严重错误(见图8)。

例如,一种流行的仪表放大器设计结构采用三运算放大 器,其连接方法如图8所示。总信号增益为

若通过低阻抗源驱动,基准输入端的增益为单位增益。但 在此例中,仪表放大器的基准引脚直接与一个简单的分压 器相连。这破坏了减法电路的对称性以及分压电路的分配 比,降低了仪表放大器的共模抑制能力及其增益精度。但 在某些情况下,R4是可调的,因而可降低其电阻值,降低 量等于分压电阻的并联值(本例为50 kΩ)。此时,电路的表 现就像是将相当于电源电压一半的低阻抗电压源连接到保 持原始值的R4上。此外,还可使减法器的精度维持不变。

如果仪表放大器采用单芯片封装(IC),则不能使用这种方 法。另一考虑因素是,分压器电阻的温度系数还应能跟踪 R4以及减法电路中的其它电阻。最后,这种方法排除了调 节基准电压的可能。另一方面,如果试图通过在分压器中 使用小电阻值来降低附加电阻,则会增加电源的耗散电 流,进而增加电路功耗。这并非好的设计方法。

图9给出了一种较好的解决方案,该方案在分压器与仪表 放大器基准输入端之间采用了一个低功耗运放缓冲器。这 种方法消除了阻抗匹配和温度跟踪问题,并且允许轻松调 节基准电压。

在利用电阻分压供电电源给运放提供基准的情况 下保持PSR

一个经常被忽视的问题是,电源电压VS的噪声、跳变、或 漂移会反馈到基准输入端进而直接叠加到输出上,仅受分 压比影响而衰减。实际的解决方案包括采用旁路和滤波 器,甚至用高精度的基准IC,比如ADR121,来产生基准 电压,而不是对VS进行分压。

在设计同时采用仪表放大器和运算放大器的电路时,这种 考虑非常重要。电源抑制(PSR)技术可将放大器与电源嗡嗡 声、噪声以及跳变电压隔离。这一点非常重要,因为许多 实际电路都包含、连接至或存在于电源电压不够理想的环 境。除此之外,电源线路中存在的交流信号可能流回电路 并被放大,在某种条件下,还可能激发寄生振荡。

现代运算放大器和仪表放大器的设计已具有出色的低频电 源抑制性能。多数工程师也将此视为必然。许多现代运算 放大器和仪表放大器的PSR值达80 dB至100 dB以上,可使电 源变化的影响降低1万至10万倍。即使PSR值仅为40 dB,电 源变化与放大器间的隔离系数也可达100。然而,高频旁 路电容(如图1至图7所示)总是可取的,往往也是必要的选 择。此外,当设计师利用简单的电阻分压器来分压供电电 源以及运放缓冲器来为仪表放大器提供基准电压时,电源 电压的任何变化都会几乎没有衰减的顺利通过电路,直接 叠加到仪表放大器的输出电平上。因此,除非采用低通滤 波器,否则,IC将失去通常较为出色的PSR性能。

在图10中,一个大电容被加至分压器,以滤除电源变化, 从而使PSR保持不变。该滤波器的−3 dB极点由R1/R2并联组 合及电容CF设定。该极点应设为低于所关心的最低频率10 倍左右。

图10给出了一组−3 dB极点频率约为0.03 Hz的参数。跨接在 R3两端的小电容(0.01 μF)可使电阻噪声最小。

滤波器充电需要一定时间。根据图中所示值,基准输入端 的上升时间为几个时间常数(其中,T = R3Cf = 5 s),大约10 至15秒左右。

图11所示电路作了进一步改进。这种情况下,运放缓冲器 充当一个有源滤波器,可以用较小的电容实现等量的电源 去耦。此外,有源滤波器可设计提供更高的Q值,从而获 得更快的开启时间。

基于图11所示元件值,对电路进行了测试。其中,电源电 压为12 V,6 V滤波后的基准电压被提供给仪表放大器。一 个频率可调的1 V峰峰值正弦波被用来调制12 V电源,并将 仪表放大器增益设为单位增益。在这些条件下,用示波器 监测VREF和仪表放大器的输出,随着频率的降低,示波 器上未出现交流信号,直到接近8 Hz。在连接低电平输入信 号到仪表放大器时,测得该电路的电源范围为4 V至25 V以 上。电路开启时间约为2秒。

对单电源运算放大器电路进行去耦

单电源运算放大器电路要求对输入共模电平进行偏置以处 理正负摆动的交流信号。当采用电阻分压供电电源的方法 来提供偏置时,必须进行足够的去耦处理,以维持PSR不 变。

一种常见的,但是错误的做法是通过一个带有0.1 μF旁路电 容的100 kΩ/100 kΩ分压电路来向运算放大器的同相端提供 VS/2偏置。如果使用这些值,电源去耦往往显得不足,因 为其极点频率仅为32 Hz。

当电路工作在不稳定的环境下,图12(同相放大)和图13(反 相放大)给出了如何获得最佳效果的VS/2去耦偏置电路。两 种情况下,偏置功能均由同相输入端提供,反馈使反相输 入端获得相同的偏置,而单位直流增益则将输出偏置为同 一电压。耦合电容C1与BW3一致,滚降低频增益。

如图12所示,在使用100 kΩ/100 kΩ电阻分压电路的时候, 一条经验法则是,使用值至少为10 μF的C2,实现0.3 Hz时有 −3 dB的滚降特性。实际上,100 μF(0.03 Hz极点频率)的值就 足以应付所有电路了。

-

电路

+关注

关注

172文章

5901浏览量

172126 -

运算放大器

+关注

关注

215文章

4929浏览量

172824

原文标题:放大器电路设计:如何避免常见问题?

文章出处:【微信号:cirmall,微信公众号:电路设计技能】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

技术 | 放大器电路设计:如何避免常见问题?

技术 | 放大器电路设计:如何避免常见问题?

评论