谁没有被抓到在窗外做白日梦,在高速公路上静止地俯视汽车线,想知道更容易或更有效的方法按时上班?即便如此,有时候候补路线并不总是最快的 - 可能会有道路建设,或者正在进行的事件会让你不得不重新路线。在这一点上,大多数人倾向于抛出所有希望在窗外准时工作(或者,如果你住在伦敦,开始沿着肩膀开车)。

现在,想象每一个道路以及交通流量中的每个交叉路口或打嗝都是PCB的电源网络。您的工作将在PCB中导航,并分析如何以最小的功率损耗优化您的高功率效率。当您的目标是设计越来越小的PCB时,您的配电网络()的路径会变得更紧密。这开启了一系列设计问题:如何通过公寓楼之间的单车道小巷驾驶这辆半卡车?如果我的汽车侧面刮伤了防护墙并产生了火花,那么有什么东西可以起火吗?

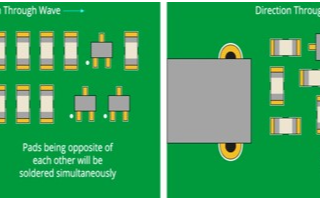

PCB设计师必须处理更高浓度的热量和噪音,这会对敏感部件造成威胁,影响相邻结构以及整个系统的功能。就像孩子一样,看着你的父母平行停放在一个非常紧张的地方,你也可以分配可容忍的力量,只要你记住坚实的设计技术,只需要最小的分配损失。

在配电中合并流量和管理热量

特别是在加利福尼亚州,高速公路延误的最大原因之一是人们没有遵循合并协议和其他规则。那么,在PCB设计中,所有的道路规则都是IC,微处理器,存储器模块,DSP(数字信号处理器)和FPGA(现场可编程门阵列)。如果您偏离电源电压的容差,那么您不能指望您的电路板规格得到满足。一些基础知识是一个很好的起点:

保持痕迹短而宽,以分散热密度。

最小化通过保持旁路环路的面积和长度尽可能小,阻抗为3:1的长宽比来实现阻抗。

优化组件之间的间距将产生最小电流和加热密度。

避免尖角使整个电路板上的热量基本保持“均匀”。

损失最小且最佳高功率效率与热管理密切相关。每个承载高电流的铜迹线和传导电流的每个电气元件都是由于电阻引起的热源。甚至诸如电阻器,电容器和电感器的无源元件也分别产生电阻和电抗加热。当你增加那个较少的车载房地产时,我们正在寻找更多的热点和铜穿孔,导致电流密度和加热的进一步增加。降低I2R的设计一直很重要,但对于低压器件来说,它们至关重要。

Heat分布是PCB布局最关键的设计考虑因素之一。

坑洼和鹿不是唯一的干扰

随着以最佳效率分配功率的目标,需要控制的另一种“损耗”是噪声和串扰形式的信号损失,这些被称为电磁干扰或EMI。挑战在于,几乎每个IC都是噪声发生器,每个高电流迹线都会发出可以作为噪声拾取的电磁辐射,基本上充当天线。此外,如果信号以300 MHz或更快的速度接通和断开,它们会引起相邻电路拾取的磁脉冲,从而产生串扰。以下是一些降低EMI和串扰的技巧:

对于输入模式下的I/O引脚,将未使用的输入连接到最低阻抗轨;如果可能的话,通过直接短路接地。

使非噪声走线远离嘈杂的元件,如连接,振荡器和继电器。

将嘈杂的迹线组合在一起,被地面痕迹包围。并且不要在电路板的外边缘上运行它们。

为了减少噪声传播,控制返回路径的形状和阻抗。请记住,噪声电压和相关电流将遵循最低阻抗回到生成点的路径。

不要在相邻导体中运行并行。

保持信号对之间的间距为迹线宽度的5倍。

管理配电和信号丢失似乎可以跟踪很多。特别是如果您正在设计具有高度特定的制造要求,则可以轻松地使用您的经验和专业知识来替代规则检查或忽略潜在干扰源。但是,通过强大的PCB设计软件,双重检查和回溯的大部分工作都可以放在布局软件的自动化范围内。

当你的PCB有信号干扰时,并不总是有警告标志告诉你。

这不是捷径,而是PDN Analyzer™将帮助您实现目标

低电压,高电流电子设备挑战任何设计PCB的人,以减少因电路板空间下降和元件密度增加而导致的配电损耗。集成电路和集成电路的进步与不断增长的需求保持同步;然而,对于PCB上所有理论和优质元件,底线仍然存在:您能否设计出具有速度和成本效率的统计上强大的PCB?答案是肯定的 - 用电力传输网络分析仪的平滑肌。

能够vwin PDN,噪声传播,布局前后和分析EMI场可以回馈一些摆动空间。为了能够在观察电流密度时评估热模式,在1 V平面上下降并且电流密度增加的地方 - 最终产品的功率最佳地分布在PCB上并且易于运行到制造。使用AltiumDesigner®的智能PCB设计软件及其可视功率分析直接在您的设计环境中查找并解决您的PDN问题,无需停工,特殊昂贵的工具或专业知识。

提供自己的能力分析,修改和重新分析您的工作。如果您对优化和减少分配损失有更多疑问,请立即联系Altium专家。

-

集成电路

+关注

关注

5387文章

11530浏览量

361604 -

pcb

+关注

关注

4318文章

23079浏览量

397437 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43030

发布评论请先 登录

相关推荐

我是pcb layout 设计师 (之一)

【高手问答】13:向资深PCB设计师取经:如何设计高速PCB

中国PCB Layout 设计师的机遇!(转贴)

成都 诚聘PCB设计师 待遇从优

【转】PCB设计基础知识 | PCB设计流程详解

每个设计师都需要知道的实用PCB布局提示

基于高速FPGA的PCB设计技术介绍

【8.25直播】PCB设计电源处理及整体PCB DFM检测

高浓度粘稠物料压力传感装置的研制与标定

年首次PCB设计师活动日邀请函

PCB设计工程师必须掌握的PCB制造知识

全球顶尖PCB设计师的作品如何?

PCB设计师必学的5个PCB设计指南

PCB设计师如何处理高浓度的热量和噪音?

PCB设计师如何处理高浓度的热量和噪音?

评论