与我在校期间在篮球队中茁壮成长的父亲不同,我在试训期间几乎无法反弹。毋庸置疑,我在开始之前就退出了运动。虽然我成为NBA职业球员的梦想破灭了,但后来我发现了我对武术的热情。我从来没有真正开始处理篮球,但至少在武术中,我可以从我的脚上反弹以迎接我的对手。

不能反弹篮球是一回事。然而,不了解电子设备中的接地反弹对于您的电路来说可能是非常有问题的。要想成为电路板,必须了解接地反弹对电路的影响。通过考虑接地反弹减少技术,您可以最大限度地减少设计中信号完整性的接地反弹。保护您的设计免受信号完整性问题的影响。

什么是接地反弹?

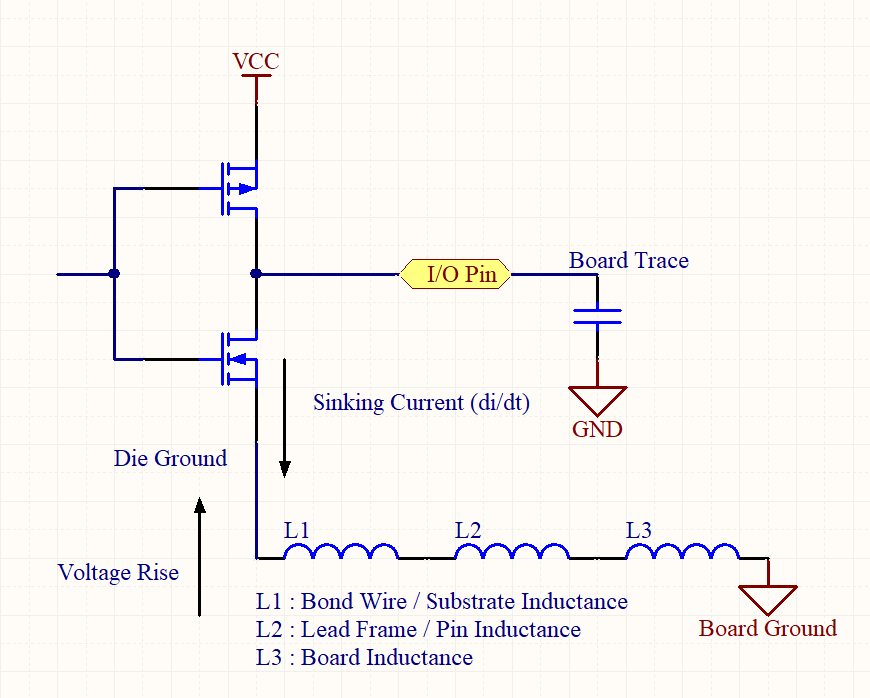

要了解接地反弹,您需要深入了解形成的晶体管的基础知识集成电路(IC)的核心。下图显示了微控制器和随机存取存储器(RAM)等IC的互补金属氧化物半导体(CMOS)电路。

CMOS逻辑门中的接地反弹

在大多数设计中,输出引脚通常连接到容性负载。当输出引脚置为逻辑'1'时,负载完全充电至VCC。当输出关闭为逻辑'0'时,电流快速从输出流向地。

在理想情况下,IC封装和电路板的接地将保持在相同的电压。然而,在大多数实际情况下,由于键合线,引线框架和电路板电感本身,在芯片接地和电路板接地之间存在电感。

当电流冲过电感时,在芯片接地和电路板接地之间建立电压。这会导致芯片接地和电路板接地瞬间处于不同电压电平的现象,从而导致接地反弹。

接地反弹如何影响电路

h2>

在最低水平,地面反弹不会对电子设备造成任何干扰。但是,当接地反弹很明显时,特别是当多个输出同时关闭时,器件的地电平上升到可能影响其他操作的水平。

例如,微控制器经历地面反弹可能它的地面转移到1.5V。工作在3.3V且连接到微控制器的逻辑IC可将逻辑“0”信号解释为“1”,因为它由于器件接地的电压电平而接收1.5V逻辑“低”信号。/p>

正在经历地面反弹的设备也可能误读其他组件的输入。例如,逻辑“高”信号会被误解为“低”,因为输入引脚的电压为1.8 V而不是3.3V,这是由于器件接地的上升所致。这低于2.31V的最小逻辑高电压。

减少接地反弹的技巧

减少接地反弹影响的最简单方法是在受影响的元件附近放置一个旁路电容。当输出逻辑电平快速变化时,这将使电流流入和流出电容器。重要的是将旁路电容尽可能靠近元件的VCC引脚放置,以最大限度地降低接地走线的总电感。

将一个电阻串联到输出负载可以减少瞬态时间变化的信号。这仅适用于输出不是时序敏感的情况,例如并行SRAM的地址总线。此方法适用于触发输出的控制引脚,如继电器或LED。

当所有输出同时驱动为低电平时,接地反弹的影响最大。那时芯片的电压差大幅增加。为了防止这种情况,请尝试分散输出驱动低的时间。在这里,甚至额外的毫秒延迟也会产生显着的差异。

作为一般规则,你应该避免在易受攻击的逻辑IC上放置毛刺敏感信号,如RESET,CHIP SELECT或SET地面反弹问题。总的来说,靠近GND引脚的输出引脚可以减少接地反弹问题。因此,您应该将关键信号放在GND引脚旁边的引脚上。

旁边放置旁路电容逻辑组件。

检测设计中的潜在接地反弹问题

最后,放置旁路电容器是一种适用于广泛的设计。它保持良好的电力传输网络并可靠地减少地面反弹。为了最大限度地减少设计中不受控制的电压降并发现其他潜在的功耗问题,请尝试使用Altium PDNAnalyzer™。

使用此工具,您可以同时vwin 多个网络的电力传输,并轻松识别直流电压或电流密度的问题。但最好的部分是它位于AltiumDesigner®的PCB设计软件中,可以在同一个统一的设计环境中从原理图转换到仿真。

地面反弹是否会对您的设计造成严重破坏?获得Altium专家的帮助。

-

pcb

+关注

关注

4319文章

23080浏览量

397456 -

电路设计

+关注

关注

6673文章

2451浏览量

204138 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43031

发布评论请先 登录

相关推荐

【转】电源的电磁干扰技术设计要点

计算机控制抗干扰技术设计

如何降低dc to dc电路的辐射发射?

如何降低dc to dc电路的辐射发射?

模拟电子技术设计

如何地面反弹降低技术设计电路?

如何地面反弹降低技术设计电路?

评论