使用外部SDRAM的一些STM32应用客户报告他们的产品正在进行EMC测试,并且存在由于SDRAM信号导致的过度辐射干扰的问题。在终端产品中,如果外壳不能用于屏蔽辐射干扰,这些问题通常需要通过修改SDRAM信号的PCB设计来解决。

这里概述了如何在SDRAM PCB应用设计中改善辐射干扰问题,供参考。

PCB设计中的SDRAM辐射干扰对策

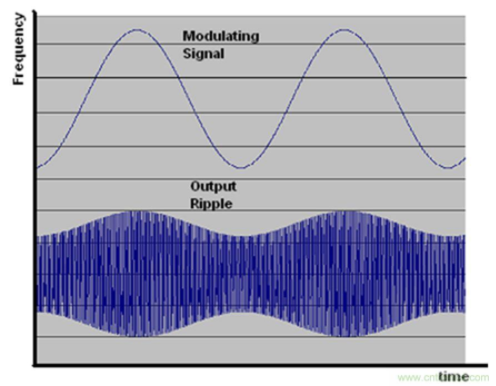

因为SDRAM工作频率较高且具有陡峭的上升沿和下降沿,有必要在PCB设计中处理高速信号传输线中的信号走线。请注意以下基本原则:

1。保持SDRAM信号的完整性

SDRAM信号的失真将进一步扩大信号的辐射频谱,导致更严重的辐射问题,所以必须注意SDRAM信号完整性设计。

建议使用4层或更多层来控制SDRAM信号的特征阻抗50欧姆,最大限度地减少SDRAM总线上的过孔使用,保持阻抗连续性,并减少阻抗不连续引起的信号反射。 ;

SDRAM信号走线间距应遵循3W原则,两条走线的中心间距应至少保持线宽的3倍,这可以减少信号之间干扰引起的信号失真;

尽可能靠近靠近MCU的SDRAM,缩短MCU到SDRAM的长度信号迹线(通常不应超过120 mm);

2。保持最短的SDRAM信号返回路径

对于多层PCB,高速信号的返回路径是其迹线的投影在参考平面上。在PCB设计中,应注意保持参考平面的完整连续性。如果由于信号切换或功率层分裂等而切断信号返回路径,则需要增加层改变电容/层改变通孔和电源平面交叉。电容器等确保SDRAM信号具有最短的返回路径。

3。将SDRAM信号(尤其是时钟信号)放在PCB的内层。

在SDRAM信号中,时钟信号具有最强的辐射水平,可以通过将其放置在PCB的内层并屏蔽外层铜箔来减少。

对于STM32 FMC接口同时采用SDRAM和FLASH设计, SDRAM和FLASH共享一些MCU引脚,其复杂的布线拓扑进一步增强了SDRAM信号的辐射干扰。建议路由SDRAM和FLASH。它们尽可能多地放置在PCB的内层,这些信号在PCB外层的地平面处被屏蔽。

4。保持SDRAM走线区域尽可能远离其他信号/电缆

更长的其他走线或电缆可用作天线传输耦合SDRAM辐射信号,因此它们应放置在远离SDRAM信号的PCB中,并在必要时放置在这些走线或电缆连接上。磁珠或滤波器衰减SDRAM辐射信号。

-

SDRAM

+关注

关注

7文章

423浏览量

55203 -

电磁干扰

+关注

关注

36文章

2312浏览量

105391 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43030

发布评论请先 登录

相关推荐

怎么提高运放电路PCB的抗辐射干扰?

要通过PCB导入siwave,获得电流分布,然后在HFSS结构中,进行协同仿真,来实现实际PCB的辐射干扰仿真,请问如何操作?

基于示波器的EMI辐射干扰测试

H桥驱动电机辐射干扰严重

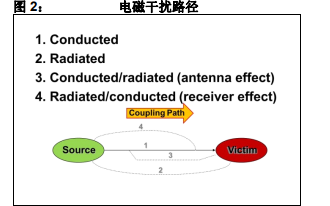

电磁干扰与电磁兼容之二:传导干扰和辐射干扰

8位PIC中单片机的传导干扰和辐射干扰的测试方法和产品性能中文概述

如何减少传导干扰和辐射干扰

PSB工程师,你知道如何改善SDRAM信号的辐射干扰?资料下载

概述了如何在SDRAM PCB应用设计中改善辐射干扰问题

概述了如何在SDRAM PCB应用设计中改善辐射干扰问题

评论