加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

加法器电路设计方案一:BCD加法器的设计

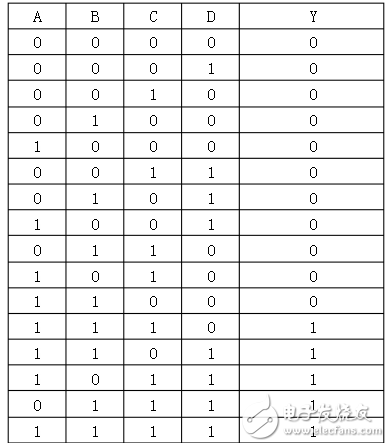

BCD加法器的设计, 目的是根据彩灯亮灭的方式,来显示两个BCD码相加之和。

本设计要求考虑高位溢出,无高位溢出时,求和结果用8个LED灯显示,亮的为1,灭的为0,读出BCD码转化为十进制,即为结果;若有高位溢出时,第9个灯亮,所得结果已超过两位,通过9个灯结合读出结果。

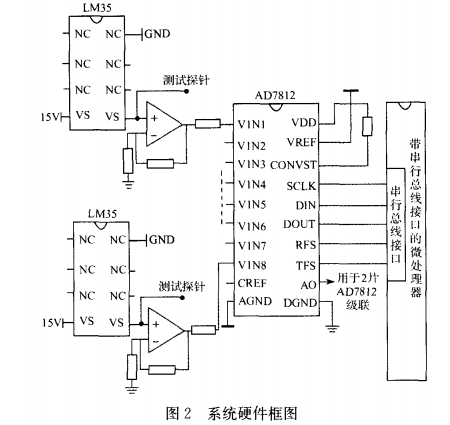

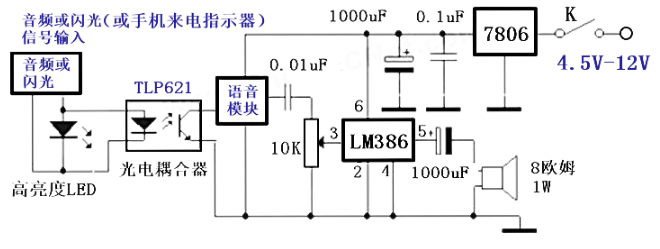

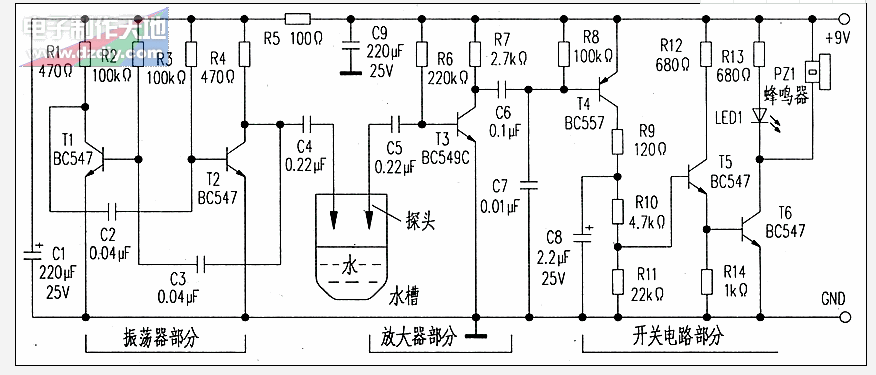

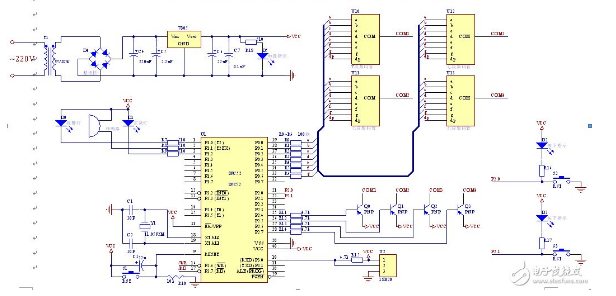

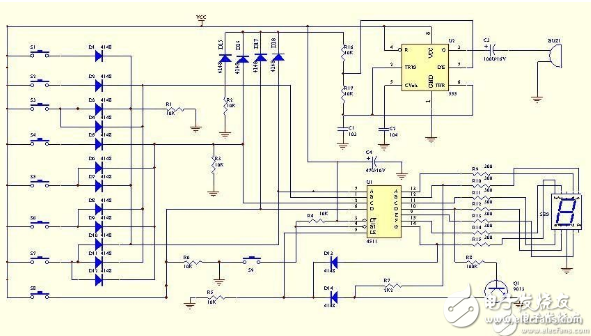

硬件接线图

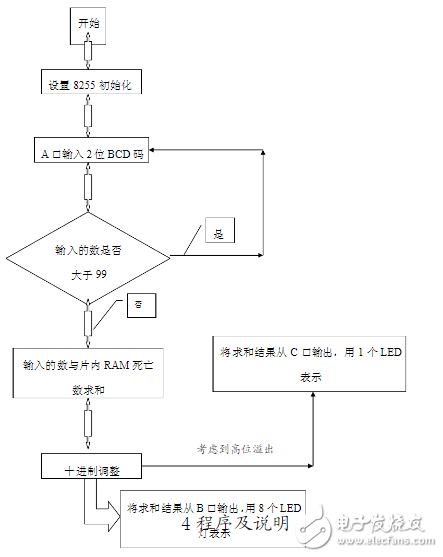

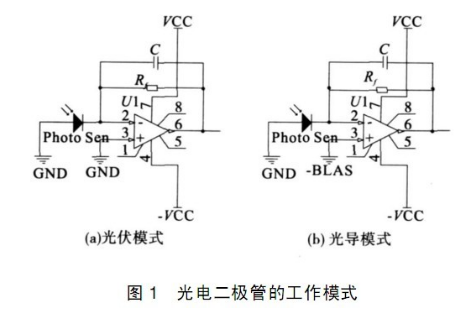

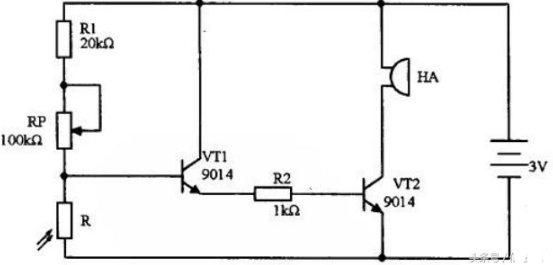

程序流程图

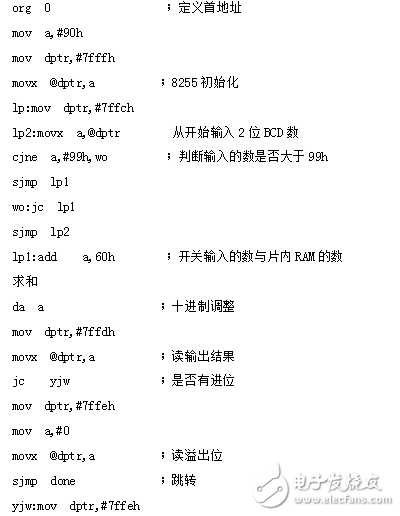

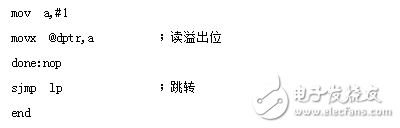

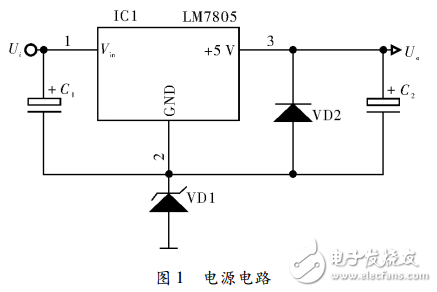

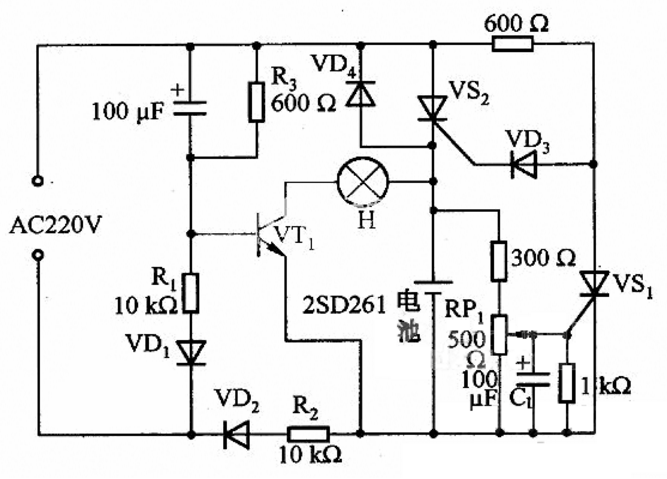

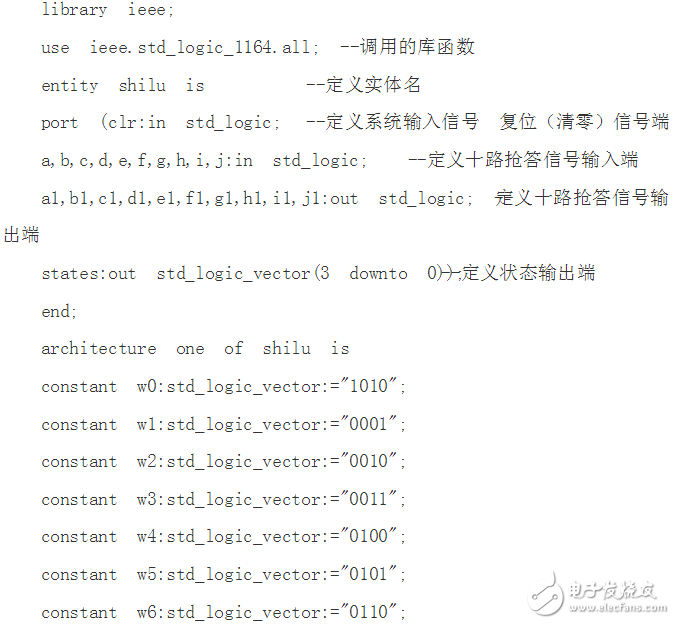

程序设计

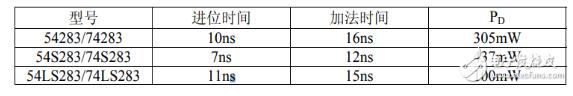

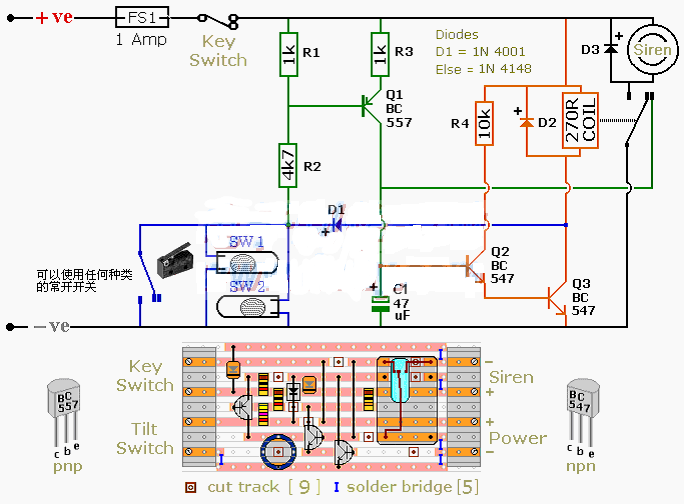

加法器电路设计方案二:8位级联加法器的设计

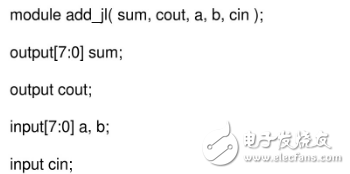

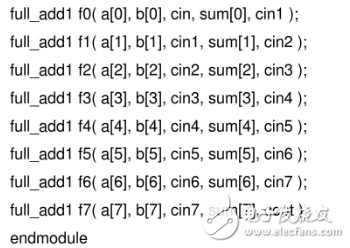

8位级联加法器的设计程序

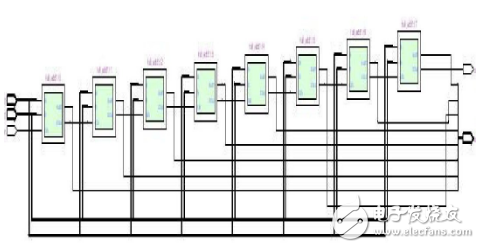

8位级联加法器RTL图

德赢Vwin官网

App

德赢Vwin官网

App

评论