计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。本文为大家带来七种任意进制计数器设计方案及其电路设计的原理详解。

任意进制计数器设计方案一:采用反馈置数法来设计任意进制计数器

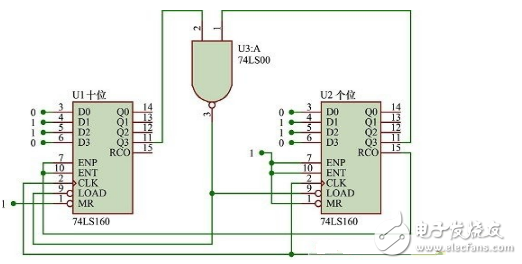

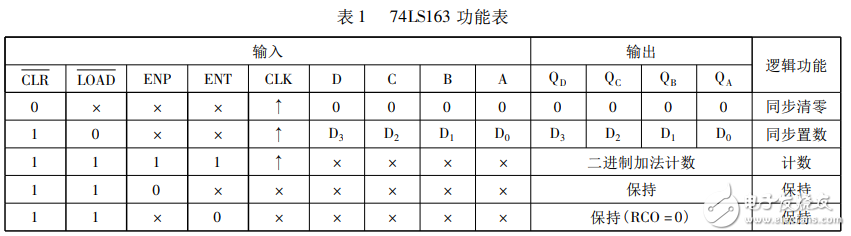

此方法适用于某些具有预置数的计数器,它是采用预置数控制端LOAD来实现。对于74LS160属于同步式预置数的计数器来说,当LOAD出现有效电平低电平后待下一个时钟脉冲信号到来后计数器输出端的状态Q3Q2Q1Q0=D3D2D1D0.使其跳过某些状态来设计任意进制计数器。下面就以74LS160为例,用并行置数法设计23进制计数器,其中预置数端D3D2D1D0可以置零,也可以置十以内的任意四位二进制数。那么此电路在其置数时十位和个位的D3D2D1D0置入(01100110)8421BCD码=(66)10,而反馈代码十位和个位为(10001000)8421BCD码=(88)10,相当于十进制数的88.由此分析可得到计数器的模为(88-66)+1=23,故计数器为23进制计数器,其设计电路图如图5所示。由此可以得到置数法的设计要点为:反馈代码转换成的十进制数-预置数端的代码转换成的十进制数+1=所设计的计数器的模。

任意N进制计数器的设计方法及步骤

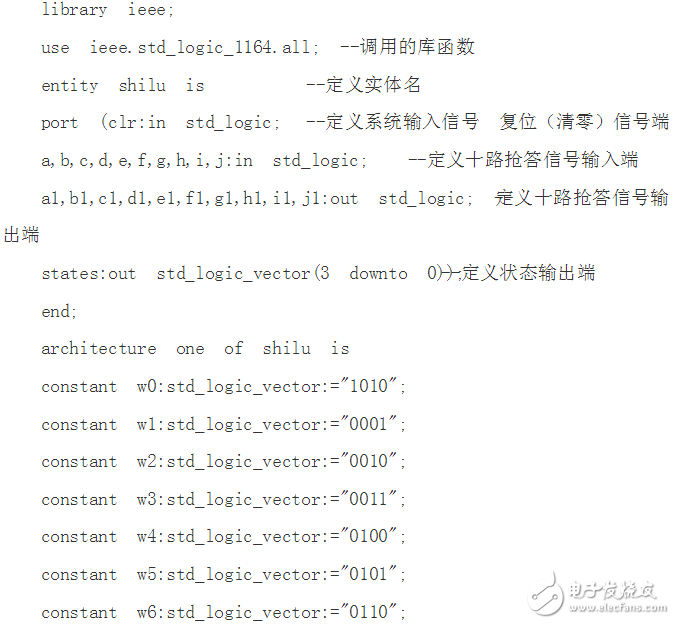

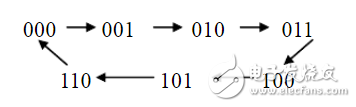

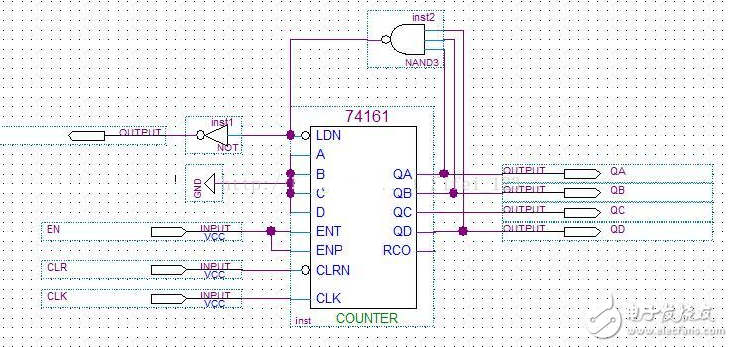

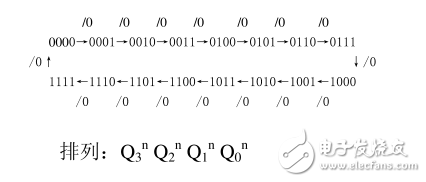

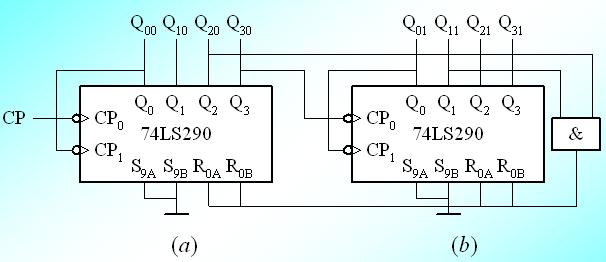

(1)根据计数模N来确定所需要计数器芯片的个数n.n=INT(logm(N-1))+1,INT表示取整。m:当芯片为十进制计数器时m取10,当芯片为四位二进制计数器时m取16.

(2)当n个计数器芯片连接成模为m的计数器

(3)选用并行法或串行法将n个计数器连接起来。

(4)确定反馈置零代码。如果计数器芯片采用异步置零反馈代码为(N)10,若是采用同步置零,则反馈代码为(N??1)10.

(5)反馈置零代码形式的转换。如果芯片为十进制制计数器,将反馈代码转换成8421BCD码的形式。若是四位二进制计数器,则将反馈代码转换成二进制数。

(6)将转换结果与计数器的状态输出端进行比较,让与1对应的引脚作用到与非门(反馈置零端低电平有效)或者与门(反馈置零端高电平有效)的输入端,然后将与非门或者与门的输出,连接到计数器芯片的反馈置零端即可。

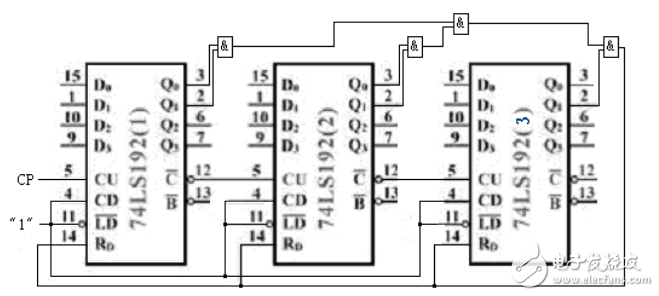

任意进制计数器设计方案二:采用清零法来设计任意进制计数器

CR(RD)=(Q1Q0)百(Q1Q0 )拾(Q1)个 初态:0000

终态:233-1=232即:0010 0011 0010

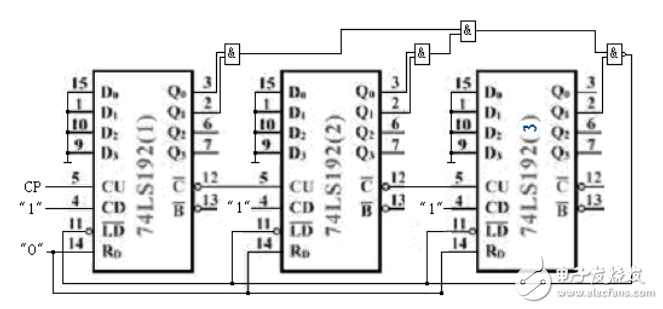

任意进制计数器设计方案三

LD=(Q1Q0)百(Q1Q0 )拾(Q2Q0)个 (或LD=CO)

初态:0000 (或1000-332=668)

终态:332-1=331即:0011 0011 0001 (或999)

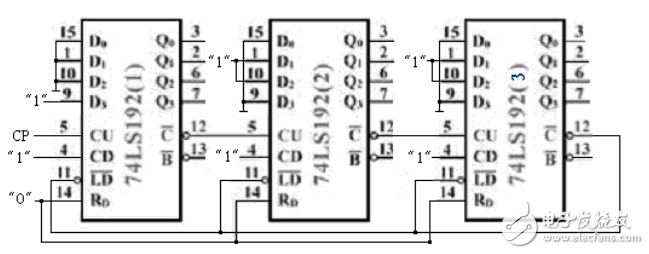

任意进制计数器设计方案四:采用置数法来设计任意进制计数器1

由于74LS192是具有异步清零、置数功能的十进制计数器,因此保留哪233种状态,方法有多种。

任意进制计数器设计方案五:采用置数法来设计任意进制计数器2

德赢Vwin官网 App

德赢Vwin官网 App

评论