。传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。 随着数字技术的发展,全数字锁相环ADPLL(AllDigital

2010-03-16 10:56:10

德赢Vwin官网

网站提供《CMOS电荷泵锁相环电路图设计.pdf》资料免费下载

2023-10-09 14:57:28 0

0 锁相环可不可以用于倍频非周期信号? 锁相环(Phase Locked Loop,简称PLL)是一种常用的电子电路,可以用来锁定输入信号的相位和频率。它具有广泛的应用领域,如通信系统、数字信号处理

2023-09-02 15:12:37 133

133 锁相环倍频器锁在基频怎么办? 锁相环倍频器是一种基于相位锁定原理的电子设备,它能够将输入信号的频率倍增。然而,有时候锁相环倍频器会锁在基频上,导致无法达到所要求的倍频效果。这时候,我们需要采取一些

2023-09-02 15:12:31 169

169 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 386

386 pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频

2023-09-02 14:59:24 444

444 硬件锁相环电路怎么设计?硬件锁相环电路的设计通常包括以下步骤。

2023-08-08 11:16:46 223

223 大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 672

672

锁相环电路,是调频电路的重要组成之一,锁相环电路的原理的认识是DDS学习的一个重点之一。

2023-07-24 15:37:05 791

791

模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 2765

2765 PLL锁相环倍频是一种用于改变输入信号频率的技术,它可以将输入信号的频率放大或缩小,以达到某种特定的目的。

2023-02-14 15:56:35 1449

1449 数字功放电路图大全免费下载。

2022-07-11 09:42:32 81

81 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 10729

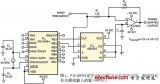

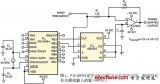

10729 一种倍频控制单元,通过编程锁频倍数和压控振荡器延迟单元的跨导,有效扩展了锁相环的锁频范围。该电路基于 Dongbu HiTek 0.18µm CMOS工艺设计,仿真结果表明,在1.8 V的工作电压下,电荷泵电路输出电压在0.25~1.5 V变化时,电荷泵的充放电电流一

2020-09-17 10:45:00 2

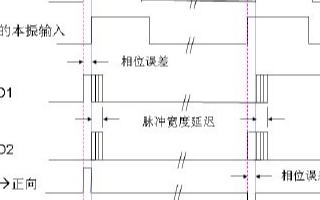

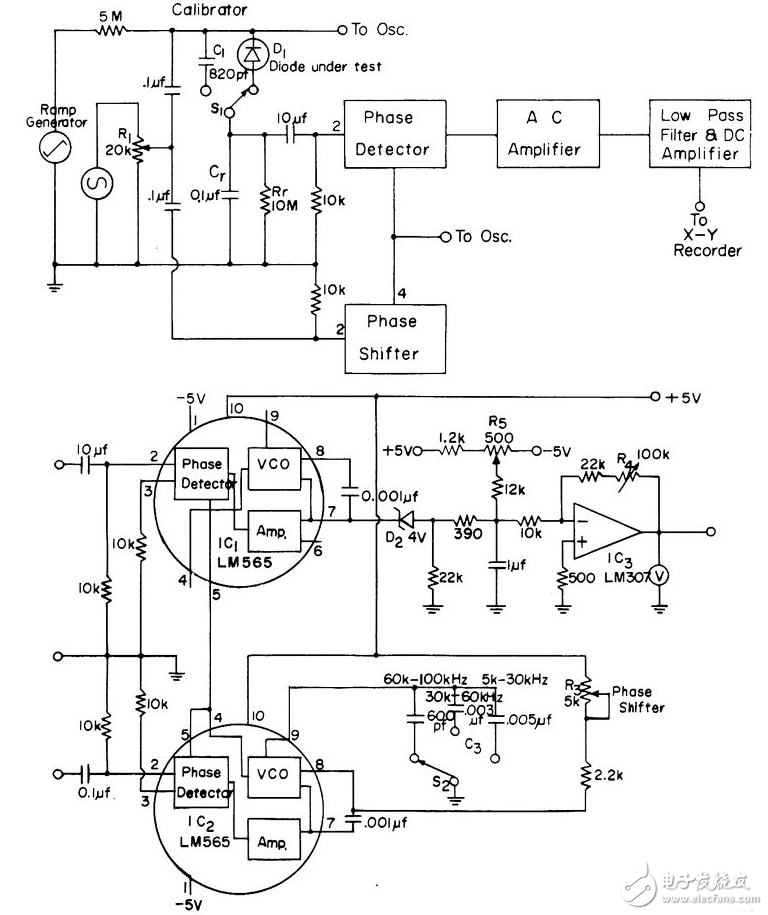

2 电荷泵锁相环的锁定检测电路设计,包括模拟锁定检测和数字锁定检测两种方法。其中,模拟检测电路采用经鉴频鉴相器PFD 输出的相位误差,产生脉冲信号对外部电容进行充电和放电,需要较长的时间以达到稳定的电平

2020-08-24 14:11:38 2743

2743

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 24

24 的问题进行了讨论。 引言 锁相环(PLL)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的PLL相比,具有精度高

2018-10-25 09:17:13 7963

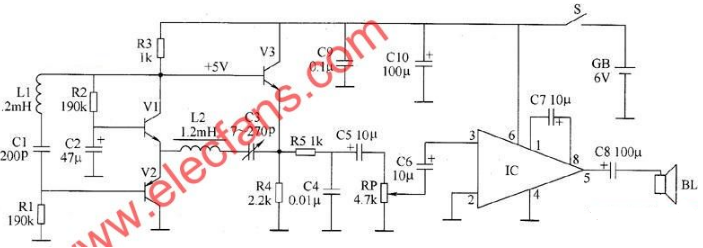

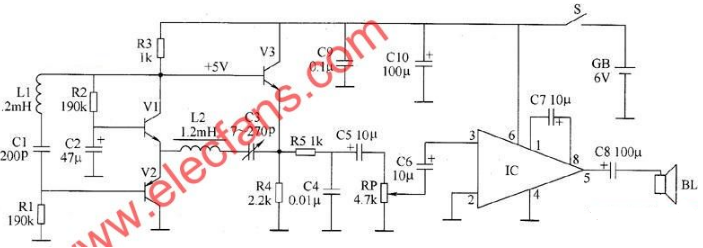

7963 本文主要介绍了脉冲金属探测器电路图大全(五款脉冲金属探测器电路原理图详解)。采用锁相环IC的金属探测器电路,使用锁相环,灵敏度较高,探测距离可达75cm。其基本原理是锁相环IC中的VCO(压控振荡器

2018-03-25 16:31:00 87726

87726

锁相环(phase locked loop),顾名思义,就是锁定相位的环路。学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出

2018-02-21 11:43:00 44802

44802

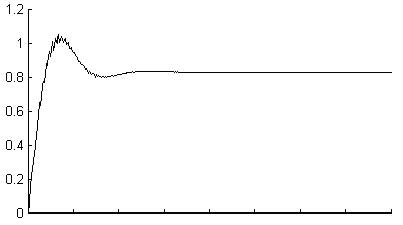

技术设计了倍频电路。首先论述了锁相环的基本原理和环路滤波器的参数设计方法,然后利用ADS软件对锁相环的环路滤波器进行了设计和仿真。最后,将设计的环路滤波器应用于实际电路,并给出了测试结果。

2017-12-07 14:46:47 12

12 一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 18

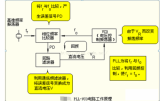

18 随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟

2017-09-12 16:54:55 0

0 锁相环就是锁定相位的环路,它一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。

2017-07-24 15:07:12 27198

27198

集成电路模拟锁相环原理及NE564在实验电路中的应用

2016-01-20 15:40:40 84

84 如何设计并调试锁相环(PLL)电路 pdf

2016-01-07 16:20:08 79

79 有关锁相环的部分资料,对制作锁相环有一定的帮助。

2015-10-29 14:16:55 62

62 本材料是基于单片机分频的锁相环测试系统电路图。

2015-10-28 13:47:49 6

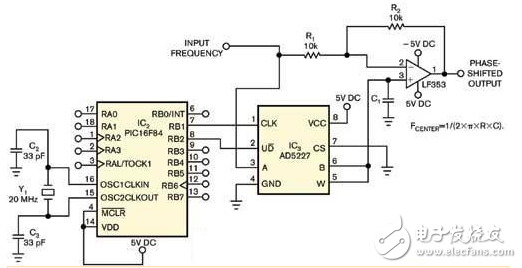

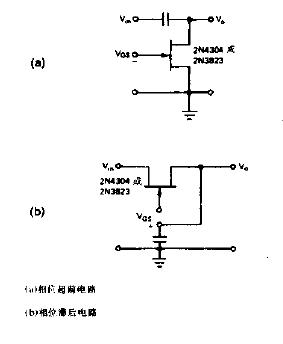

6 移相器广泛应用于各种电路,但由于在放大器中的偏差以及电容公差,通常很难实现电路精确控制所需的精确移相。图1中的电路利用AD5227 64步递增/递减数字电位器IC3可以控制输入到输出

2011-12-12 14:03:48 1849

1849

介绍了锁相环集成电路CD4046 的工作原理及其内部结构, 给出了锁相环集成电路在工业自动化仪表中的一些具体应用实例, 如调制解调电路、频率变换电路、锁相倍频电路等。

2011-11-11 15:50:32 115

115 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

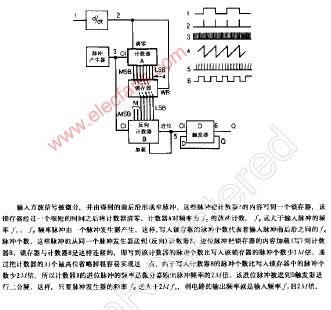

频率跟踪的 锁相环电路 由专用锁相芯片CD4046和分频芯片CD4040组成,以实现工频信号的锁相倍频,分频比为1/64。在工频信号恰好为50 Hz的情况下,该电路的锁相倍频频率为5064=3 200 Hz,相

2011-10-26 11:17:47 8375

8375

本书是图解电子工程师实用技术丛书之一,本书主要介绍锁相环(PLL)电路的设计与应用,内容包括PLL工作原理与电路构成、PLL电路的传输特性、PLL电路中环路滤波器的设计方法、PLL电路

2011-09-14 17:55:24 2104

2104 目录: 基础理论 环路的性能 电路实解 锁相环在手机中的应用

2011-05-02 11:05:01 468

468 电荷泵锁相环的锁定指示电路设计,常用的方法是在PFD 电路中通过检测经分频后的参考输入和本振反馈信 号的相位误差来实现,当相位误差超过某个锁定检测窗口时,锁相环电路就上报失锁告警。由于数字锁定指示电路 设计简单,易于被监控而被广泛应用。在实际的

2011-03-16 10:20:51 58

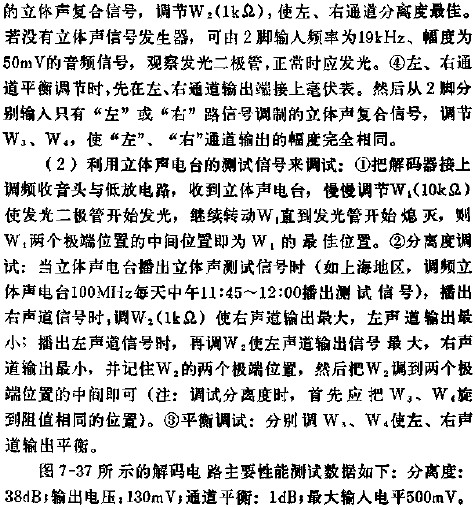

58 D3361调频立体声解码电路,采用锁相环方式解码,它比D3301解码电路多了一个锁相环电路,因此性能较D3301优越.主要

2010-10-11 13:10:13 2022

2022

基于fpga的锁相环位同步提取电路

该电路如图所示,它由双相高频时钟

2010-10-08 12:00:23 1410

1410

数字三相锁相环中含有大量乘法运算和三角函数运算,占用大量的硬件逻辑资源。为此,提出一种数字三相锁相环的优化实现方案,利用乘法模块复用和CORDIC算法实现三角函数运算

2010-09-30 16:35:54 35

35 锁相环的英文全称是Phase-Locked Loop,简称PLL。它是由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)三部分构成的一种信号相差自动调节反馈电路(环)。PLL电路框图如下,其

2010-09-07 16:33:52 662

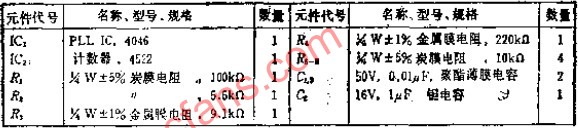

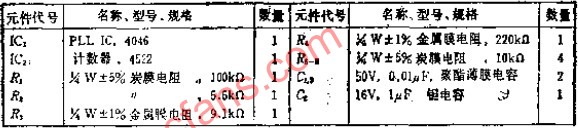

662 采用PLL(锁相环)IC的频率N(1~10)倍增电路

电路的功能

很多电路

2010-05-12 10:51:53 1457

1457

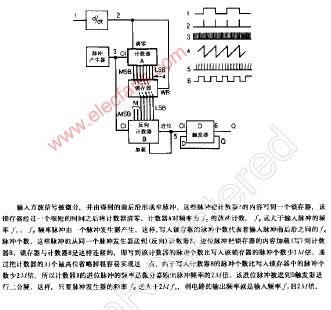

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 5312

5312 宽频带数字锁相环的设计及基于FPGA的实现数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的

2009-11-23 21:00:58 1101

1101

锁相环电路

锁相环

2009-09-25 14:28:39 6731

6731

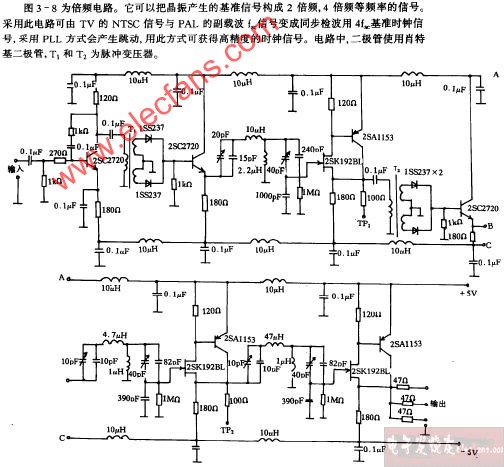

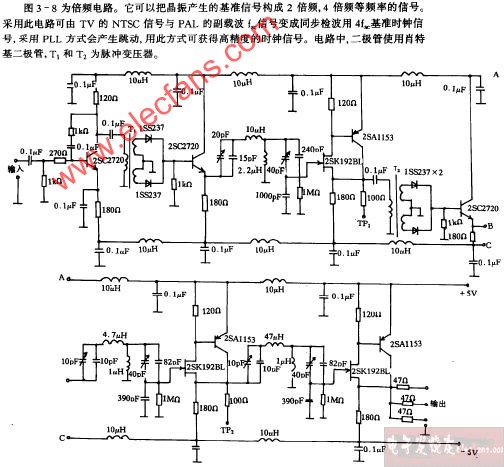

不带锁相环的倍频器

2009-09-17 16:11:00 805

805

锁相环电路的设计:

2009-07-25 17:05:36 536

536

倍频电路图

2009-07-14 17:09:47 2971

2971

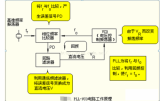

智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 70

70 摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1313

1313

倍频电路图

2009-05-08 14:28:08 2615

2615

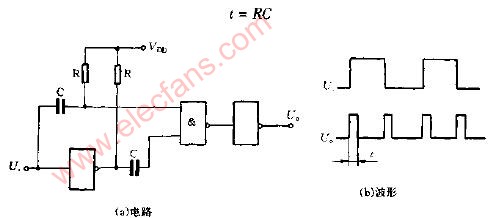

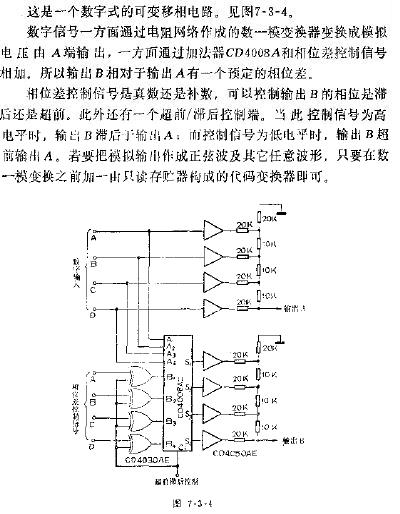

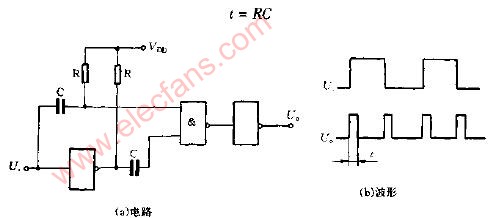

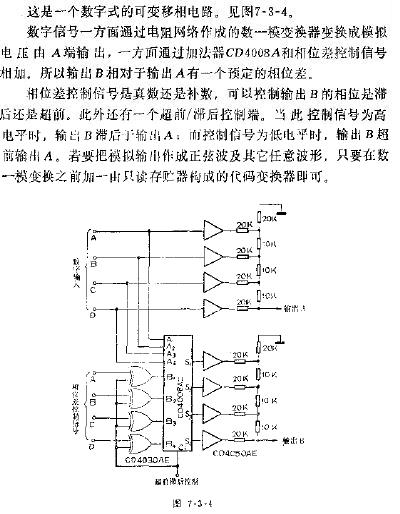

数字移相器电路图

2009-04-15 10:53:23 2350

2350

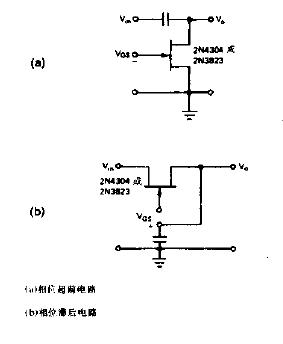

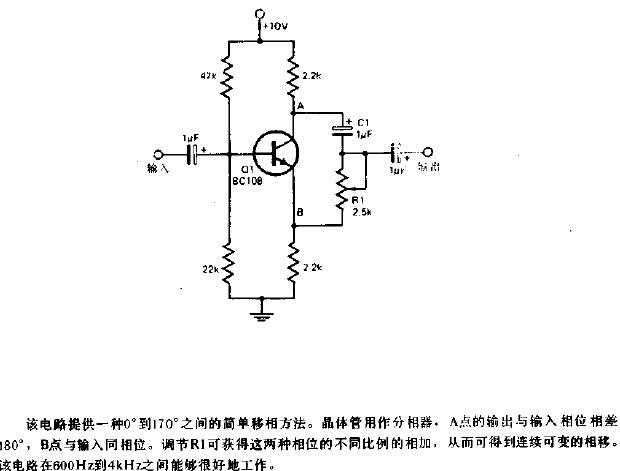

移相电路图

2009-04-06 09:04:39 2697

2697

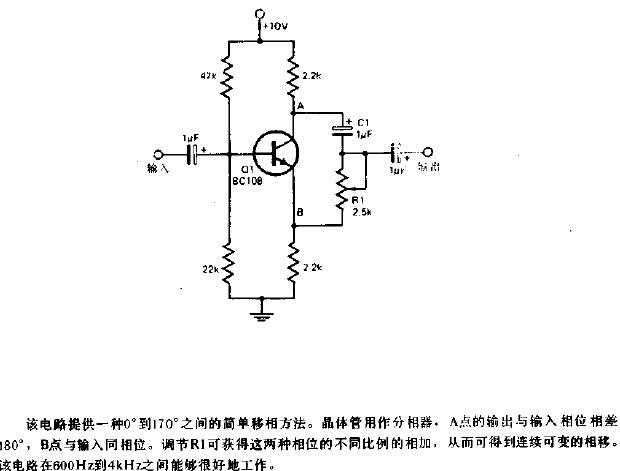

单管移相器电路图

2009-04-06 09:03:32 1078

1078

实验五 数字锁相环与位同步

一、 实验目的

1. 掌握数字锁相环工作原理以及触发式数字锁

2009-04-01 09:27:45 4862

4862

一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 124

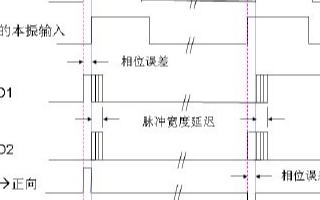

124 应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下

2008-10-16 08:59:42 967

967

智能全数字锁相环的设计

摘要: 在FPGA片内实现全数字

2008-08-14 22:12:51 52

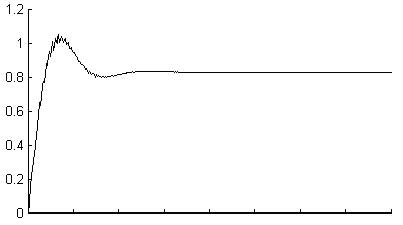

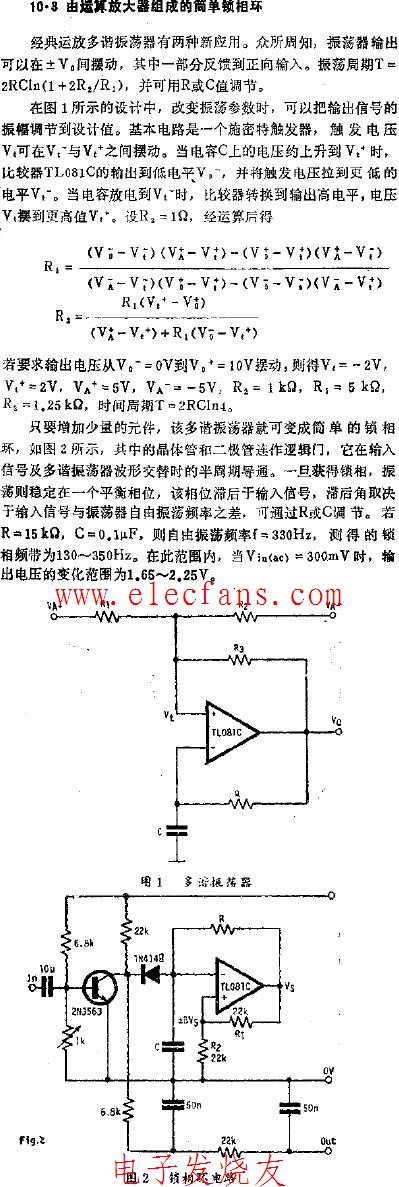

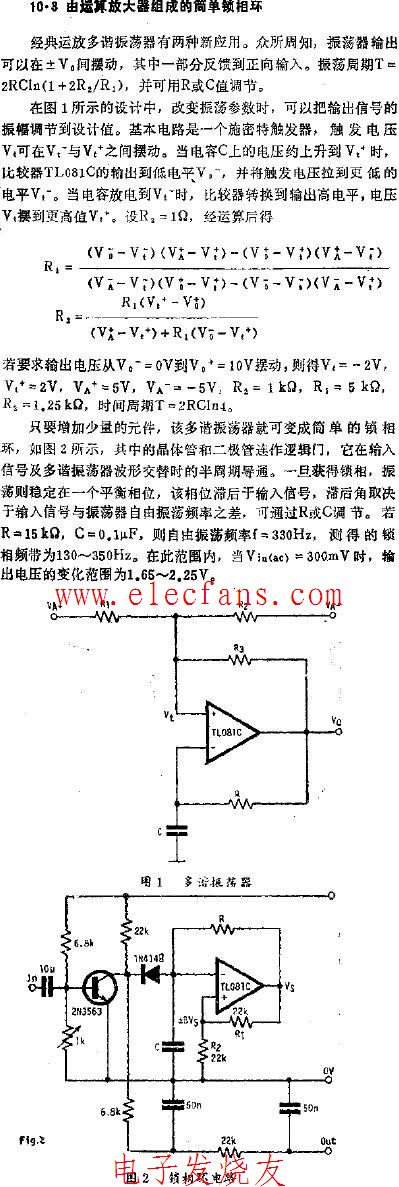

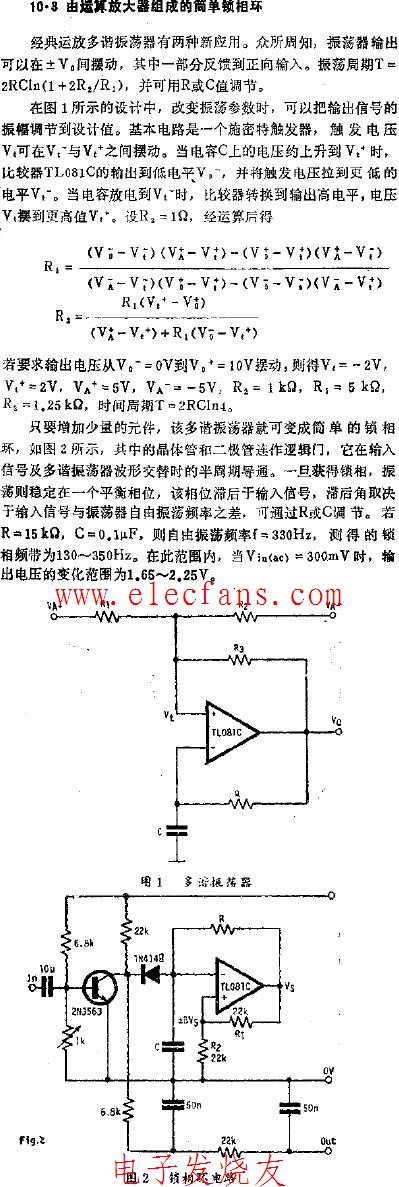

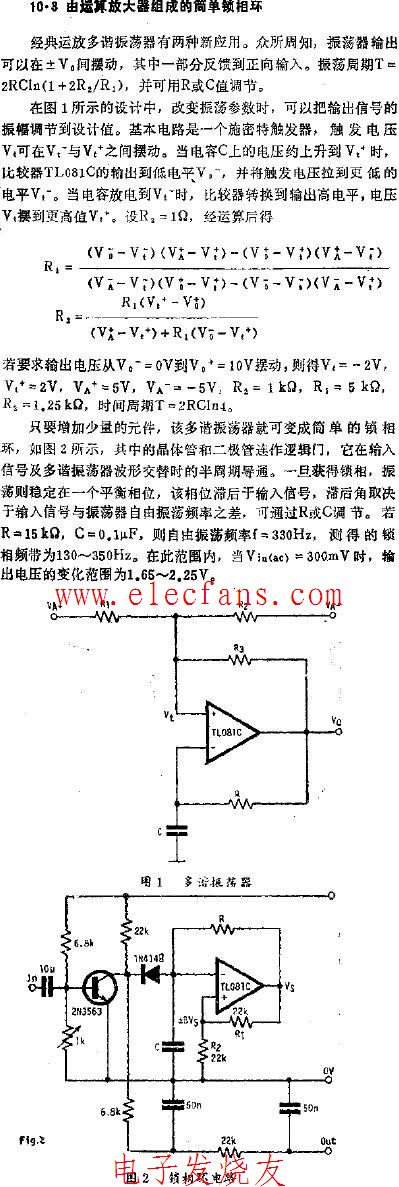

52 运算放大器组成的简单锁相环电路图

2008-02-25 21:50:11 3303

3303

锁相环电路图

2008-02-25 21:48:30 3757

3757

锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 4689

4689 锁相环CD4046的原理详细介绍及应用电路

锁相的意义是相位同步的自动控制,能够完成两

2006-04-17 21:18:11 4844

4844

CD4046锁相环的介绍和应用电路

锁相的意义是相位同步的自动控制,能够完

2006-04-16 17:58:36 12824

12824

德赢Vwin官网

App

德赢Vwin官网

App

评论