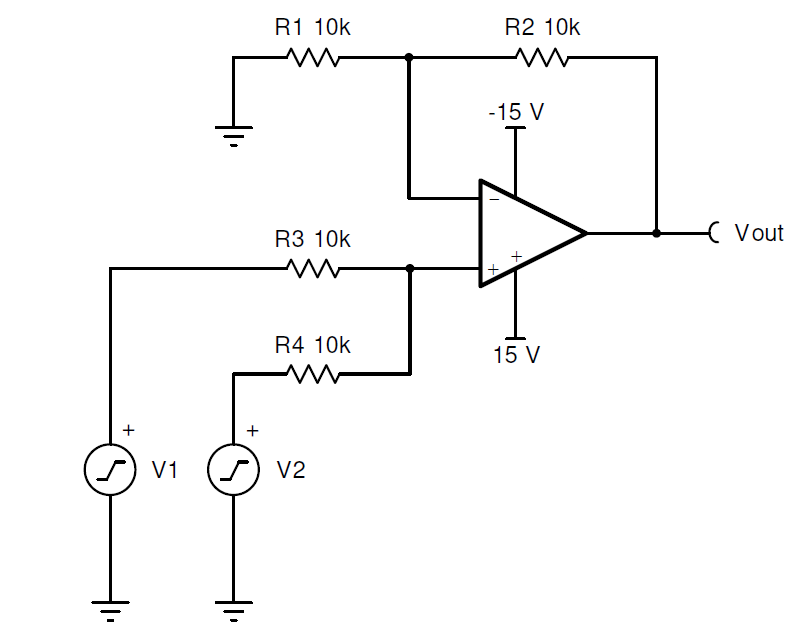

加法器:Summing Amplifier

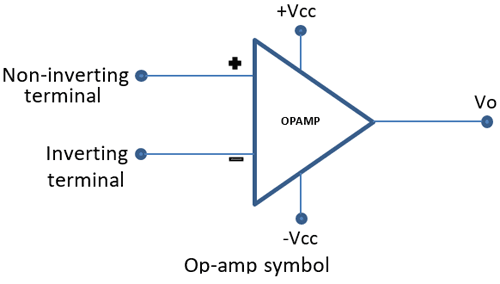

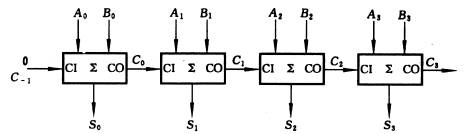

The summing amplifier, a special case of the inverting amplifier, is shown in Figure 4. The circuit gives an inverted output which is equal to the weighted algebraic sum of all three inputs. The gain of any input of this circuit is equal to the ratio of the appropriate input resistorto the feedback resistor, R4. Amplifier bandwidth may be calculated as in the inverting amplifier shown in Figure 1 by assuming the input resistor to be the parallel combination of R1, R2, and R3. Application cautions are the same as for the inverting amplifier. If an uncompensated amplifier is used, compensation is calculated on the basis of this bandwidth as is discussed in the section describing thesimple inverting amplifier. Theadvantage of this circuit is that there is no interaction between inputs and operations such as summing and weighted averaging are implemented very easily.

求和电路是反相放大器的一种特殊形式。如图4。其输出电压为3个输入电压加权代数和取反(因为其为反相电路,其每路的增益为负值——译者)。每路输入电压的增益等于其反馈电阻和输入电阻之比(取反——译者)。增益带宽的计算方式和反相放大电路相同,参见例1,将其输入电阻替换为R1、R2、R3的并联电阻值。应用上的注意事项和反相放大电路相同。如果使用了没有内部补偿功能的OP,应该在简单反相器的带宽的基础上计算补偿量。这个电路的特点在于:各个输入之间相互不影响,求和或者取平均的功能很容易就可以实现。

德赢Vwin官网 App

德赢Vwin官网 App

评论