LCD数显温度计

电路图

ICL7136 pdf datasheet

2008-11-07 21:30:21

本文是本系列的第四篇,本文主要介绍FPGA常用

运算模块-

除法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:20:45

924

924

今天来给大家简单介绍一下:

运算放大器的应用,

电路图+波形

图,一次性解决。

2023-05-12 09:02:26

2948

2948

NI Multisim 10经典教程分享--

除法与开平方

运算

电路

2023-02-08 09:18:28

689

689

FPGA中的硬件逻辑与软件程序的区别,相信大家在做

除法

运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间

除法

运算会占用较多的资源,

电路结构复杂,且通常无法在一个时钟周期内完成。因此FPGA实现

除法

运算并不是一个“/”号可以解决的。

2022-04-27 09:16:03

5168

5168

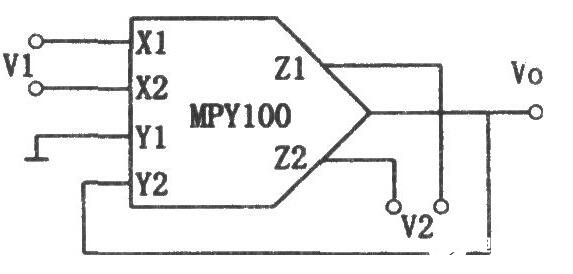

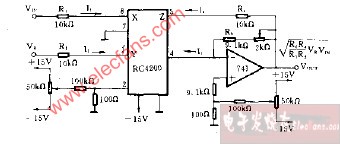

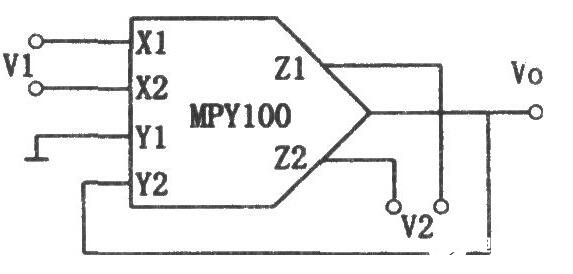

输入信号为V1、V2,输出Vo为Vo=10V2/V1。这种

除法器是将乘法器接在

运算放大器的反院回路组成的。V1的输入范围为-0.2V到10V,V2的输入范围为-10V到10V。

2019-12-31 14:12:44

15859

15859

FPGA中的硬件逻辑与软件程序的区别,相信大家在做

除法

运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间

除法

运算会占用较多的资源,

电路结构复杂,且

2018-05-18 01:15:00

3961

3961

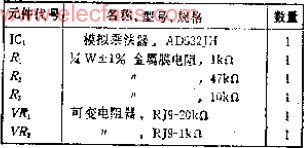

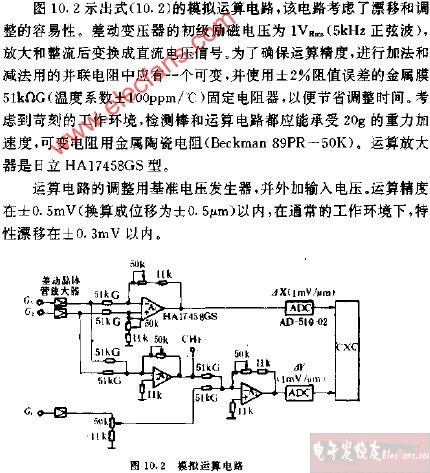

本文为大家带来九款不同的

除法

运算

电路设计方案,包括这九款模拟

电路设计的原理及设计过程。

2018-01-17 18:24:49

46006

46006

14.2

除法

运算因为ARM体系结构本身并不包含

除法

运算硬件,所以在ARM上实现

除法是十分耗时的。ARM指令集中没有直接提供

除法汇编指令,当代码中出现

除法

运算时,ARM编译器会调用C库函数(有符合

2017-10-17 17:22:29

5

5

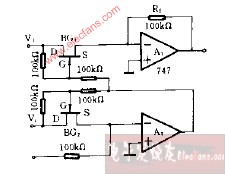

用于比率计算的

除法

运算

电路

电路的功能 本

电路是用X除输入信号Z

2010-05-08 15:29:01

1562

1562

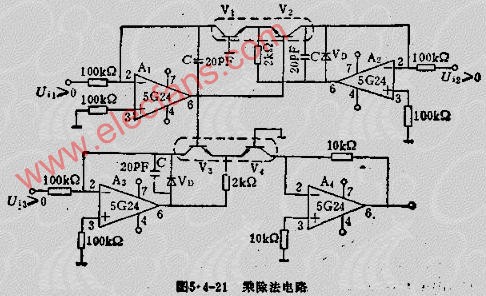

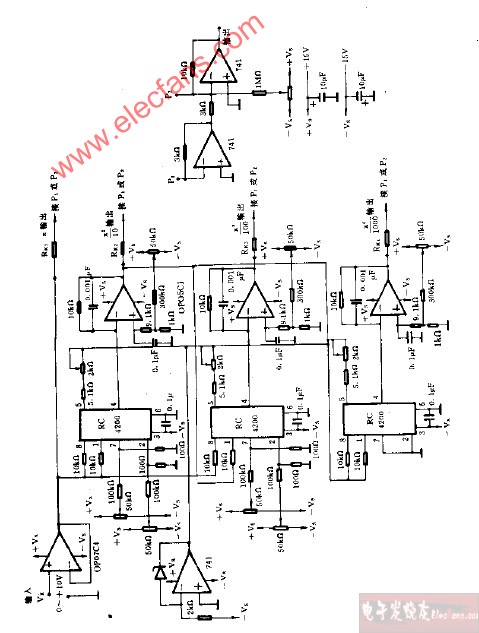

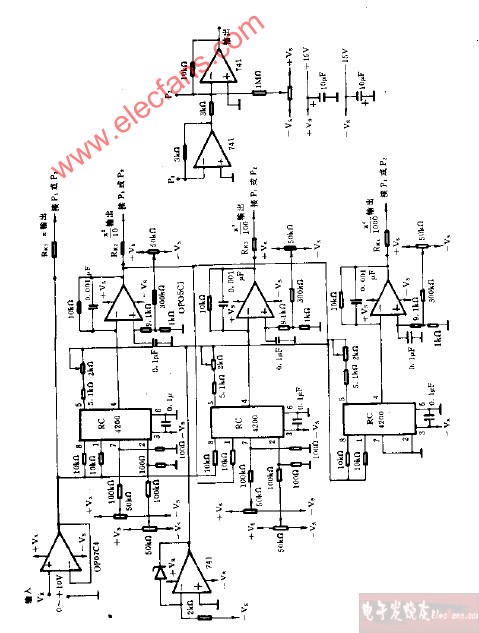

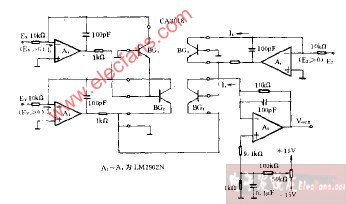

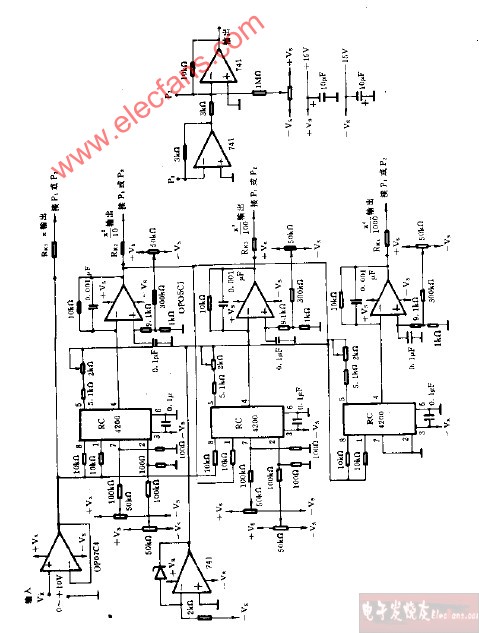

乘

除法

电路

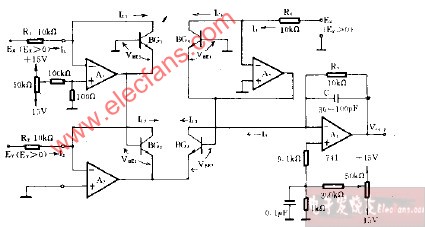

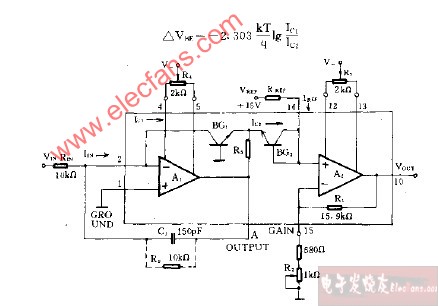

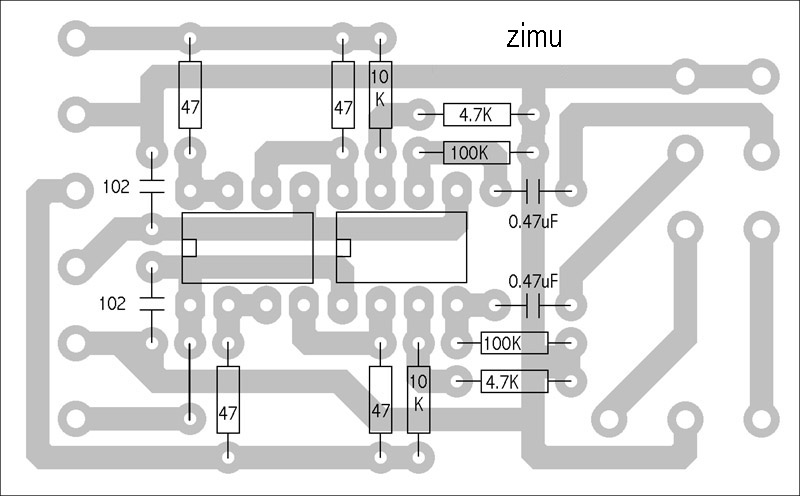

图5.4-21是乘

除法

运算实用

电路之一。 1、A

2010-04-26 16:11:49

16002

16002

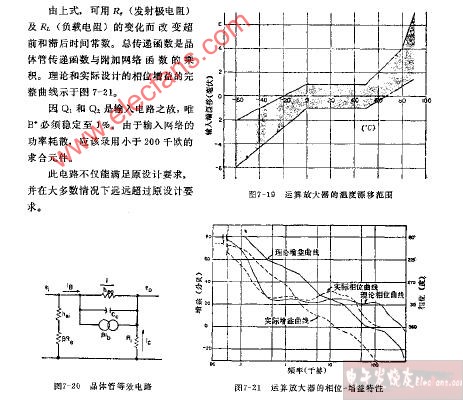

除法器对数

运算

电路的应用 由对数

电路实现

除法

运算的数学原理是:

2010-04-24 16:07:27

2366

2366

原码

除法

运算原理是什么? 两个原码表示的数相除时,商的符号由两数的符号按位相加求得,商的数值部分由两数的数值部分相除求得。 设有n位定

2010-04-13 11:15:45

11412

11412

并行

除法器 ,并行

除法器结构原理是什么? 1.可控加法/减法(CAS)单元 和阵列乘法器非常相似,阵列式

除法器也是一种并行

运算部件,

采用大规模集成

2010-04-13 10:46:30

14405

14405

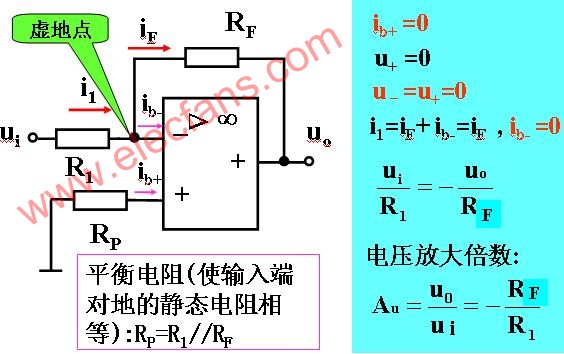

反相比例

运算放大

电路图

2010-04-13 10:29:38

37636

37636

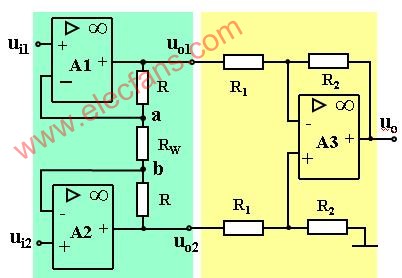

三相

运算放大

电路图

2010-04-13 10:27:35

2281

2281

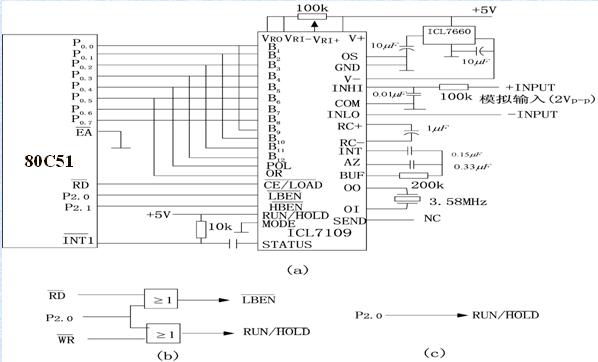

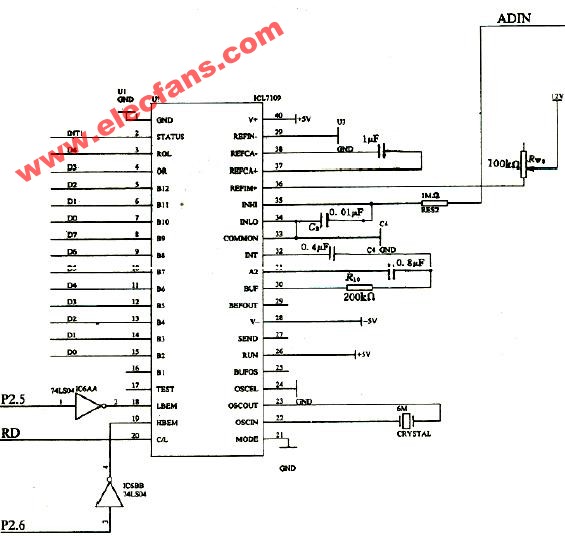

ICL7109与80C51的接口

电路图

2009-10-25 11:49:39

3794

3794

由

ICL7182构成的液晶条

图温度表

电路图

2009-07-23 17:16:17

716

716

由

ICL7182构成的液晶条

图电压表

电路图

2009-07-23 17:15:57

717

717

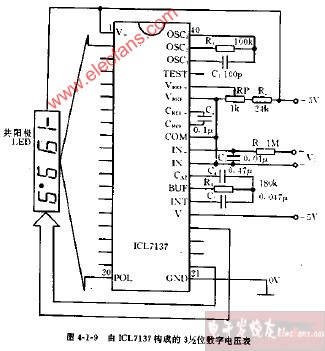

由

ICL7137构成的3,1 2位数字电压表

电路图

2009-07-23 17:15:38

1879

1879

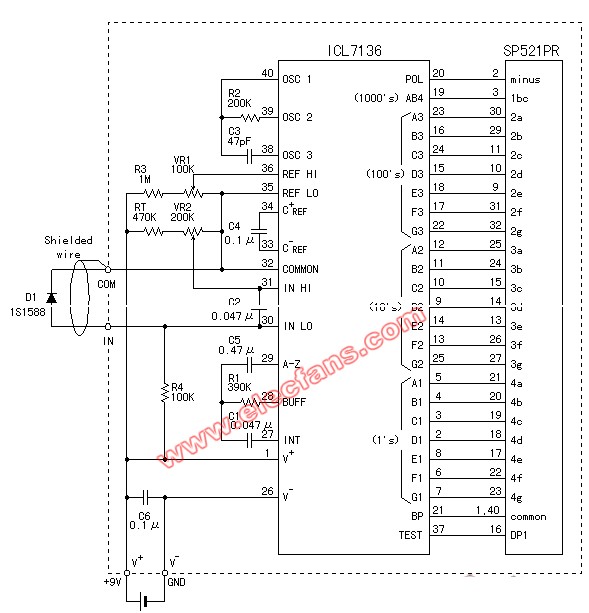

由

ICL7136构成的3,1 2位数字电压表

电路图

2009-07-23 17:15:13

2679

2679

由

ICL7129构成的4,1 2位数字电压表

电路图

2009-07-23 17:12:10

4523

4523

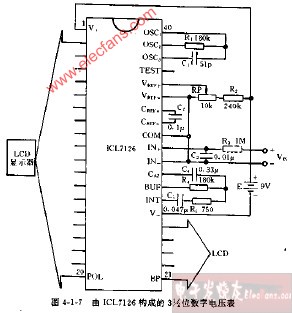

由

ICL7126构成的3,1 2位数字电压表

电路图

2009-07-23 17:11:18

2085

2085

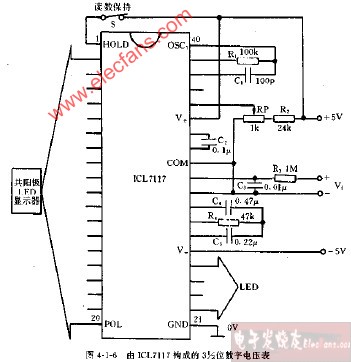

由

ICL7117构成的3,1 2位数字电压表

电路图

2009-07-23 17:10:55

1460

1460

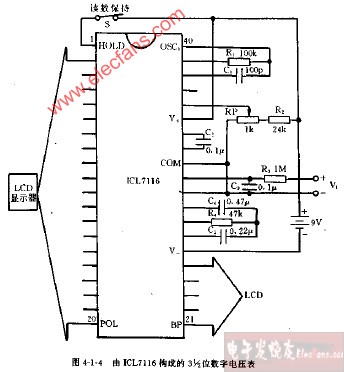

由

ICL7116构成的3,1 2位数字电压表

电路图

2009-07-23 17:10:33

1180

1180

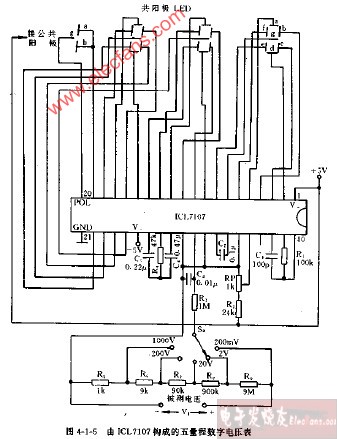

由

ICL7107构成的五量程位数字电压表

电路图

2009-07-23 17:10:09

2227

2227

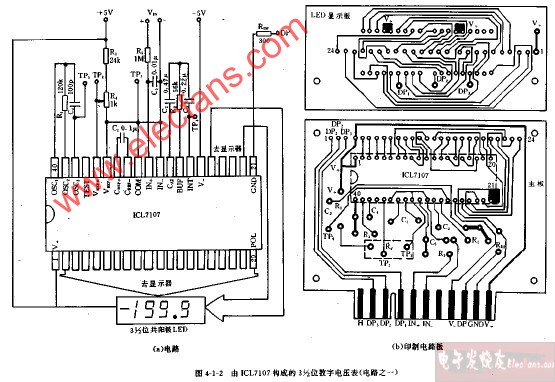

由

ICL7107构成的3,1 2位数字电压表

电路图(之一)

2009-07-23 17:09:48

1856

1856

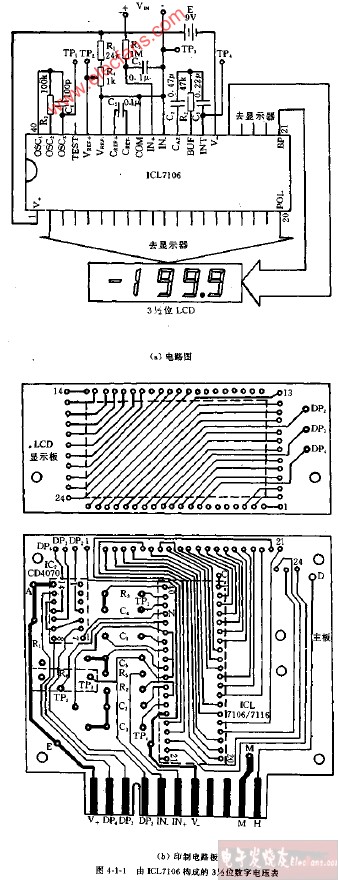

由

ICL7106构成的3,1 2位数字电压表

电路图

2009-07-23 17:09:19

2592

2592

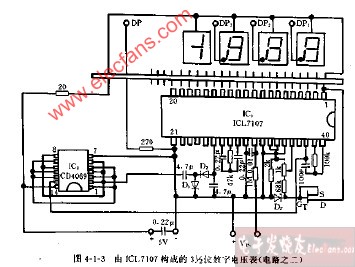

由

ICL7107构成的3,1 2位数字电压表

电路图(之二)

2009-07-23 17:08:38

2083

2083

采用

ICL8211和

ICL8212的电源 摘要:

ICL8211和

ICL8212是微功率的双极性单片集成

电路,主要用于精密电压检测和精密电压产生。

2009-07-20 15:15:37

1984

1984

运算型线性化

电路图

2009-07-20 12:22:49

508

508

运算型线性化

电路图

2009-07-20 12:22:47

342

342

平方

运算

电路图

2009-07-20 12:18:34

2582

2582

平方

运算

电路图

2009-07-20 12:16:02

3661

3661

平方根

运算

电路图

2009-07-20 12:15:39

1811

1811

除法

运算

电路图

2009-07-20 12:10:07

691

691

乘除

运算

电路图

2009-07-20 12:09:43

496

496

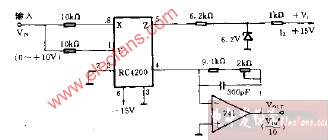

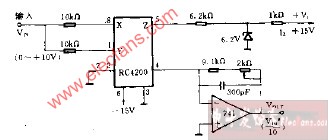

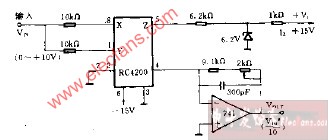

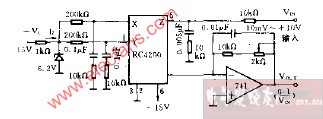

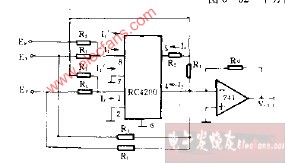

采用RC4200的4象限乘法

运算

电路图

2009-07-20 12:07:25

714

714

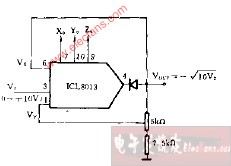

采用

ICL8013的平方根

运算

电路图

2009-07-20 12:07:00

825

825

采用

ICL8013的

除法

运算

电路图

2009-07-20 12:02:30

668

668

采用

ICL8013的

除法

运算

电路图

2009-07-20 12:02:08

610

610

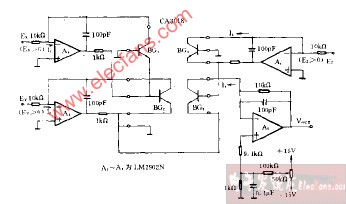

采用CA3018和运放构成的乘法

运算

电路图

2009-07-20 12:01:40

1265

1265

ICL8048的基本

电路图

2009-07-20 11:57:42

775

775

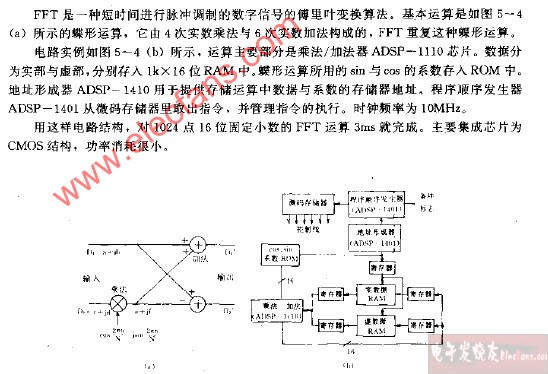

FFT(快速傅里叶变换)

运算器

电路图

2009-07-20 11:29:20

2026

2026

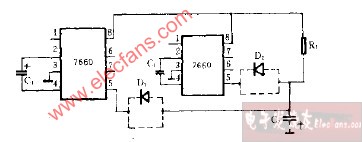

ICL7660片内串联稳压器

电路图

2009-07-17 11:36:35

1036

1036

运算型线性化

电路图

2009-07-17 11:35:19

402

402

平方

运算

电路图

2009-07-17 11:32:41

2990

2990

平方根

运算

电路图

2009-07-17 11:32:19

467

467

除法

运算

电路图

2009-07-17 11:26:48

3856

3856

乘除

运算

电路图

2009-07-17 11:26:22

423

423

采用RC4200的基本

电路图

2009-07-17 11:24:39

1800

1800

采用RC4200的4象限乘法

运算

电路图

2009-07-17 11:24:17

689

689

采用

ICL8013的平方根

运算

电路图

2009-07-17 11:23:54

1036

1036

采用CA3018和运放构成的乘法

运算

电路图

2009-07-17 11:23:08

3082

3082

ICL8048的基本

电路图

2009-07-17 11:22:22

1584

1584

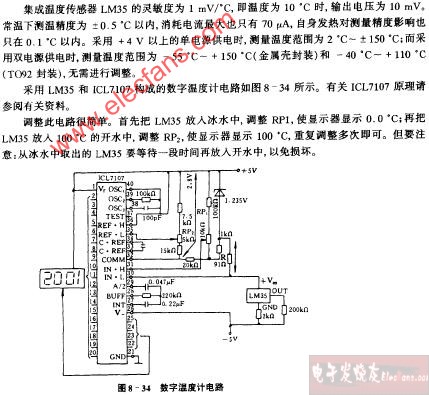

采用LM35和

ICL7107构成的数字温度计

电路图

2009-07-16 17:27:45

2837

2837

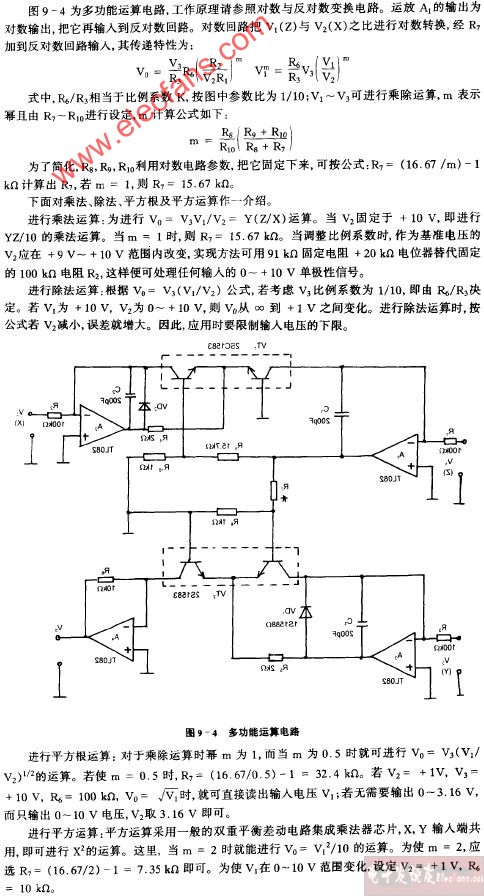

多功能

运算

电路图

2009-07-16 17:11:21

543

543

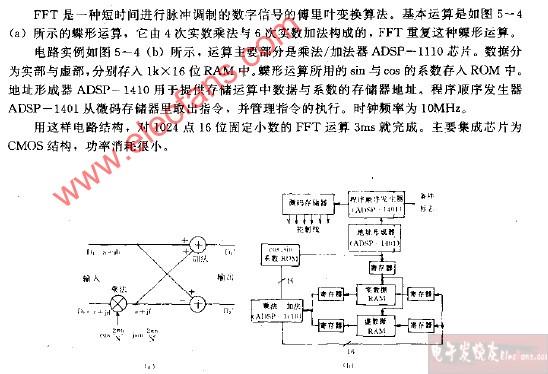

FFT(快速傅里叶变换)

运算器

电路图

2009-07-16 11:49:18

3981

3981

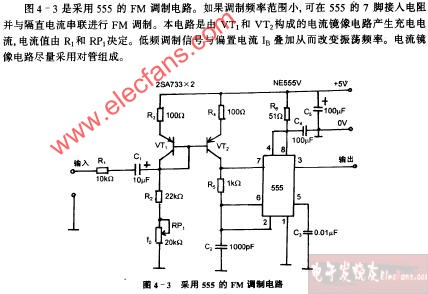

采用555的FM调制

电路图

2009-07-15 16:49:39

809

809

模拟

运算

电路图

2009-07-06 14:50:33

366

366

简化

运算放大器

电路图

2009-06-27 10:22:44

783

783

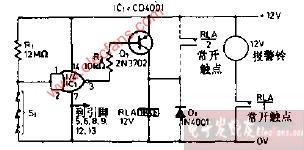

采用CMOS的断开报警

电路图

2009-06-10 08:33:04

1533

1533

运算放大器线性藕

电路图

2009-06-06 10:11:09

637

637

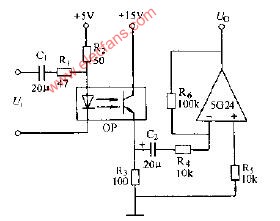

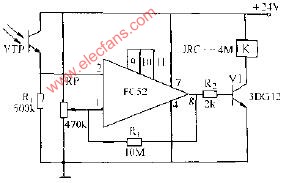

光控

运算放大器

电路图

2009-06-04 14:37:05

1118

1118

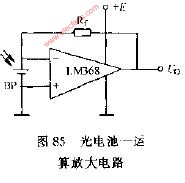

光电池-

运算放大

电路图

2009-06-04 13:49:47

642

642

光电池-

运算放大

电路图

2009-06-04 13:49:05

737

737

光电池-

运算放大

电路图

2009-06-04 13:48:32

2465

2465

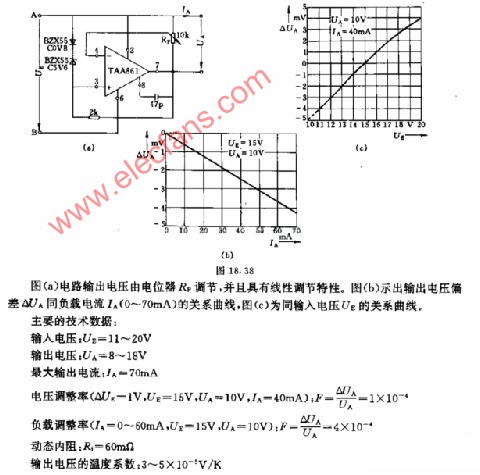

采用

运算放大器TAA861的恒压源

电路图

2009-05-13 21:46:07

2825

2825

运算放大器的凋零

电路图

2009-05-08 13:45:52

1001

1001

图8

ICL7135与8031的接口

电路

2009-03-14 14:29:31

3433

3433

The

ICL8013is a four quadrant analog multiplier whoseoutput is proportional to the algebraic

2009-01-06 16:48:58

18

18

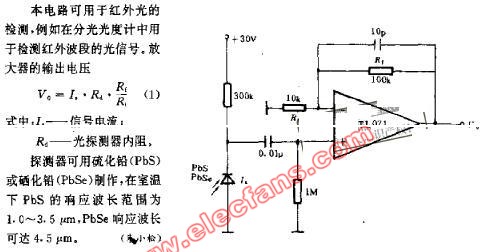

采用Pbs PbSe的测光

电路图

2008-12-24 21:58:31

1105

1105

ICL7109应用

电路图A/D

采用一片砌

ICL7109。

ICL7109为双积分型模数转换器,12位输出,

2008-12-01 17:06:56

5525

5525

用

ICL7136设计的LCD数显温度计

电路图

2008-11-07 21:26:00

5543

5543

ICL7107

电路图

2008-01-11 23:39:59

7800

7800

运算放大器

电路图大全

2007-09-29 21:31:29

3621

3621

IC扩流

电路图_音量补偿器

电路图_通用FET 输入

运算放大器

电路图最简单的cm

2007-09-29 20:54:57

1240

1240

运算放大器

电路图:包含

2007-09-13 14:07:11

1418

1418

德赢Vwin官网 App

德赢Vwin官网 App

硬声App

硬声App

5168

5168

15859

15859

3961

3961

46006

46006

5

5

11412

11412

14405

14405

1984

1984

18

18

评论