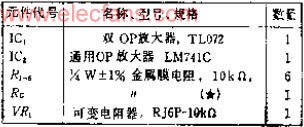

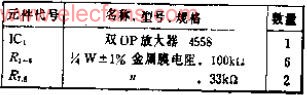

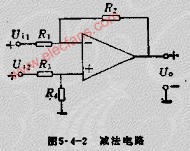

带输入缓冲的减法器电路

- 减法(8251)

相关推荐

顶层为原理图的能显示16进制减法计数器设计

)。(在图6-1中为KZ模块,其中Q(3:0)为数据输出信号,D(2:0)为输出位选通信号)。2.用VHDL设计一个16进制

减法器,并用ModelSim Simulator 仿真验证。3.用VHDL设计一

2009-10-11 08:51:38

FPGA常用运算模块-加减法器和乘法器

本文是本系列的第二篇,本文主要介绍FPGA常用运算模块-加

减法器和乘

法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:13:57

1336

1336

1336

1336

数字电路基础知识分享4

本小节将从这些逻辑器件,门

电路,触发器开始,搭建一些相对复杂点的功能

电路,比如加

法器和

减法器等。从这个过程中,体会一下如何从基本逻辑门开始,构建功能稍微复杂的

电路。

2023-05-04 15:23:43

373

373

373

373

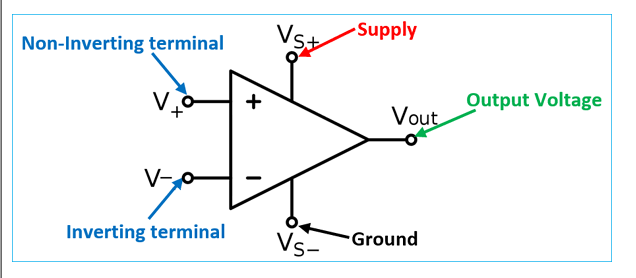

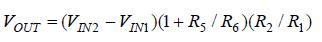

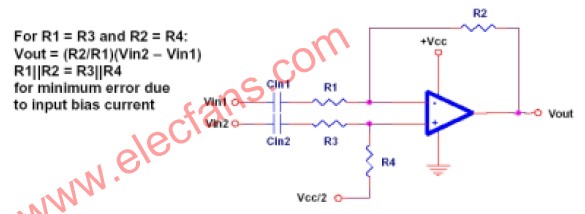

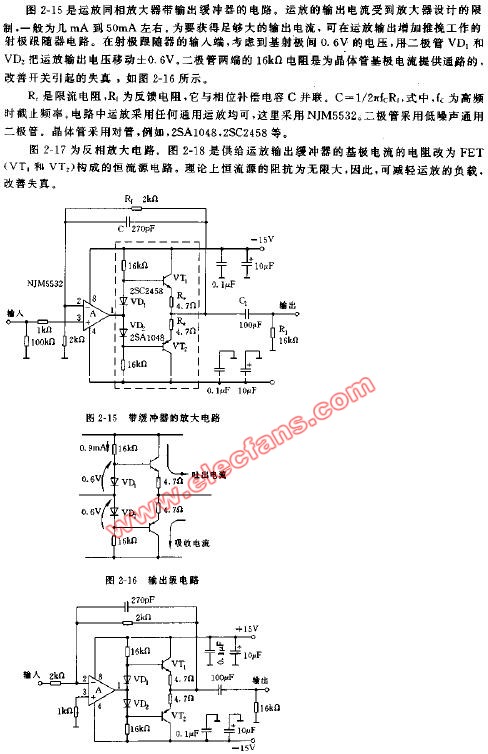

如何将运算放大器用作差分放大器查找电压值的电压差

在本教程中,我们将学习如何将运算放大器用作差分放大器来查找两个电压值之间的电压差。它也被称为电压

减法器。我们还将在面包板上尝试电压

减法器

电路,并检查

电路是否按预期工作。

2022-09-22 17:16:46

3722

3722

3722

3722

DSP48E1片的数据和控制输入提供算术和逻辑阶段

DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补

法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3

输入加

法器/

减法器或2

输入逻辑单元(参见图2-5)。使用2

输入逻辑单元时,不能使用乘

法器。

2022-01-21 14:14:26

842

842

842

842

计算机为什么要使用补码

,增加了计算的时间,能不能用加

法器实现

减法器的功能?这个实现的过程就用到了补码。 计算机为什么使用补码?采用补码可以简化计算机硬件

电路设计的复杂度。 对于有符号数,内存要区分符号位和数值位,要是能把符号位和数值位

2021-09-12 16:06:43

5873

5873

5873

5873

DSP48E1详解(2):简化DSP48E1片操作

DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补

法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3

输入加

法器/

减法器或2

输入逻辑单元(参见图2-5)。使用2

输入逻辑单元时,不能使用乘

法器。

2021-01-29 08:19:37

13

13

13

13

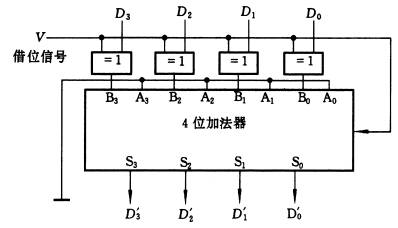

数字电路中加法器和减法器逻辑图分析

多位二进制

减法器,是由加法

电路构成的;在加法

电路的基础上,

减法与加法采用同一套

电路,实现加

减法共用。

2020-09-01 16:02:09

18552

18552

18552

18552

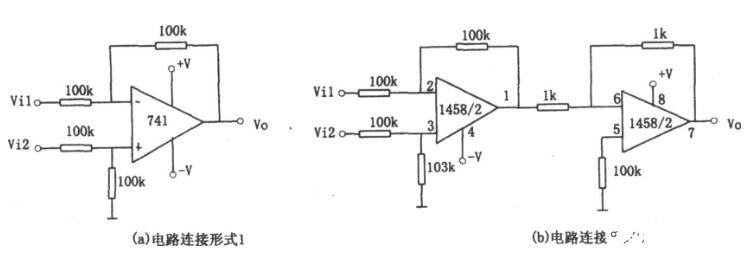

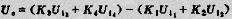

三款减法器电路图分享

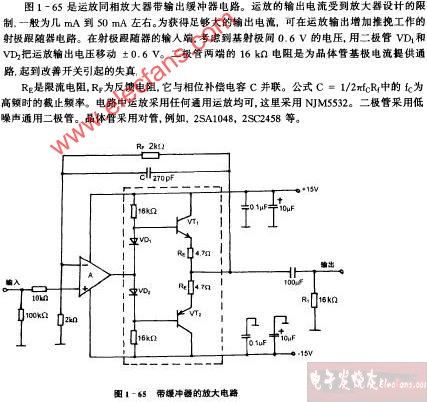

V0=Vi2-Vi1图中放大器的输出信号电压极性通常与

输入电压极性相同。如果要求反相输出,则采用图(b)所示

电路。其

输入输出关系为:Vo=Vi1-Vi2。

2019-12-31 14:22:49

36625

36625

36625

36625

一些基础的运用电路合集免费下载

本文档的一些基础的运用

电路合集免费下载包括了:反向放大器同向放大器加

法器

减法器积分

电路微分

电路电压转换成电流差分放大

电路电流转换成电压。

2019-11-12 08:00:00

37

37

37

37

关于运放电路分析和介绍

分析运放

电路的工作原理时,紧扣“虚短”和“虚断”两个概念,再结合

电路原理进行计算即可,非常方便,不需要记什么同向放大、反向放大,什么加

法器、

减法器、差分

输入等计算公式。

2019-10-25 11:29:48

11504

11504

11504

11504

运算放大器积分电路和斜坡发生器方程

积分器运算放大器产生的输出电压与

输入信号的幅度和持续时间成正比,可用作正反馈放大器或负反馈放大器的一部分或作为加

法器或

减法器类型的

电路,在

输入和反馈环路中仅使用纯电阻。

2019-06-26 09:28:12

42334

42334

42334

42334

12位加法器的实验原理和设计及脚本及结果资料说明

加

法器是数字系统中的基本逻辑器件。例如:为了节省资源,

减法器和硬件乘

法器都可由加

法器来构成。但宽位加

法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

2019-04-15 08:00:00

4

4

4

4

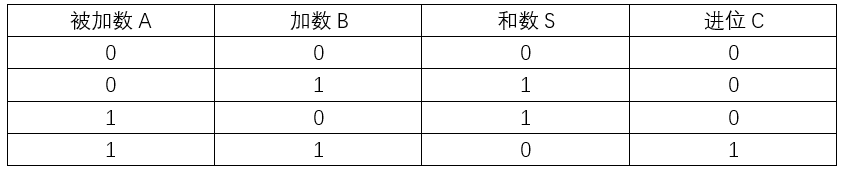

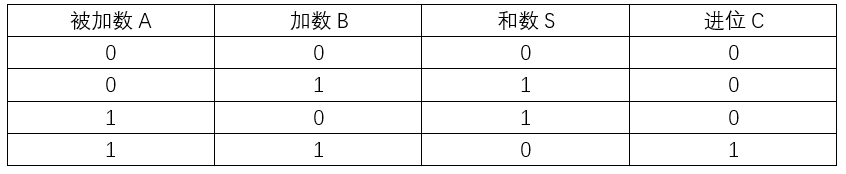

加法器与减法器_反相加法器与同相加法器

加

法器是产生数的和的装置。加数和被加数为

输入,和数与进位为输出的装置为半加器。

减法

电路是基本集成运放

电路的一种,

减法

电路可以由反相加法

电路构成,也可以由差分

电路构成。基本集成运放

电路有加、减、积分和微分等四种运算。一般是由集成运放外加反馈网络所构成的运算

电路来实现。

2017-08-16 11:09:48

157219

157219

157219

157219

同相加法器电路原理与同相加法器计算

同相加

法器

输入阻抗高,输出阻抗低 反相加

法器

输入阻抗低,输出阻抗高.加

法器是一种数位

电路,其可进行数字的加法计算。当选用同相加

法器时,如A

输入信号时,因为是同相加

法器,

输入阻抗高,这样信号不太容易流入加

法器,反而更容易流入B端。

2016-09-13 17:23:33

54133

54133

54133

54133

本的二进制加法/减法器,本的二进制加法/减法器原理

本的二进制加法/

减法器,本的二进制加法/

减法器原理 两个二进制数字Ai,Bi和一个进位

输入Ci相加,产生一个和输出Si,以及一个进位输

2010-04-13 11:11:55

5077

5077

5077

5077

并行除法器,并行除法器结构原理是什么?

并行除

法器,并行除

法器结构原理是什么? 1.可控加法/

减法(CAS)单元 和阵列乘

法器非常相似,阵列式除

法器也是一种并行运算部件,采用大规模集成

2010-04-13 10:46:30

14405

14405

14405

14405

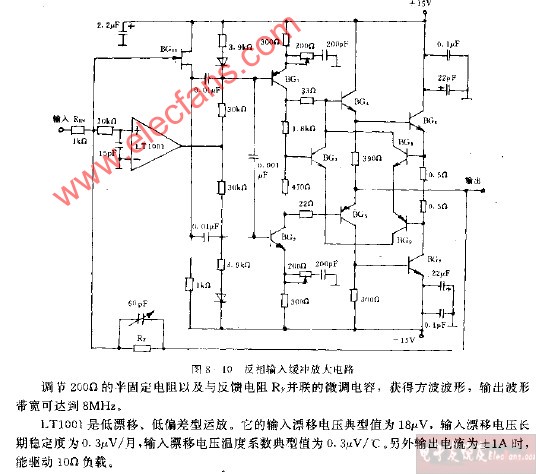

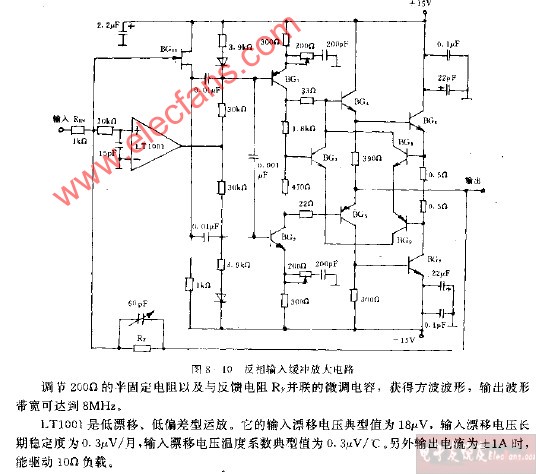

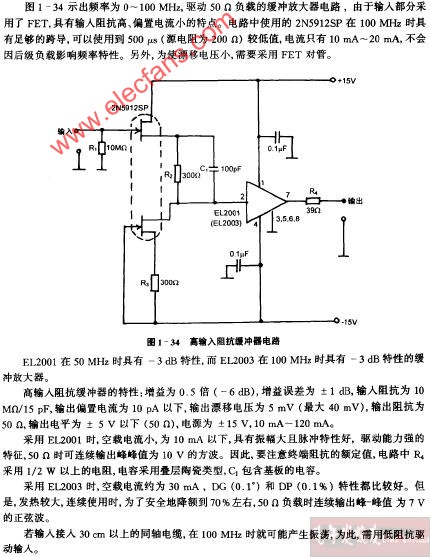

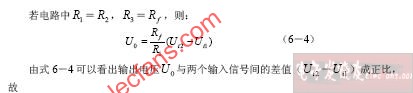

使用三运放搭建输入缓冲级和输出级电路

使用三运放搭建

输入

缓冲级和输出级

电路传统IA使用三运放搭建

输入

缓冲级和输出级

电路(图2)。

输入

缓冲级

电路提供全差分增益、单位共模增益和高阻

输入,差分

2009-12-07 22:47:26

1789

1789

1789

1789

含运算放大器的电路的分析

1.运放的传输特性2.比例器、加

法器、

减法器、跟随器等运算

电路3.含理想运放的运算

电路的分析计算 难点 熟练计算含理想运放的思路 运放的

电路模型

2009-07-08 09:09:19

74

74

74

74

减法运算

减法运算 同加法运算一样,

减法运算可采用

减法器来实现。半减器和全减器的设计方法和步骤与设计加

法器相同。实用上,为了简化系统结构,通常不另外设计减

2009-04-07 10:38:39

12577

12577

12577

12577

德赢Vwin官网 App

德赢Vwin官网 App

评论