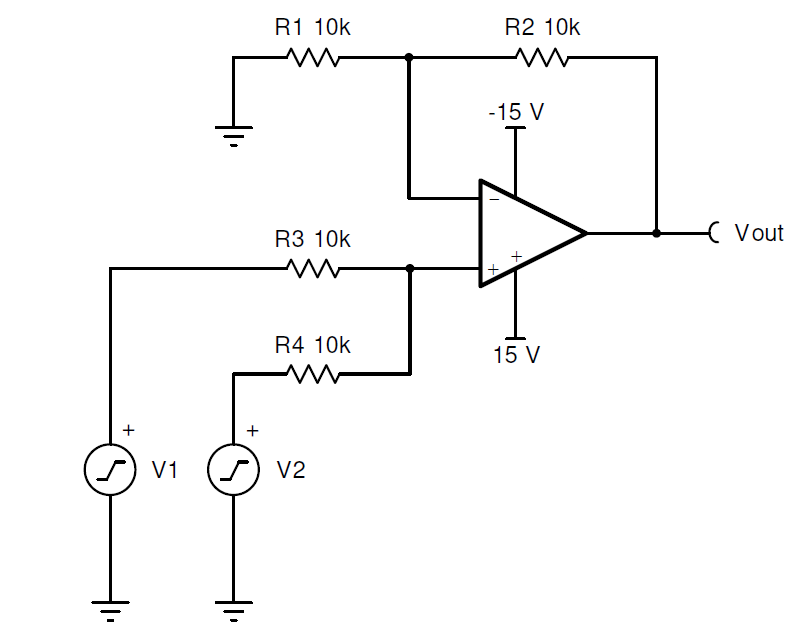

运算放大加法器电路图

- 放大(35939)

- 加法器(29467)

- 运算(25601)

相关推荐

初级数字IC设计-加法器

加法器(Adder)** 是非常重要的,它不仅是其它复杂算术

运算的基础,也是** CPU **中** ALU **的核心部件(全加器)。

2023-10-09 11:14:14

433

433

433

433

半加法器的工作原理及电路解析

半

加法器是一种执行二进制数相加的数字

电路。它是最简单的数字

加法器,您只需使用两个逻辑门即可构建一个;一个异或门和一个 AND 门。

2023-06-29 14:35:25

1320

1320

1320

1320

全加法器的工作原理和电路解析

加法器可以是半

加法器或全

加法器。不同之处在于半

加法器仅用于将两个 1 位二进制数相加,因此其总和只能从 0 到 2。为了提高这种性能,开发了FullAdder。它能够添加三个 1 位二进制数,实现从 0 到 3 的总和范围,可以用两个输出位 (“11”) 表示。

2023-06-29 14:27:35

1542

1542

1542

1542

实用电路分享-同相加法器

同相

加法器(又称为同相组合器、输入能量合成器、同相求和器)是一种电子

电路器件,主要应用在通信、信号处理、调试和测量等领域。

2023-06-13 14:53:32

3644

3644

3644

3644

加法器的原理及采用加法器的原因

有关

加法器的知识,

加法器是用来做什么的,故名思义,

加法器是为了实现

加法的,它是一种产生数的和的装置,那么

加法器的工作原理是什么,为什么要采用

加法器,下面具体来看下。

2023-06-09 18:04:17

2245

2245

2245

2245

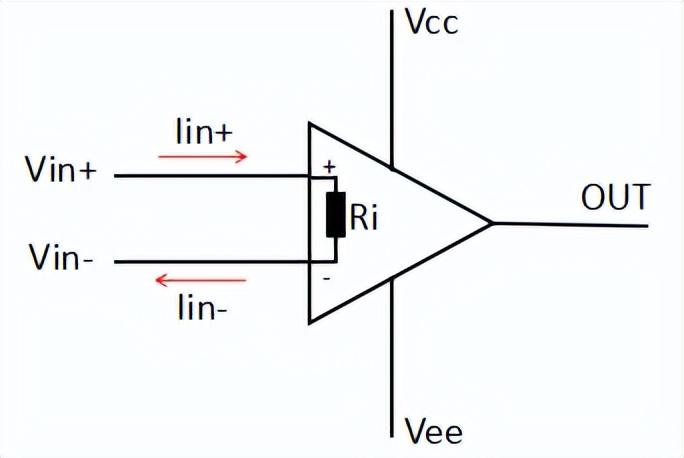

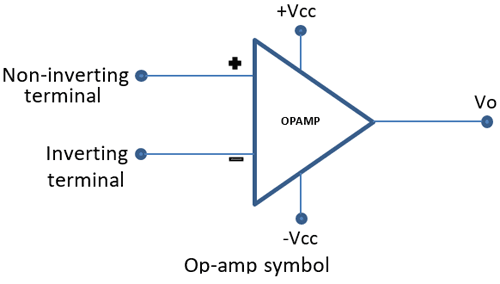

运算放大器的常用电路图及其工作原理

今天我们介绍一下基于

运算放大器的反相

放大器、同相

放大器、

加法器、减

法器的

电路图及其工作原理。要读懂

运算放大器的常用

电路图,理解其工作原理,首先要了解

运算放大器的两个重要概念:虚短和虚断。前面我们已经对虚短和虚断的概念进行了简单的介绍,感兴趣的小伙伴可以去考个古。

2023-02-24 16:10:00

6845

6845

6845

6845

如何使用LM358运算放大器来演示加法器电路

运算放大器(Opamp)有许多有趣的应用,我们已经使用

运算放大器创建了许多

电路。今天我们将研究

运算放大器的另一个应用,即添加两个或多个输入电压,该

电路称为求和

放大器或

运算放大器

加法器。在这里,我们将使用 LM358

运算放大器来演示

加法器

电路。

2022-11-11 15:29:29

7919

7919

7919

7919

超前进位加法器是如何实现记忆的呢

行波进位

加法器和超前进位

加法器都是

加法器,都是在逻辑

电路中用作两个数相加的

电路。我们再来回顾一下行波进位

加法器。

2022-08-05 16:45:00

639

639

639

639

计算机组成原理、数字逻辑之加法器详解

问题咨询及项目源码下载请加群:群名:IT项目交流群群号:245022761一、

加法器的意义

加法器是计算机中的基础硬件,了解

加法器不仅能够揭开计算机的本质,也能对计算机的数制

运算产生深刻的理解。二、半

2021-11-11 12:06:03

20

20

20

20

反相加法器原理图与电路图资料下载

德赢Vwin官网 网为你提供反相

加法器原理

图与

电路图资料下载的电子资料下载,更有其他相关的

电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-24 08:47:52

14

14

14

14

加法器工作原理_加法器逻辑电路图

。在电子学中,

加法器是一种数位

电路,其可进行数字的

加法计算。三码,主要的

加法器是以二进制作

运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

2021-02-18 14:40:31

29303

29303

29303

29303

数字电路中加法器和减法器逻辑图分析

多位二进制减

法器,是由

加法

电路构成的;在

加法

电路的基础上,减法与

加法采用同一套

电路,实现加减法共用。

2020-09-01 16:02:09

18552

18552

18552

18552

加法器原理

。在电子学中,

加法器是一种数位

电路,其可进行数字的

加法计算。三码,主要的

加法器是以二进制作

运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

2019-06-19 14:20:39

23685

23685

23685

23685

加法器功能

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

2019-06-19 14:19:17

6914

6914

6914

6914

12位加法器的实验原理和设计及脚本及结果资料说明

加法器是数字系统中的基本逻辑器件。例如:为了节省资源,减

法器和硬件乘

法器都可由

加法器来构成。但宽位

加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

2019-04-15 08:00:00

4

4

4

4

怎么设计一个32位超前进位加法器?

最近在做基于MIPS指令集的单周期CPU设计,其中的ALU模块需要用到

加法器,但我们知道普通的

加法器是串行执行的,也就是高位的

运算要依赖低位的进位,所以当输入数据的位数较多时,会造成很大的延迟

2018-07-09 10:42:00

18610

18610

18610

18610

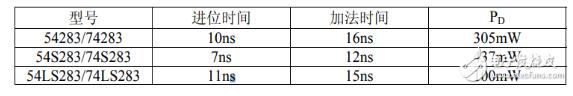

加法器芯片74ls283中文资料汇总(74ls283引脚图及功能_极限值及应用电路)

本文主要详解

加法器芯片74ls283中文资料汇总,首先介绍了74ls283引脚

图及功能,其次介绍了74ls283逻辑功能

图及极限值,最后介绍了两款基于

加法器芯片74ls283的应用

电路图,具体的跟随小编一起来了解一下。

2018-05-29 16:17:55

254409

254409

254409

254409

加法器内部电路原理

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2018-01-29 11:28:26

79946

79946

79946

79946

反相加法器电路与原理

加法器是为了实现

加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2018-01-29 10:49:50

30686

30686

30686

30686

加法器电路设计方案汇总(八款模拟电路设计原理详解)

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,

加法器是一种数位

电路,其可进行数字的

加法计算。

2018-01-17 10:42:03

134108

134108

134108

134108

八位加法器仿真波形图设计解析

8位全加器可由2个4位的全加器串联组成,因此,先由一个半加器构成一个全加器,再由4个1位全加器构成一个4位全加器并封装成元器件。

加法器间的进位可以串行方式实现,即将低位

加法器的进位输出cout与相临的高位

加法器的最低进位输入信号cin相接最高位的输出即为两数之和。

2017-11-24 10:01:45

27671

27671

27671

27671

音频运放加法器电路_njm4558 音频运放电路

在电子学中,

加法器是一种数位

电路,其可进行数字的

加法计算。

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2017-08-16 12:06:45

16643

16643

16643

16643

加法器与减法器_反相加法器与同相加法器

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。减法

电路是基本集成运放

电路的一种,减法

电路可以由反相

加法

电路构成,也可以由差分

电路构成。基本集成运放

电路有加、减、积分和微分等四种

运算。一般是由集成运放外加反馈网络所构成的

运算

电路来实现。

2017-08-16 11:09:48

157219

157219

157219

157219

同相加法器电路图_反相加法器电路图_运放加法器电路图解析

在电子学中,

加法器是一种数位

电路,其可进行数字的

加法计算。

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

2017-08-16 10:21:31

143816

143816

143816

143816

加法器是什么?加法器的原理,类型,设计详解

加法器是为了实现

加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

2017-06-06 08:45:01

22064

22064

22064

22064

同相加法器电路原理与同相加法器计算

同相

加法器输入阻抗高,输出阻抗低 反相

加法器输入阻抗低,输出阻抗高.

加法器是一种数位

电路,其可进行数字的

加法计算。当选用同相

加法器时,如A输入信号时,因为是同相

加法器,输入阻抗高,这样信号不太容易流入

加法器,反而更容易流入B端。

2016-09-13 17:23:33

54133

54133

54133

54133

基于选择进位32位加法器的硬件电路实现

为了缩短

加法

电路运行时间,提高FPGA运行效率,利用选择进位算法和差额分组算法用硬件

电路实现32位

加法器,差额分组中的

加法单元是利用一种改进的超前进位算法实现,选择进位算

2013-09-18 14:32:05

33

33

33

33

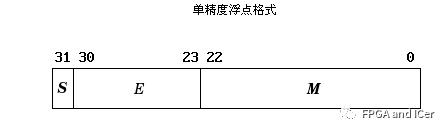

FPU加法器的设计与实现

浮点

运算器的核心

运算部件是浮点

加法器,它是实现浮点指令各种

运算的基础,其设计优化对于提高浮点

运算的速度和精度相当关键。文章从浮点

加法器算法和

电路实现的角度给出设计

2012-07-06 15:05:42

47

47

47

47

一款32位嵌入式CPU的定点加法器设计

根据一款32位嵌入式CPU的400MHz主频的要求,结合该CPU五级流水线结构,并借鉴各种算法成熟的

加法器,提出了一种

电路设计简单、速度快、功耗低、版图面积小的32位改进定点

加法器

2010-07-19 16:10:03

17

17

17

17

加法器和乘法器简介及设计

大多数数字功能可分为:数据通道、储存器、控制单元、I/O。

加法器和乘

法器属于数据通道部分。 一般对数据通道有如下要求:首先是规整性以优化版图,其次是局域性(时间

2010-05-25 17:43:34

6279

6279

6279

6279

多位快速加法器的设计

摘要:

加法

运算在计算机中是最基本的,也是最重要的

运算。传统的快速

加法器是使用超前进位

加法器,但其存在着

电路不规整,需要长线驱动等缺点。文章提出了采用二叉树法设

2010-05-19 09:57:06

62

62

62

62

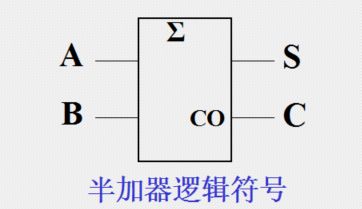

计算机常用的组合逻辑电路:加法器

计算机常用的组合逻辑

电路:

加法器一、

加法器1.半加器: 不考虑进位输入时,两个数码X n和Y n相加称为半加。设半加和为H n ,则H n 的

2010-04-15 13:48:11

5885

5885

5885

5885

十进制加法器,十进制加法器工作原理是什么?

十进制

加法器,十进制

加法器工作原理是什么? 十进制

加法器可由BCD码(二-十进制码)来设计,它可以在二进制

加法器的基础上加上适当的“校正”逻辑来实现,该校正逻

2010-04-13 10:58:41

12142

12142

12142

12142

加法器原理(16位先行进位)

加法器原理(16位先行进位) 这个

加法器写的是一波三折啊,昨天晚上花了两三个小时好不容易写完编译通过了,之后modelsim莫

2010-03-08 16:52:27

10796

10796

10796

10796

加法器:Summing Amplifier

加法器:Summing Amplifier The summing amplifier, a special case of the inverting amplifier, is shown in Figure 4. The circuit gives an

2009-05-16 12:38:34

2486

2486

2486

2486

性能改进的1 6 位超前进位加法器

加法

运算是最重要最基本的

运算, 所有的其他基本算术

运算, 减、 乘、 除、 模乘

运算最终都能归结为

加法

运算。 在不同的场合使用的

加法器对其要求也不同, 有的要求

2009-04-08 15:15:12

41

41

41

41

超前进位集成4(四)位加法器74LS283

超前进位集成4位

加法器74LS283 由于串行进位

加法器的速度受到进位信号的限制,人们又设计了一种多位数超前进位

2009-04-07 10:36:35

26072

26072

26072

26072

第二十讲加法器和数值比较器

第二十讲

加法器和数值比较器 6.6.1

加法器一、半加器1.含义 输入信号:加数Ai,被加数Bi 输出信号:本位和Si,向高位

2009-03-30 16:24:54

4993

4993

4993

4993

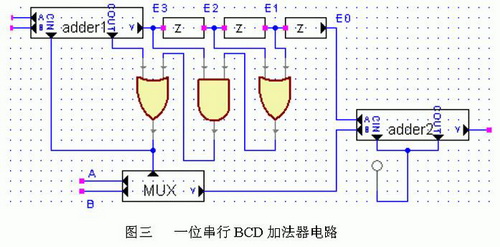

一位串行BCD加法器电路

图三所示为一位串行BCD

加法器。它是以牺牲速度以达到减少硬件逻辑门的目的,这种

电路在对频率要求不高的系统中非常之适用。其中ADDER1、ADDER2均为一位全加器。ADDER1 做主

运算器,

2009-03-28 16:36:21

3233

3233

3233

3233

德赢Vwin官网 App

德赢Vwin官网 App

评论