他方面的损耗,反而会引起更严重的EMI问题,导致整个系统不能稳定工作。所以需要在减少MOSFET的损耗的同时需要兼顾模块电源的EMI性能。

2017-12-24 08:36:53 16897

16897

瑞萨电子开发第三代车载SJ-MOSFET,计划1~2年内开始量产。该器件降低了导通电阻和EMI(电磁噪声)...

2013-05-31 09:22:20 1467

1467 简化的MOSFET等效电路MOSFET开通(turn on)过程MOSFET损耗——Rds和Rg电阻损耗Di

2017-10-31 15:43:38 21569

21569

,反而会引起更严重的EMI问题,导致整个系统不能稳定工作。所以需要在减少MOSFET的损耗的同时需要兼顾模块电源的EMI性能。

2023-04-18 09:22:02 1251

1251 本文主要阐述了MOSFET在模块电源中的应用,分析了MOSFET损耗特点,提出了优化方法;并且阐述了优化方法与EMI之间的关系。

2023-08-17 09:16:30 1297

1297

正确的二极管外,设计人员还能够通过调节栅极驱动导通源阻抗来控制Eon损耗。降低驱动源阻抗将提高IGBT或MOSFET的导通di/dt及减小Eon损耗。Eon损耗和EMI需要折中,因为较高的di/dt 会

2018-08-27 20:50:45

针对特定SMPS应用中的IGBT 和 MOSFET进行性能比较,确定关键参数的范围还是能起到一定的参考作用。本文将对一些参数进行探讨,如硬开关和软开关ZVS(零电压转换) 拓扑中的开关损耗,并对电路

2021-06-16 09:21:55

IGBT组合封装在一起。 除了选择正确的二极管外,设计人员还能够通过调节栅极驱动导通源阻抗来控制Eon损耗。降低驱动源阻抗将提高IGBT或MOSFET的导通di/dt及减小Eon损耗。Eon损耗和EMI

2020-06-28 15:16:35

MOSFET功率损耗的详细计算

2023-09-28 06:09:39

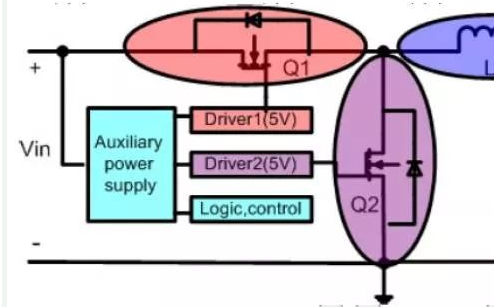

提高电源的开关和导通损耗。此外,它还会提高电磁干扰的噪声水平,从而使设计出的产品达不到理想的性能。若要最大限度降低电路板布局带来的影响,设计人员必须确保通过将驱动和MOSFET尽可能地背靠背放置,从而

2019-05-13 14:11:31

内部二极管的反向恢复时间trr高速化的ROHM SJ-MOSFET。PrestoMOS的FN系列与标准型AN系列相比,trr速度提高至约1/5。同时,反向恢复电流Irr也降低至约1/3。这些特性的提升

2018-11-28 14:27:08

MOSFET较小的栅极电阻可以减少开通损耗吗?栅极电阻的值会在开通过程中影响与漏极相连的二极管吗?

2023-05-16 14:33:51

的SiC,可使用更小的电感器,仍能达到以前相同的电感器纹波电流要求。在OBC系统中使用SiC MOSFET的好处是能够以更高的频率进行开关,功率密度更高,能效更高,EMI性能得到改善以及系统尺寸减小

2022-05-30 10:01:52

电机效率的影响因素降低电机损耗的关键制造技术

2021-01-26 07:49:16

使用绝缘栅双极晶体管(IGBT)。但随着半导体技术的进步,碳化硅 (SiC) 金属氧化物半导体场效应晶体管 (MOSFET) 能够以比 IGBT 更高的频率进行开关,通过降低电阻和开关损耗来提高效率

2022-11-02 12:02:05

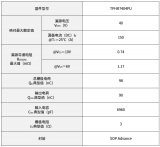

降低電源中的EMI

2021-08-25 17:11:19

要有深入了解,才能有利于理解和分析相应的问题。 高压MOSFET原理与性能分析 在功率半导体器件中,MOSFET以高速、低开关损耗、低驱动损耗在各种功率变换,特别是高频功率变换中起着重要作用。在低压

2023-02-27 11:52:38

B1M080120HC是一款碳化硅 MOSFET 具有导通电阻低,开关损耗小的特点,可降低器件损耗,提升系统效率,更适合应用于高频电路。降低器件损耗,提升系统 EMI 表现。在新能源汽车电机控制器

2021-11-10 09:10:42

在LED光通量有关的一些小知识点。在实际应用中这些概念将帮助开发者对于LED产品的性能进行提升,并提供一些能够小错误的快速修复。希望大家在阅读过本文之后能够有所收获。

2020-11-02 08:53:05

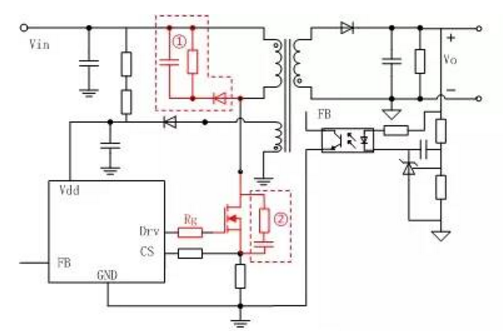

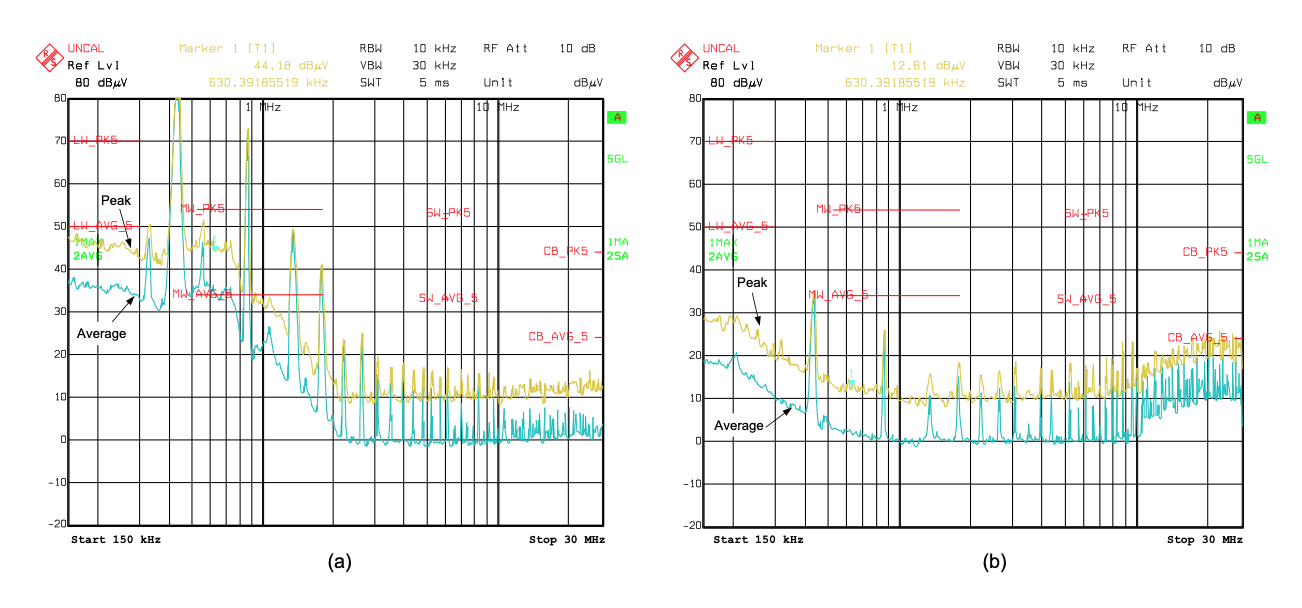

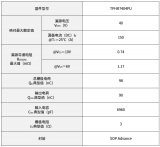

LED照明电路(临界模式PFC+DC/DC):利用MOSFET提升效率并降低噪声的案例下面的电路摘自实际LED照明电路的相关部分。该LED驱动电路是DC/DC转换器通过临界模式(BCM)的PFC向

2022-04-09 13:36:25

关断器件。这会大大延迟关断,从而增加MOSFET的功率损耗,降低转换效率。此外,杂散电感可导致电路中出现超过器件电压额定值的电压尖峰,从而导致出现故障。 旨在降低电阻和提升热性能的封装改进还可极大

2018-09-12 15:14:20

提升导通能量,当栅极电阻降低时,导通能量也随之降低。图2 Eon和Rg的关系曲线当横跨栅极电阻器的压降超过了半桥转换器上MOSFET的阈值电压,就会发生寄生导通,即米勒效应。此时,反向恢复能量(Err

2019-07-09 04:20:19

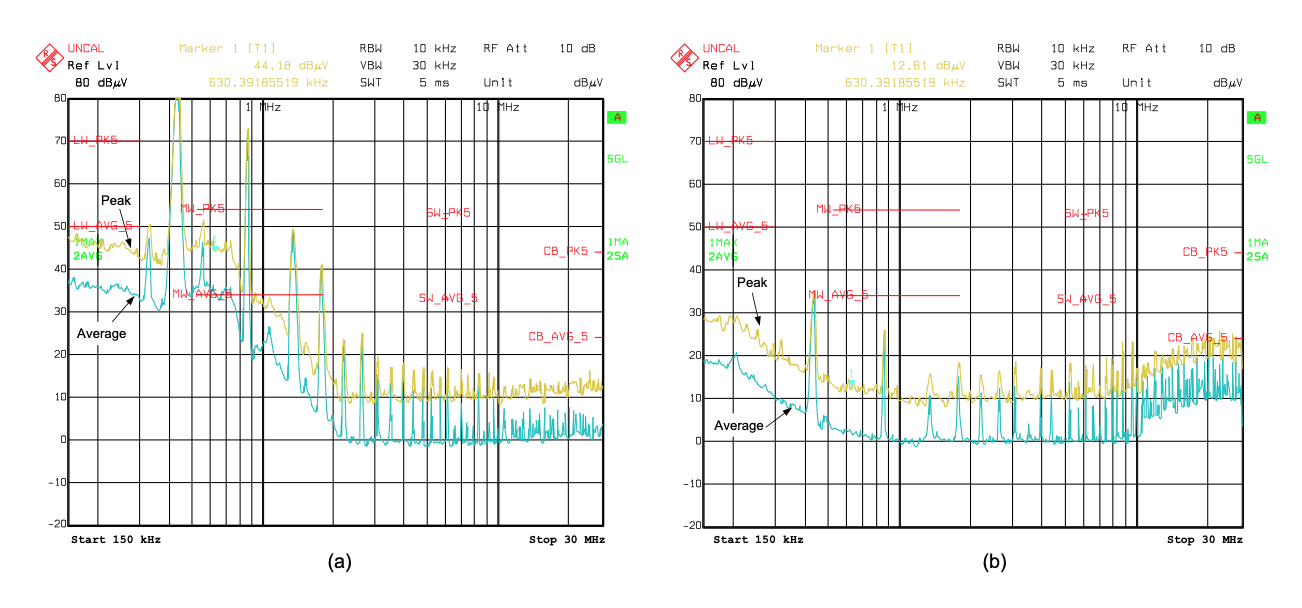

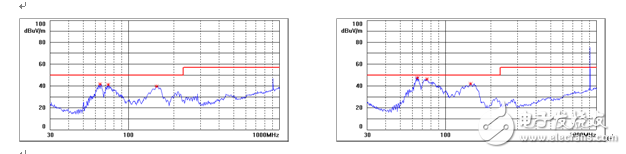

。通过扩频,降低了输出端上的高频能量,从而大幅提升了EMI性能。“实际上,扩频系数并不需要太高,根据我们的试验,±6%是最佳值”,Roderick Hogan介绍说。图2和图3显示了扩频前后的实际效果对比

2016-04-23 16:52:59

, 同步整流, 太阳能微逆变器, 低压马达驱动等应用量身定制。英飞凌新的OptiMOS 产品在以下方面具有最佳方案:-在各种负载情况下降低功率损耗提升能效-采用CanPAK 或者 S3O8更能节省空间

2012-07-13 10:50:22

的调制,以引入边带能量,并改变窄带噪声到宽带的发射特征,从而有效地衰减谐波峰值。需要注意的是,总体 EMI 性能并没有降低,只是被重新分布了。利用正弦调制,可控变量的两个变量为调制频率 (fm) 以及您

2017-05-16 16:56:41

本帖最后由 张飞电子学院鲁肃 于 2021-1-30 13:21 编辑

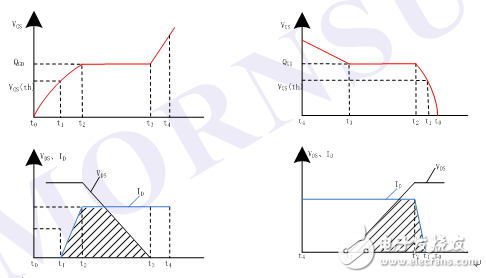

本文详细分析计算功率MOSFET开关损耗,并论述实际状态下功率MOSFET的开通过程和自然零电压关断的过程,从而使电子

2021-01-30 13:20:31

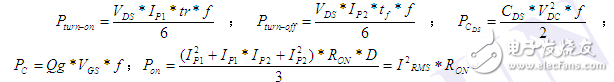

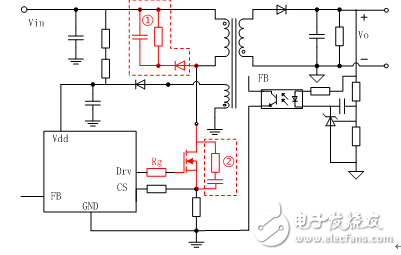

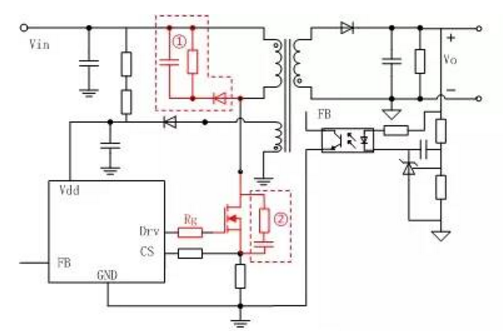

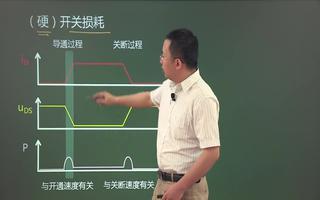

,反而会引起更严重的EMI问题,导致整个系统不能稳定工作。所以需要在减少MOSFET的损耗的同时需要兼顾模块电源的EMI性能。MOSFET的损耗主要有以下部分组成:MOSFET导通与关断过程中都会产生

2019-09-25 07:00:00

外,设计人员还能够通过调节栅极驱动导通源阻抗来控制Eon损耗。降低驱动源阻抗将提高IGBT或MOSFET的导通di/dt及减小Eon损耗。Eon损耗和EMI需要折中,因为较高的di/dt 会导致电压尖

2019-03-06 06:30:00

。设计挑战然而,SiC MOSFET 技术可能是一把双刃剑,在带来改进的同时,也带来了设计挑战。在诸多挑战中,工程师必须确保:以最优方式驱动 SiC MOSFET,最大限度降低传导和开关损耗。最大

2017-12-18 13:58:36

SiC-MOSFET和SiC肖特基势垒二极管的相关内容,有许多与Si同等产品比较的文章可以查阅并参考。采用第三代SiC沟槽MOSFET,开关损耗进一步降低ROHM在行业中率先实现了沟槽结构

2018-11-27 16:37:30

,提高开关的速度,从而降低开关损耗,但是过高的开关速度会引起EMI的问题。(2)提高栅极驱动电压也可以提高开关的速度,降低开关损耗。同时,高的栅极驱动电压会增加驱动损耗,特别是轻载的时候,对效率

2017-03-06 15:19:01

过程中的开关损耗。开关损耗内容将分成二次分别讲述开通过程和开通损耗,以及关断过程和和关断损耗。功率MOSFET及驱动的等效电路图如图1所示,RG1为功率MOSFET外部串联的栅极电阻,RG2为功率

2017-02-24 15:05:54

如何提升D类放大器的EMI性能 D类放大器以其超高的效率吸引着广大设计工程师的青睐,从而在电池供电的各种电子设备中得到了广泛的应用。但是,只要在系统中采用D类放大器,设计师们可能

2009-12-01 16:03:08

D类放大器以其超高的效率吸引着广大设计工程师的青睐,从而在电池供电的各种电子设备中得到了广泛的应用。因为EMI干扰,实现复杂度高,以及需要较多的外部元器件而导致的成本过高等问题,设计师们会如何提升D类放大器的EMI性能?

2021-04-07 06:29:26

提升SRAM性能的传统方法

2021-01-08 07:41:27

如何提升基站性能?

2021-05-26 06:33:50

开关管MOSFET的功耗分析MOSFET的损耗优化方法及其利弊关系

2020-12-23 06:51:06

问题:如何使用摆率控制来降低EMI?

2019-03-05 20:59:44

MOSFET的驱动电流,减缓该MOSFET的接通时间,同时有助于降低开关节点振铃噪音。注意:减慢高侧MOSFET的关闭时间会增大开关损耗。在低电磁辐射和高侧MOSFET的开关损耗之间选用RHO时,需要

2018-08-31 19:55:41

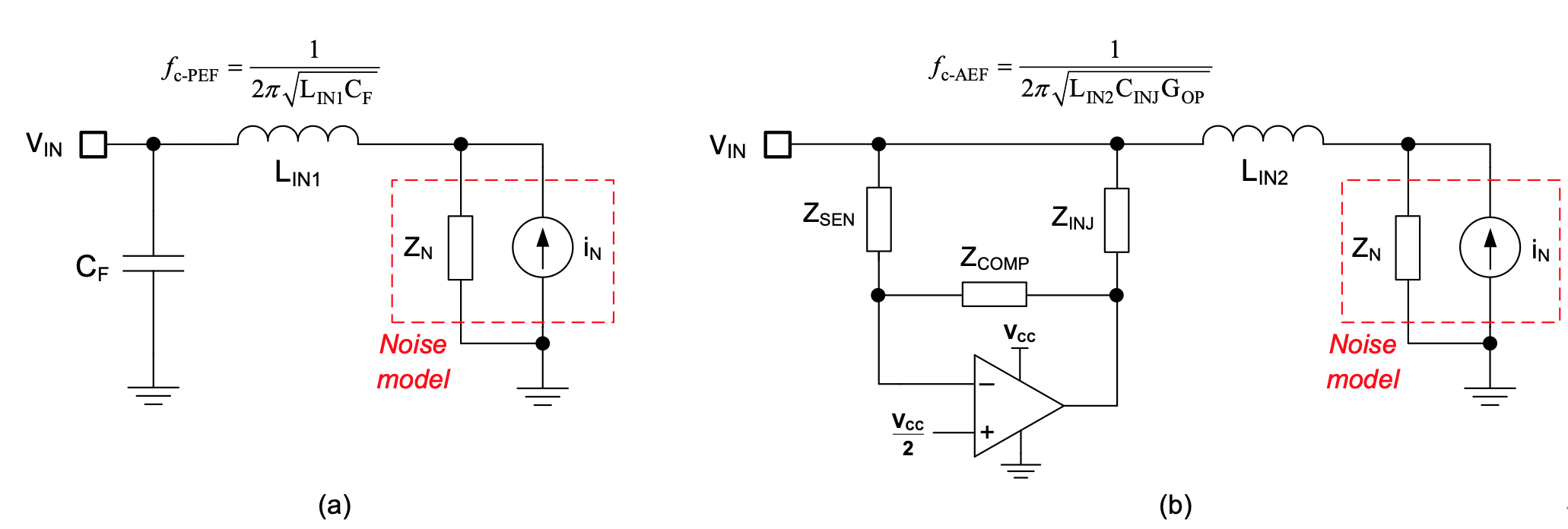

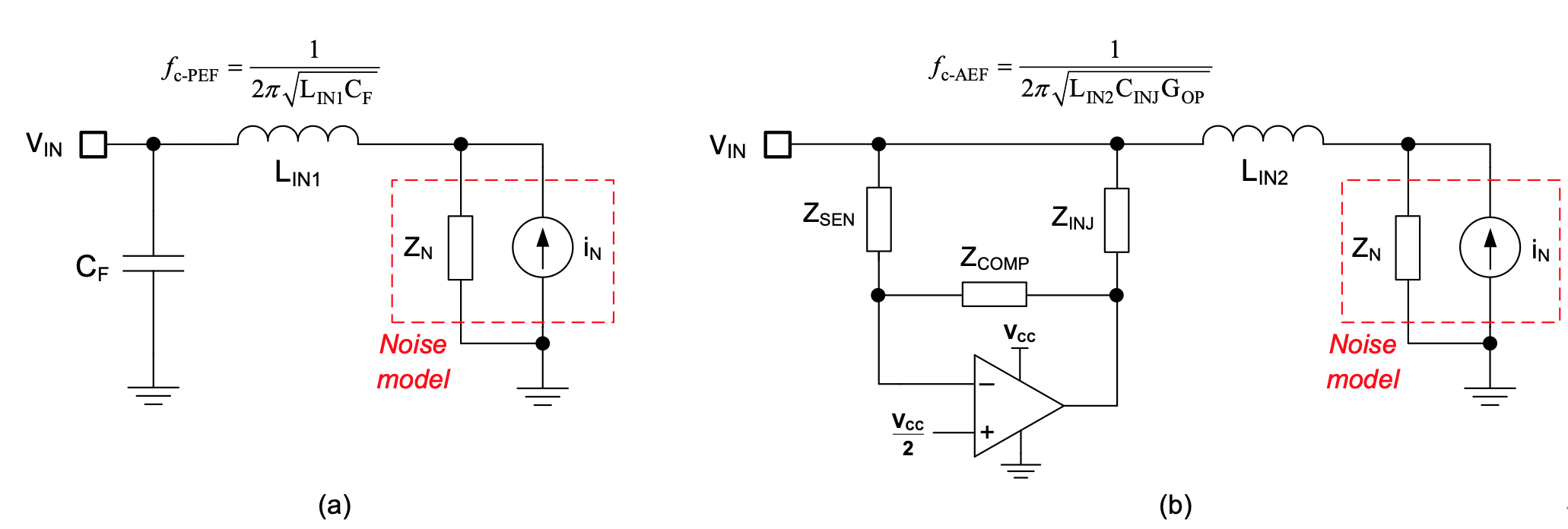

从事低电磁干扰 (EMI) 应用的设计工程师通常面临两大挑战:需要降低设计的 EMI,同时还要缩小解决方案尺寸。用于减轻开关电源产生的传导 EMI 的前端无源滤波可确保符合传导 EMI 标准,但这种

2021-08-31 14:58:42

如何去降低USB 3.x的插入损耗?有大神能解答这个问题吗

2021-07-15 06:26:36

汽车电源设计之不改PCB如何降低EMI

2021-03-18 06:04:50

如何更加深入理解MOSFET开关损耗?Coss产生开关损耗与对开关过程有什么影响?

2021-04-07 06:01:07

如何测量EMI滤波器插入损耗

2014-04-04 10:44:43

开关电源设计中,我们常常使用到一个电阻串联一个电容构成的RC电路, RC电路性能会直接影响到产品性能和稳定性。如何设计既能降低开关管损耗,且可降低变压器的漏感和尖峰电压的RC电路?

2019-01-10 14:07:18

问题:如何通过驱动高功率LED降低EMI?

2019-03-05 14:33:29

中的寄生源电感。因此,采用SMD封装的MOSFET也能实现快速开关,同时降低开关损耗。适用于4引脚器件的SMD封装名为“ThinkPAK 8X8”。 III.分析升压转换器中采用最新推出的TO247

2018-10-08 15:19:33

效率。图8.将启动电阻器添加到LMR23630转换器开关节点的影响。EMI辐射较低,但由于开关损耗较高,因此效率有所降低。图8显示了LMR23630 EVM的EMI辐射扫描。对布局进行更改后,将输入

2019-06-03 00:53:17

解决问题:怎么改变电源频率来降低EMI性能 解决办法:调制电源开关频率延伸EMI特征 更大调制指数进一步降低峰值EMI性能 文章里的这种方法涉及了对电源开关频率的调制,以引入边带能量,并

2016-01-15 09:57:10

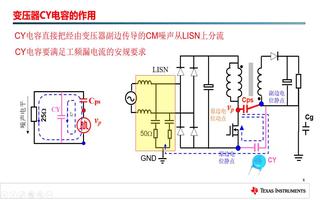

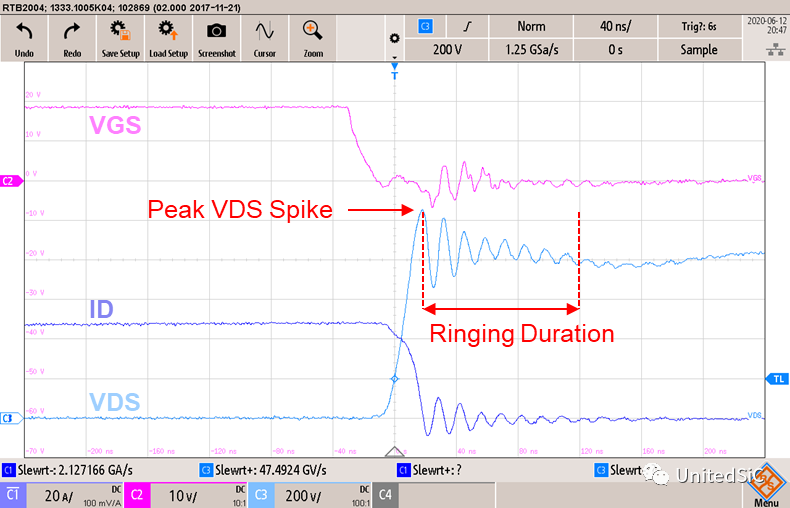

Cds、增大 Rgon 等,是降低 MOSFET 电压尖峰和电流尖峰的有效措施,从而改善电路 EMI 性能。此外合适的测量仪器设备是电源工程师快速定位问题必不可少的工具,通过科学的测量方法和有效的改善手段,可使低噪高功率密度电源产品快速成型。

2020-10-10 08:31:31

将去耦电容直接放在IC封装内可以有效控制EMI并提高信号的完整性,本文从IC内部封装入手,分析EMI的来源、IC封装在EMI控制中的作用,那么,最佳EMI抑制性能的设计规则具体有哪些呢?

2019-08-06 07:58:53

能够正常工作,这个损耗是无法避免的,在IC选型的时候尽量选择工作电流小的。 四、开关管损耗 输入端的MOS管Q1在待机的时候,主要体现的是开关损耗,所以需要降低待机时MOS管的损耗,待机的工作频率

2023-03-20 16:59:01

MOSFET通过降低开关损耗和具有顶部散热能力的DaulCool功率封装技术可以实现更高的工作频率,从而能够获得更高的功率密度。 理想开关 在典型的同步降压开关电源转换器中,MOSFET作为开关使用时

2012-12-06 14:32:55

功率MOSFET的Coss会产生开关损耗,在正常的硬开关过程中,关断时VDS的电压上升,电流ID对Coss充电,储存能量。在MOSFET开通的过程中,由于VDS具有一定的电压,那么Coss中储能

2017-03-28 11:17:44

减小硅钢片的厚度,但薄铁芯片会增加铁芯片数目和电机制造成本。3、采用导磁性能良好的冷轧硅钢片降低磁滞损耗。4、采用高性能铁芯片绝缘涂层。5、热处理及制造技术,铁芯片加工后的剩余应力会严重影响电动机

2018-10-11 10:21:49

,如果基极电流不是从非常接近0.7V的电压取得,则会产生很大的损耗。 功率MOSFET驱动效率比双极型功率晶体管高。MOSFET栅极有两个与漏源极相连的等效电容,即栅源电容Ciss和漏源电容Crss

2020-08-07 08:06:08

来自斯坦福大学的一支科研团队近日宣布在电池领域获得突破性进展,在提升锂电池性能同时降低体积和重量。近年来对电池性能的改善逐渐使用硅阳极,相比较目前常用的石墨更高效。但在充电过程中硅粒子同样会出现膨胀

2016-02-15 11:49:02

蓝牙5.0提升了哪些性能?

2021-05-18 06:25:17

FreeRTOS对性能有多大提升?比如做Robomasters这种机器人比赛,使用FreeRTOS,对性能有多大提升

2020-06-19 09:00:47

节点增加电容、磁珠以及在MOSFET外接Cds、增大Rgon等,是降低MOSFET电压尖峰和电流尖峰的有效措施,从而改善电路EMI性能。此外合适的测量仪器设备是电源工程师快速定位问题必不可少的工具,通过科学的测量方法和有效的改善手段,可使低噪高功率密度电源产品快速成型。

2020-10-21 07:13:24

5、无源元件损耗 我们已经了解MOSFET 和二极管会导致SMPS 损耗。采用高品质的开关器件能够大大提升效率,但它们并不是唯一能够优化电源效率的元件。图1 详细介绍了一个典型的降压型转换器IC

2021-12-31 06:19:44

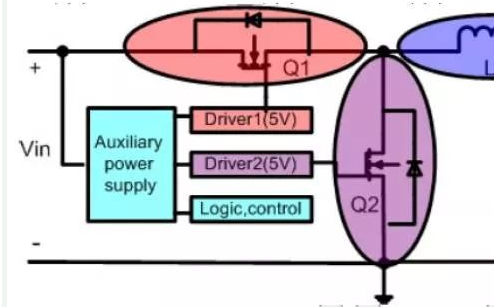

MOSFET和去耦电容器的布局布置。目的是在开关换向期间最大程度地减小功率环路寄生电感并降低电压过冲。随之而来的三个优点是:更低的电磁干扰(EMI),更低的开关电压应力和更高的转换效率。48V电池电压变化

2019-09-21 13:25:03

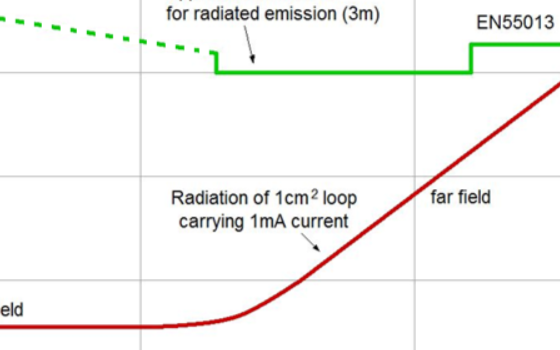

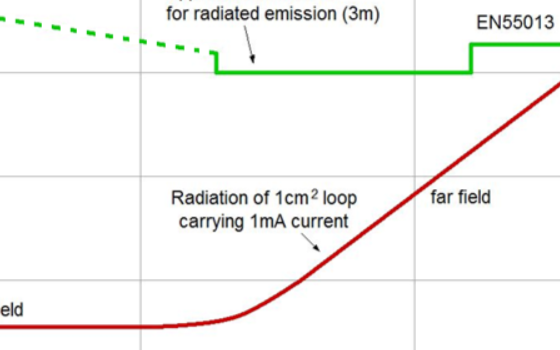

有源EMI滤波技术是一种较新的EMI滤波方法,可减弱电磁干扰,让工程师能够大幅缩小无源滤波器的尺寸、降低成本并提升EMI性能。为了说明有源EMI滤波器在EMI性能提升和空间节省方面的主要优势,在本文

2022-11-04 08:12:50

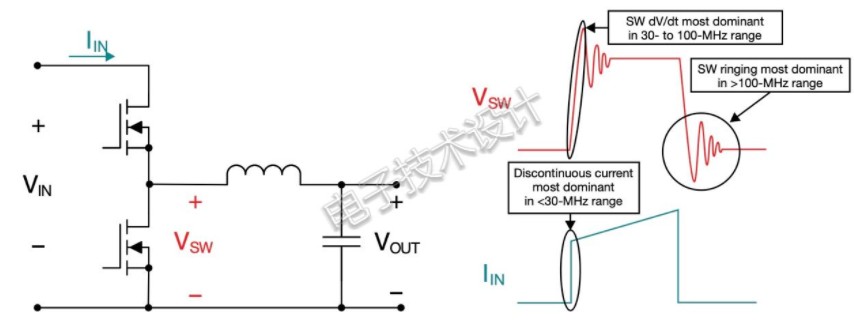

噪声的传导回路面积较大,进一步推动辐射发射的产生。在第 3 部分中,我将全面介绍降压稳压器电路中影响 EMI 性能和开关损耗的感性和容性寄生元素。通过了解相关电路寄生效应的影响程度,可以采取适当的措施将

2020-11-03 07:54:52

在第 3 部分中,我将全面介绍降压稳压器电路中影响 EMI 性能和开关损耗的感性和容性寄生元素。通过了解相关电路寄生效应的影响程度,可以采取适当的措施将影响降至最低并减少总体 EMI 信号。一般来说

2022-11-09 07:38:45

图1:开关损耗让我们先来看看在集成高侧MOSFET中的开关损耗。在每个开关周期开始时,驱动器开始向集成MOSFET的栅极供应电流。从第1部分,您了解到MOSFET在其终端具有寄生电容。在首个时段(图

2022-11-16 08:00:15

的SJ-MOSFET。通过降低栅极电阻Rg和栅极-漏极间电荷量Qgd,提高了开关性能。通过提高开关速度,可降低开关损耗并提高效率。最后列出了这三个系列相关技术信息的链接。这里虽然给出了各系列的特征,但为了进一步

2018-12-03 14:27:05

根据MOSFET的简化模型,分析了导通损耗和开关损耗,通过典型的修正系数,修正了简化模型的极间电容。通过开关磁铁电源的实例计算了工况下MOSFET的功率损耗,计算结果表明该电源中

2011-11-14 16:46:22 112

112

Fairchild将在PCIM Asia上介绍如何通过打破硅“理论上”的限制

来将IGBT 开关损耗降低30%

2015-06-15 11:09:23 1029

1029 为了有效解决金属-氧化物半导体场效应晶体管(MOSFET)在通信设备直流-48 V缓启动应用电路中出现的开关损耗失效问题,通过对MOSFET 栅极电荷、极间电容的阐述和导通过程的解剖,定位了MOSFET 开关损耗的来源,进而为缓启动电路设计优化,减少MOSFET的开关损耗提供了技术依据。

2016-01-04 14:59:05 38

38 奥地利微电子推出全球首款集成测量IC降低系统成本并提高逆变电源性能。

2016-03-30 14:45:39 10

10 MOSFET的损耗主要包括如下几个部分:1导通损耗,导通损耗是比较容易理解的,即流过MOSFET的RMS电流在MOSFET的Rdson上的I^2R损耗。降低这个损耗也是大家最容易想到的,例如选用更低

2017-11-22 17:26:02 25213

25213

MOSFET的损耗分析

2019-04-17 06:44:00 6005

6005

1.7 EMI滤波器与插入损耗

2019-02-20 06:14:00 10996

10996

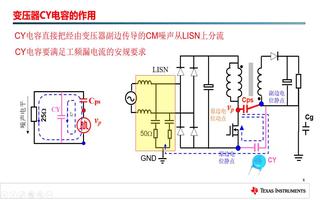

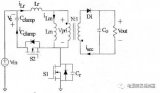

开关电源小型化设计中,提高开关频率可有效提高电源的功率密度。但随着开关频率提升,电路电磁干扰(EMI)问题使电源工程师面临了更大的挑战。本文以反激式开关拓扑为例,从设计角度,讨论如何降低电路EMI。

2019-07-19 16:02:28 640

640 优秀PCB设计练习降低PCB的EMI有许多方法可以降低PCB设计的EMI基本原理:电源和地平面提供屏蔽顶层和

2019-08-20 09:11:38 3845

3845 Mosfet的损耗主要有导通损耗,关断损耗,开关损耗,容性损耗,驱动损耗

2020-01-08 08:00:00 11

11 功率MOSFET的开关损耗分析。

2021-04-16 14:17:02 48

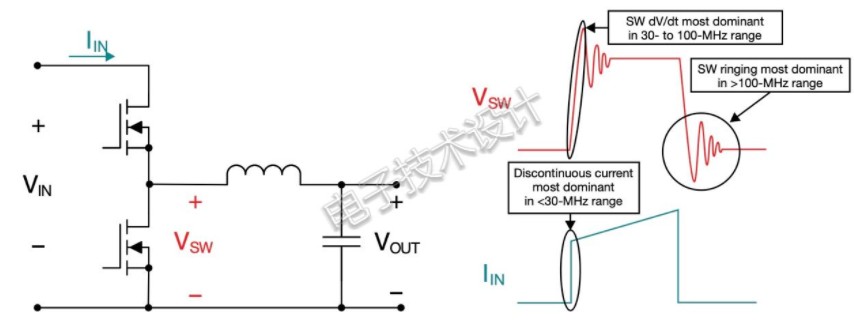

48 图1以降压转换器拓扑为例,说明了不同频带下各个因素的影响。随着设计压力不断提升,通过提高开关频率来降低尺寸和成本,以及通过增大压摆率来提高效率,使EMI问题变得更加严重。因此,有必要采用不影响电源设计、同时具有成本效益且易于集成的EMI缓解技术。

2021-05-01 09:17:00 4041

4041

AN144-通过静默交换机设计降低EMI并提高效率

2021-05-07 15:27:55 6

6 节省空间,降低EMI

2021-05-20 11:42:15 6

6 缩小EMI滤波器体积仍是系统设计人员的首要任务。

有源EMI滤波技术是一种较新的EMI滤波方法,可减弱电磁干扰,让工程师能够大幅缩小无源滤波器的尺寸、降低成本并提升EMI性能。为了说明有源EMI滤波器

2022-01-11 17:01:40 1098

1098

TPHR7404PU 做电源设计的工程师朋友都知道,MOSFET由于其快速开关,导通电压低等特性,在电源设计中应用的非常广泛。但是使用MOSFET时易出现的尖峰电压会增加EMI(电磁干扰

2021-11-26 15:08:03 2422

2422

由于涉及非常高的频率,因此降低开关模式电源中的电磁干扰 (EMI) 可能是一项挑战。电气元件的行为与预期不同,因为元件的寄生效应通常起着重要作用。本应用笔记介绍了与 EMI 相关的低压降压转换器操作的一些基础知识,并提供了一些如何在降压转换器设计中降低 EMI 的实用技巧。

2022-04-20 16:06:39 3404

3404

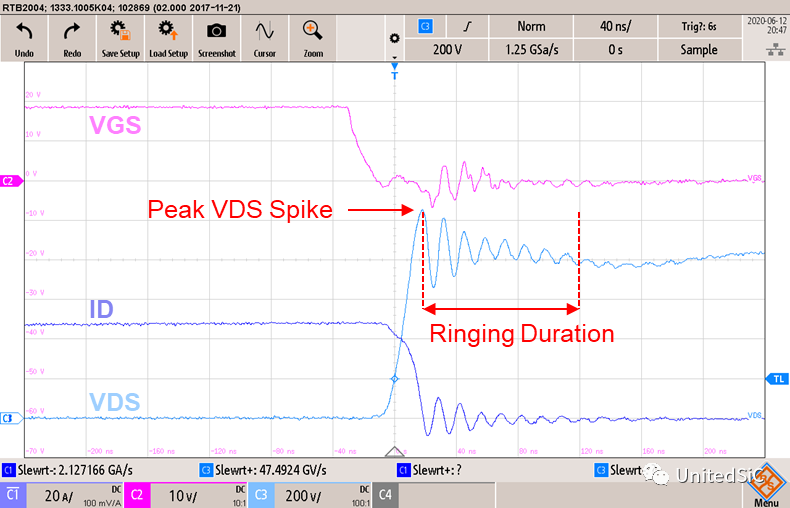

寄生电感是SiC MOSFET Vds尖峰和振铃的主要原因。SiC MOSFET的快速开关速度会导致较高Vds尖峰和较长的振铃时间。这种尖峰会降低设备的设计裕量,并且较长的振铃时间会引入EMI。

2022-08-29 15:20:38 1010

1010 据评估,世界上超过一半的电能消耗用于各种电动机。因此,降低电动机的功率损耗并提高电力转换的效率显得尤为重要。

2023-01-12 14:43:58 312

312 关键要点 ・ SiC MOSFET因其在降低功率转换损耗方面的出色表现而备受关注。 ・ 以DC-DC转换器和EV应用为例,介绍使用新一代(第4代)SiC MOSFET所带来的优势–降低损耗

2023-02-15 23:45:05 342

342 有源EMI滤波技术是一种较新的EMI滤波方法,可减弱电磁干扰,让工程师能够大幅缩小无源滤波器的尺寸、降低成本并提升EMI性能。为了说明有源EMI滤波器在EMI性能提升和空间节省方面的主要优势,在本文中,我将回顾集成了有源EMI滤波器功能的汽车同步降压控制器设计的结果。

2023-03-20 10:38:45 654

654

的传导和开关损耗,本文以给出了使用ST碳化硅MOSFET的主要设计原则,以得到最佳性能。一,如何减少传导损耗:碳化硅MOSFET比超结MOSFET要求更高的G级电压

2022-11-30 15:28:28 2647

2647

德赢Vwin官网

网站提供《DMC4040SSD可降低MOSFET损耗 确保可靠运行.pdf》资料免费下载

2023-07-25 16:07:11 0

0 性能提升,功耗降低!,这样的MOSFET是你的最爱么?

2023-12-04 15:09:36 114

114

使用SiC MOSFET时如何尽量降低电磁干扰和开关损耗

2023-11-23 09:08:34 333

333

变压器有哪些损耗?如何降低变压器的损耗? 变压器中存在几种主要的损耗,包括铜损、铁损和额外损耗。下面将详细介绍这些损耗,并提出一些有效降低变压器损耗的方法。 一、铜损 铜损是由于变压器的线圈电阻

2023-11-23 15:04:28 1375

1375 同轴传输的损耗是如何产生的?怎样才能减少损耗,提升同轴传输性能? 同轴传输的损耗主要是由以下几个因素引起的:传导损耗、辐射损耗、绝缘损耗和连接损耗。为了减少损耗并提升同轴传输的性能,可采取以下措施

2023-11-28 14:34:54 367

367 将详细介绍产生光纤熔接损耗的原因,并提供一些有效的方法来降低光纤熔接损耗。 首先,我们需要了解光纤熔接损耗的主要原因。以下是一些常见的原因: 1. 光纤表面的污染:在进行光纤熔接前,光纤表面可能会受到污染,如灰尘、油

2023-11-28 15:39:19 433

433

德赢Vwin官网

App

德赢Vwin官网

App

评论