时序发生器的设计,基于

CPLD和VerilogHDL

语言的一种线阵CCD驱动时序电路的设计,基于

CPLD和Verilog的高精度线阵CCD驱动电路设计,基于

CPLD和

VHDL的一种线阵CCD驱动时序电路

2019-06-03 16:45:25

它们的基本设计方法是借助于 EDA 设计软件,用原理图、状态机和硬件描述

语言等方法,生成相应的目标文件,最后用编程器或下载电缆,由

CPLD/

FPGA目标器件实现。 生产

CPLD/

FPGA

2019-03-04 14:10:13

`

CPLD/

FPGA高级应用

开发指南第1章可编程逻辑器件与EDA技术第2章Xilinx

CPLD系列产品第3章Xilinx

FPGA系列产品第4章Xilinx ISE应用基础第5章

FPGA高级

2013-06-02 10:13:17

本帖最后由 richthoffen 于 2019-7-19 16:41 编辑

CPLD、

FPGA的

开发应用

2019-07-18 08:04:43

各位好,请问哪里有免费下载的

CPLD系统设计及

VHDL

语言的视频教程?是天祥的。淘宝里有好多卖的,可是要淘宝帐户和钱呀?

2008-07-20 10:29:10

FPGA加三移位法,有人用

vhdl

语言写过吗

2019-03-20 15:59:05

7-5606-1132-X/TP·0574本书介绍了

FPGA的相关基础知识,

VHDL硬件描述

语言,

FPGA

开发软件的使用;器件配置与调试;

FPGA设计

中的基本问题和电路设计实例等。 《

CPLD

2012-02-27 11:31:10

和

CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的

语言以及

开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学

FPGA还是

2019-02-21 06:19:27

希望

在今后的学习中大家多多帮助,先来几个基础的verilog 教材吧 现在我用到了

FPGA关键分配的知识。 不过还是想系统的学习一下。那就先从软件的使用和语法开始学习吧。 完整的pdf格式文档德赢Vwin官网 下载地址(共31页):

FPGA中文

VHDL

语言教程.pdf

2018-07-04 01:11:32

算得上简单实用,但随着逻辑规模的不断攀升,这种落后的设计方式已显得力不从心。取而代之的是代码输入的方式,当今绝大多数的设计都采用代码来完成。

FPGA/

CPLD

开发所使用的代码,我们通常称之为硬件描述

语言

2015-01-29 09:20:41

/1bndF0bt

在第一章

中,已经给出了

FPGA/

CPLD的基本

开发流程图。这里不妨回顾一下,如图5.15所示。这个流程图是一个相对比较高等级的

FPGA/

CPLD器件

开发流程,从项目的提上议程开始,设计者需要

2015-02-09 20:14:21

FPGA入门:基本

开发流程概述

在第一章

中,已经给出了

FPGA/

CPLD的基本

开发流程图。这里不妨回顾一下,如图5.15所示。这个流程图是一个相对比较高等级的

FPGA/

CPLD器件

开发流程,从项目

2019-01-28 02:29:05

和

CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的

语言以及

开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学

FPGA还是

2015-03-12 13:54:42

开发环境,具有2年以上

CPLD/

FPGA设计经验; 了解主流CPU接口与总线。2:有扎实的数字和模拟电路、通信理论知识;3:了解Protel/Orcad/PADS等电路设计工具; 4:具备团队精神,具有

2013-08-08 10:23:02

认为做

fpga

开发是做软件

开发,这是错误的。虽然

fpga的代码是

在电脑上敲出来的,但是编程的思想跟软件编程有所不同。做

fpga

开发必须有硬件电路的思想。

FPGA的

语言

Fpga

开发者所用的

语言

2019-09-23 11:07:31

信号显示器 采用可编程逻辑器件(

FPGA/

CPLD)设计模拟信号检测电 基于VJDL

语言

在FIR滤波器设计

中的应用 基于

VHDL

语言的数字钟系统设计 采用可编程器件(

FPGA/

CPLD

2012-02-10 10:40:31

VHDL主要用于描述数字系统的结构、行为、功能和接口。除了含有许多具有硬件特征的语句外,

VHDL

在

语言形式、描述风格和句法上与一般的计算机高级

语言十分相似。

VHDL的程序结构特点是将一项

2018-09-07 09:04:45

描述

语言方式(如Verilog或

VHDL)进行设计。2.综合输入的设计被综合进入由逻辑元素(LEs,

FPGA芯片提供)组成的电路

中。3.功能仿真综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素

2017-10-24 14:59:23

用

vhdl实现

cpld配置

fpga,配置成功后

在usermode下设置一个重新配置信号,当信号有效时对

fpga进行重新配置;

fpga配置程序放在flash内;现在遇到的问题是,上电

cpld能够正常配置

fpga并且进入usermode ,但是加上重新配置语句过后就不能成功配置

fpga,求高人指点~

2013-01-17 22:35:39

超高速集成电路硬件描述

语言,主要是应用在数字电路的设计

中。它在中国的应用多数是用在

FPGA/

CPLD/EPLD的设计

中。当然

在一些实力较为雄厚的单位,它也被用来设计ASIC。

VHDL主要用于描述数字系统的结构

2015-09-30 13:48:29

大家熟悉

在

CPLD/

FPGA

开发中一个关键的技术——状态机,并且简单介绍了一下RTL 视图的使用。第三讲:加/减计数器例程,讲解了计数器的

VHDL

语言的设计过程,以及硬件下载的方法,并且可以通过

2020-05-14 14:50:30

特权同学的《

FPGA/

CPLD边学边练---快速入门Verilog/

VHDL》

中的UART串口收发实验发送数据和接收的数据不一致。

在每个有效数据的后面都会多两个数据。比如发送的有效数据是:FF。则

2017-11-30 09:25:44

Verilog HDL

语言有什么优越性Verilog HDL

语言

在

FPGA/

CPLD

开发

中的应用

2021-04-23 07:02:03

,让大家熟悉

在

CPLD/

FPGA

开发中一个关键的技术——状态机,并且简单介绍了一下RTL视图的使用。 第三讲:加/减计数器例程,讲解了计数器的

VHDL

语言的设计过程,以及硬件下载的方法

2009-03-26 16:38:29

大家好,今天第一次发帖,见笑了。因初学

FPGA、

cpld,不知从哪着手,以前看过EDA,觉得

VHDL

语言比较复杂

2009-10-15 22:37:06

请问一下,现在c

语言编程

FPGA并不是十分的广泛,那么,以后未来的趋势是不是使用c

语言来进行

FPGA编程,就是DSP,ARM一样呢?那Verilog和

vhdl会不会被淘汰啊?

2015-04-15 16:44:11

如题,multisim12能不能进行

FPGA/

CPLD的

VHDL仿真??各位大神,multisim12到底能不能进行

VHDL的仿真呢?看上multisim的直观,可惜好像不能使用里面的

FPGA器件。。各种忧伤啊。。。。。求助。。。

2013-09-22 17:09:04

《

CPLD_FPGA的

开发与应用》

2012-08-17 09:47:53

的边界扫描测试第5章 Xilinx Foundation应用基础第6章 Foundation高级应用第7章

VHDL

语言简介第8章

CPLD/

FPGA在数字系统设计

中的应用第9章

CPLD/

FPGA

在通信

2018-03-29 17:11:59

`

CPLD、Spartan可编程器件的基础知识,

VHDL

语言基础,Foundation编辑工具使用,高级应用以及

CPLD/

FPGA在数字系统设计的应用。`

2021-04-06 11:43:55

请问使用

VHDL

语言设计

FPGA有哪些常见问题?

2021-05-06 09:05:31

设计

语言,熟悉Quartus、ISE等

开发环境,具有2年以上

CPLD/

FPGA设计经验; 了解主流CPU接口与总线。 4:具备团队精神,具有良好的沟通能力;5:具有一定的程序设计基础(从事过军品

开发

2013-08-02 15:58:20

`相对于C

语言,基于繁琐的

VHDL等等,图像化编程

语言可以

开发

FPGA,完成信号的触发以及数据的采集等等内容`

2017-01-20 11:40:02

语言进行

CPLD/

FPGA设计

开发,Altera和Lattice已经

在

开发软件方面提供了基于本公司芯片的强大

开发工具。但由于

VHDL设计是行为级设计,所带来的问题是设计者的设计思想与电路结构相脱节,而且

2019-06-18 07:45:03

的Quartus II软件的基本使用方法和

VHDL描述的基本结构。第二讲:主要以moore状态机为例,让大家熟悉

在

CPLD/

FPGA

开发中一个关键的技术——状态机,并且简单介绍了一下RTL视图的使用。第三

2009-02-07 11:34:24

大家了解 Altera 公司的Quartus II 软件的基本使用方法和

VHDL描述的基本结构。 第二讲:主要以moore 状态机为例,让大家熟悉

在

CPLD/

FPGA

开发中一个关键的技术 ——状态机

2012-09-29 21:32:44

利用现场可编程门阵列(

FPGA)和

VHDL

语言实现了PCM码的解调,这样

在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

2021-05-07 06:58:37

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述

语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。

2019-10-18 08:20:51

淘汰的今天,作为一个电类专业的毕业生应该熟悉

VHDL

语言和

CPLD、

FPGA器件的设计,阎石教授新编写的教材也加入了

VHDL

语言方面的内容,可见使用

VHDL

语言将数字系统集成到一块集成电路

中是现在

2009-10-22 15:44:59

(PLD)的发展而发展起来的。它是一种面向设计、多层次的硬件描述

语言,是集行为描述、RTL描述、门级描述功能为一体的

语言,并已成为描述、验证和设计数字系统中最重要的标准

语言之一。由于

VHDL

在语法和风格上类似于高级编程

语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。

2019-08-28 08:05:46

串行通信发送器是什么工作原理?怎么用

VHDL

语言

在

CPLD上实现串行通信?

2021-04-13 06:26:46

在语法和风格上类似于高级编程

语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,使用

VHDL

语言进行

CPLD/

FPGA设计

开发,Altera和Lattice

2019-08-08 07:08:00

开发环境,具有2年以上

CPLD/

FPGA设计经验; 了解主流CPU接口与总线。2:有扎实的数字和模拟电路、通信理论知识;3:了解Protel/Orcad/PADS等电路设计工具; 4:具备团队精神,具有

2013-08-12 09:48:39

本人小菜鸟,开始学

FPGA的时候学的Verilog

语言,后来因为课题组前期的工作都是

VHDL就该学

VHDL了。最近听了几个师兄的看法,说国内用

VHDL的已经很少了,建议我还是坚持用Verilog,小菜现在好纠结,请问到底应该用哪种

语言呢?望各位大神指点!

2015-07-08 10:07:56

感觉模拟IC设计就应该是设计模拟电路.设计运放等,通过设计电路、

在硅片上搭建TTL.CMOS......从而做成IC芯片;而我经常看到说IC设计就是使用

VHDL

语言设计IC,写好

VHDL

语言后烧录到

FPGA.CPLD.......从而做成芯片。我想问的是这两者有什么区别?

2018-08-29 09:45:43

),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了

FPGA/

CPLD器件,那么我们就可以将所需要的UART功能集成到

FPGA内部。使用

VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于

FPGA/

CPLD器件设计与实现UART。

2012-05-23 19:37:24

电缆下载到目标芯片

FPGA或

CPLD

中。 如果是大批量产品

开发,则通过更换相应的厂家综合库,轻易地转由 ASIC 的方式实现。

2019-02-28 11:47:32

基于

CPLD的状态机该怎样去设计?如何去描述

VHDL

语言?

2021-04-28 07:01:10

门阵列)。本文主要探索CPU协同

FPGA的异构计算方式。传统的

FPGA

开发方式是采用硬件描述

语言Verilog/

VHDL,

开发难度高,为了

在

FPGA上实现类似CPU/GPU的

开发运行体验,

FPGA两大

2017-09-25 10:06:29

VHDL硬件描述

语言教学:包括

fpga讲义,

VHDL硬件描述

语言基础,

VHDL

语言的层次化设计的教学幻灯片

2006-03-27 23:46:49

93

93

第1章 绪论 1.1 关于EDA 1.2 关于

VHDL1.3 关于自顶向下的系统设计方法 1.4 关于应用

VHDL的 EDA过程 1.5 关于在系统编程技术 1.6 关于

FPGA/

CPLD的优势 1.7

2008-06-04 10:24:06

1679

1679

EDA/

VHDL讲座主要内容一、EDA、EDA技术及其应用与发展二、硬件描述

语言三、

FPGA和

CPLD四、EDA工具软件五、电子设计竞赛几个实际问题的讨论六、

VHDL

语言初步七

2009-03-08 10:54:10

39

39

A

CPLD

VHDLIntroduction This introduction covers the fundamentals of

VHDLas applied to Complex

2009-03-28 16:14:37

25

25

FPGA/

VHDL技术是近年来计算机与电子技术领域的又一场革命。本书以AAltera公司的

FPGA/

CPLD为主详细介绍了

FPGA、

CPLD为主详细介绍了

FPGA的相关知识,MAX+PLUSⅡ

开发环境和

VHDL

语言基础,并

2009-07-11 15:06:42

58

58

VHDL

语言及其应用的主要内容:第一章 硬件模型概述第二章 基本的

VHDL编程

语言第三章

VHDL模型的组织第四章

VHDL综合工具第五章

VHDL应用样例附录A

VHDL

2009-07-20 12:06:15

0

0

介绍了用

VHDL

语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera 公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13

85

85

VHDL

语言概述:本章主要内容:硬件描述

语言(HDL)

VHDL

语言的特点

VHDL

语言的

开发流程 1.1 1.1 硬件描述

语言( 硬件描述

语言(HDL HDL)H

2009-08-09 23:13:20

47

47

VHDL

语言程序的元素:本章主要内容:

VHDL

语言的对象

VHDL

语言的数据类型

VHDL

语言的运算符

VHDL

语言的标识符

VHDL

语言的词法单元

2009-09-28 14:32:21

41

41

CPLD

FPGA高级应用

开发指南

2010-04-15 10:56:51

58

58

基于

FPGA/

CPLD芯片的数字频率计设计摘要:详细论述了利用

VHDL硬件描述

语言设计,并在EDA(电子设计自动化)工具的帮助下,用大规模可编程逻辑器件(

FPGA/

CPLD)实现

2010-04-30 14:45:13

132

132

简要介绍了

CPLD/

FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII

开发软件下,利用

VHDL硬件描述

语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57

36

36

探讨电梯控制技术的发展历史和技术现状,仔细研究

CPLD器件的工作原理,

开发流程以及

VHDL

语言的编程方法;采用单片

CPLD器件,在MAX+plusⅡ软件环境下,运用

VHDL

语言设计一个16楼层单

2010-12-27 15:27:35

56

56

摘要:简要介绍了

CPLD/

FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II

开发软件下,利用

VHDL硬件描述

语言以及原理图的输

2006-03-13 19:36:44

869

869

摘 要:通过设计实例详细介绍了用Verilog HDL

语言

开发

FPGA/

CPLD的方法,并通过与其他各种输入方式的比较,显示出使用Verilog HDL

语言的优越性。

2009-06-20 11:51:28

1857

1857

摘 要: 串行通信是实现远程测控的重要手段。采用

VHDL

语言在

CPLD上实现了串行通信,完全可以脱离单片机使用。 关键词:

2009-06-20 12:43:50

570

570

摘要:简要介绍了

CPLD/

FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II

开发软件下,利用

VHDL硬件描述

语言以及原理图的输

2009-06-20 12:45:00

627

627

基于

VHDL

语言的智能拨号报警器的设计 介绍了以EDA技术作为

开发手段的智能拨号报警系统的实现。本系统基于

VHDL

语言,采用

FPGA作为控制核心,实现了远程防盗报警。该

2009-10-12 19:08:43

1167

1167

采用

CPLD/

FPGA的

VHDL

语言电路优化原理设计

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述

语言,是随着可编程逻辑器件(PLD)的发展而发展起

2010-03-19 11:38:02

2318

2318

在我国使用Verilog HDL的公司比使用

VHDL的公司多。从EDA技术的发展上看,已出现用于

CPLD/

FPGA设计的硬件C

语言编译软件,虽然还不成熟,应用极少,但它有可能会成为继

VHDL和Verilog之后,设计大规模

CPLD/

FPGA的又一种手段。

2011-03-12 11:21:20

1686

1686

利用一块芯片完成除时钟源、按键、扬声器和显示器(数码管)之外的所有数字电路功能。所有数字逻辑功能都在

CPLD器件上用

VHDL

语言实现。这样设计具有体积小、设计周期短(设计过

2011-09-27 15:08:56

366

366

VHDL(Very High Speed Integrated CIRCUITHARDWARE DESCRIPTION Language)是IEEE工业标准硬件描述

语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。

2012-03-02 09:16:05

3822

3822

用

VHDL/VerilogHD

语言

开发PLD/

FPGA的完整流程为: 1.文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。通常

VHDL文件保存为.vhd文件,Verilog文件保存为.v文件 2.功能仿真

2012-05-21 12:58:06

1083

1083

本资料是关于基于Quartus II

FPGA/

CPLD数字系统设计实例(

VHDL源代码文件),需要的可以自己下载。

2012-11-13 14:03:36

907

907

altera

FPGA/

CPLD高级篇(

VHDL源代码)

2012-11-13 14:40:38

134

134

基于

CPLD的

VHDL

语言数字钟(含秒表)设计

2015-11-04 15:14:36

9

9

CPLD-FPGA应用系统设计与产品

开发-人邮

2016-05-09 10:59:26

16

16

,或是硬件描述

语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用

FPGA/

CPLD的在线修改能力,随时修改设计而不必改动硬件电路。 使用

FPGA/

CPLD来

开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

FPGA/

CPLD还

2017-10-09 09:52:20

14

14

在小规模数字集成电路就要淘汰的今天,作为一个电类专业的毕业生应该熟悉

VHDL

语言和

CPLD、

FPGA器件的设计,阎石教授新编写的教材也加入了

VHDL

语言方面的内容,可见使用

VHDL

语言将数字系统集成

2017-12-05 09:00:31

20

20

Xilmx作为当今世界上最大的

FPGA/

CPLD生产商之一,长期一来一直推动着

FPGA/

CPLD技术的发展。其

开发的软件也不断升级换代,由早期的Foundation系列逐步发展到目前的ISE系列

2018-03-16 14:25:24

6

6

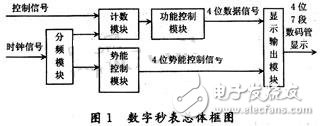

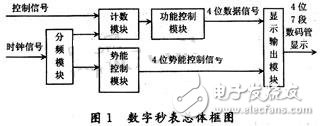

应用

VHDL

语言设计数字系统,很多设计工作可以在计算机上完成,从而缩短了系统的

开发时间,提高了工作效率。本文介绍一种以

FPGA为核心,以

VHDL为

开发工具的数字秒表,并给出源程序和仿真结果。

2019-07-24 08:05:00

3119

3119

用

VHDL

语言设计交通灯控制系统,并在MAX+PLUS II系统对

FPGA/

CPLD芯片进行下载,由于生成的是集成化的数字电路,没有传统设计中的接线问题,所以故障率低、可靠性高,而且体积小。体现了EDA技术在数字电路设计中的优越性。

2018-11-05 17:36:05

23

23

本文档的主要内容详细介绍的是

FPGA视频教程之

FPGA和

CPLD与

VHDL基础知识的详细资料说明。主要的目的是:1.

VHDL入门,2.设计单元,3.体系结构建模基础,4.

VHDL逻辑综合,5.层次

2019-03-20 14:35:19

9

9

本文档的主要内容详细介绍的是使用

FPGA和

VHDL

语言进行的抢答器设计资料合集免费下载。

2019-06-03 08:00:00

19

19

什么是

vhdl

语言

VHDL的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述

语言)。VHSIC是Very High Speed

2020-04-23 15:58:49

10242

10242

经常看到不少人在论坛里发问,

FPGA是不是用C

语言

开发的?国外有些公司专注于

开发解决编译器这方面问题,目的让其能够达到用C

语言替代

VHDL

语言的目的,也

开发出了一些支持用c

语言对

FPGA进行编程的

开发工具。但在使用多的

FPGA编程

语言还是verilog和

VHDL

语言,一般不使用C

语言进行编程。

2020-07-29 16:37:37

23117

23117

本文档的主要内容详细介绍的是

FPGA

VHDL

语言基础的学习课件免费下载。

2021-01-21 16:30:00

26

26

简要介绍了

CPLD/

FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII

开发软件下,利用

VHDL硬件描述

语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-16 09:45:53

10

10

在这个项目中,我们用

VHDL

语言创建一个 8 位算术逻辑单元 (ALU),并在连接到带有输入开关和 LED 显示屏的定制 PCB 的 Altera

CPLD

开发板上运行。

2023-10-24 17:05:57

675

675

和

VHDL都是用于逻辑设计的硬件描述

语言,并且都已成为IEEE标准。它们能形式化地抽象表示电路的结构和行为,支持逻辑设计中层次与领域的描述,具有电路仿真与验证机制以保证设计的正确性,并便于文档管理和设计重用。

fpga用什么

语言

开发

FPGA(现场可编程逻辑门阵列)的

开发主要使用硬件描述

语言(HD

2024-03-14 17:09:32

223

223

FPGA(现场可编程门阵列)的编程涉及到三种主要的硬件描述

语言(HDL):

VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。这些

语言在

FPGA设计和

开发过程中扮演着至关重要的角色。

2024-03-15 14:36:01

88

88

德赢Vwin官网 App

德赢Vwin官网 App

评论