X24128是美国XICor公司生产的CMOS串行通信EEPROM。内部结构为16k字节8位阵列。X24182在2线总线上可同时并联8片,并具有软件和硬件写保护功能。片内最高地址单元(FFFFH)为一写保护寄存器。通过写入不同数据,可进行软件写保护、块锁定选择保护和编程硬件写保护三种不同形式的写保护。在2线总线上串行通信的最高时钟频率为400kHz。另外还具有输入、输出消噪声和抑制功能。而且功耗低,它的读状态工作电流小于1mA, 写状态工作电流小于3mA,静态电流小于1uA。工作电压有1.8V-3.6V、2.5V-5.5V和4.5V-5.5V三种类型供选择。写方式有按字节写和按页写两种形式,每页为32字节。

1.管脚说明

X24128有三种封装形式:14-SOIC、16-SOIC和8-PDIP。图1为8-PDIP封装的外形图。各管脚的功能说明如下:

VCC、Vss:为电源的正、负极输入端;

SCL:串行时钟输入端,用于控制数据的输入与输出;

SDA:串行数据输入与输出的共用管脚。漏极输出,可与其它器件的SDA脚的输出组成线或逻辑关系。由于是漏极输出,因此在使用时必须接上拉电阻;

WP:硬件写保护输入管脚。当WP管脚接高电平且写保护寄存器的WPEN位被写1时,写保护仿寄存器实施写保护,这时块锁定的存储阵列无法再用程序改写。不需要写保护时,WP管脚接低电平;

S0、S1、S2器件选择输入端。在串行通信总线上可以并接多至8片X24128,它们可以分时享用总线。在输入的地址中,当第一字节(器件地址)的数据与器件的输入管脚S0、S1、S2相符时,器件被选择并可与CPU进行串行通信。如与器件的输入管脚不符,则处于等待状态。

2.地址选择

X24128内部EEPROM由16k×8位组成,这16k数据单元的地址为0000H-3FFFH。写保护寄存器的地址为FFFFH。每个地址可以分为地址高位字节BYTE1和地址低位字节BYTE0。除了数据单元地址外,还具有一个器件地址。在器件地址中,高四位必须为1010,这是X24128的识别码。S2、S1、S0三位为所选器件的地址码,它们必须与所选器件的输入管脚S2、S1、S0相一致。例如所选器件的S2管脚接Vcc,S1、S0两个输入管脚连接Vss,则器件地址应为1010100R/WB。位位为读、写选择位,位为1时,选择读;位为0时,选择写。

3.写保护寄存器

写保护寄存器是一可读寄存器,格式如下:各位的状态可通过程序写入。现将功能说明如下:

WEL:为EEPROM阵列写使能锁存器,WEL=1时,写使能锁存器置位,可进行写操作;WEL=0时,写使能锁存器复位,拒绝一切写操作。

RWEL:为“写保护寄存器”写使能锁存器,RWEL=1时,可对“写保护寄存器”进行改写;RWEL=0时,写使能锁存器复位,拒绝改写。

上电时,WEL和RWEL均被复位。

BL1、BL0:EEPROM阵列块锁定保护位。整个EEPROM阵列有三种锁定形式,BL1、BL0=00时,整个阵列未加块锁定保护;BL1、 BL0=01时,地址为3000H~FFFH的阵列进行块锁定保护;BL1、BL0=10时,地址为2000~3FFF的阵列进行块锁定保护;BL1、 BL0=11时,地址为0000H~3FFFH的阵列进行块锁定保护.

WPEN:写保护使能位,当WPEN位被写入1且将器件的WP管脚接至Vcc时,,硬件写保护使能;当WPEN位被复位或者WP管脚接至Vss时,硬件写保护不再使能。硬件写保护能为整个系统在实际应用操作中给用户实施写保护操作提供方便。

通过BL1、BL0位进行块锁定的存储器阵列不受硬件写保护的影响,只有通过改变BL1、BL0的值才能改变块锁定保护阵列的区域范围。但改变BL1、 BL0的值要受到RWEL位的制约。RWEL位的改变又受到硬件写保护的制约。未加块锁定保护的阵列不受硬件写保护的制约,因而可对其进行写操作。

在未加硬件写保护的情况下,对BL1、BL0的改写可按以下三步进行:

1)对FFFFH地址写入00000010,使WEL=1;

2)对FFFFH地址写入00000110B,使RWEL=1;

3)对FFFFH地址写入X00XX010B,使RWEL=0。进行寄存器写保护。如果在第(3)步中使RWEL=1,则对寄存器的改写无效。寄存器仍保持(2)步的状态。

4.读写时序

在进行读、写操作之前,先设置开始状态。方法是命令SCL总线保持高电平,并在SDA总线上设置一个由高电平向低电平的跳变。而在通信结束时,又需设置一个结束状态,即将SCL总线保护高电平,并在SDA总线上设置一个低电平向高平跳变。设置结束状态后,器件脱离通信状态。

SDA总线上通信数据的改变必须在SCL总线处于低电平状态时进行。SCL总线处于高电平时,数据处于保持状态。

在通信过程中,接收数据的器件每次有效地接收到8位数据后,都给发送数据的器件发送一个负脉冲应答信号。在定操作过程中,X24128每次接收到8位数据(包括接收到8位地址数据)后,在SDA总线上产生一个负脉冲,该脉冲的宽度一直延续到第9个时钟脉冲信号结束。在读操作过程中,CPU每次接收到 X24128所发送的8位数据后,SDA总线上再发送一个负脉冲,以示读有效,然后X24128可以继续发送数据。如果X24128未接收到应答信号,则停止发送数据,直到接收到结束信号时,通信结束。

4.1按字节写时序

给X24128内部存储阵列中未加锁定保护部分的某一单元写一个字节的数据时,首先设置开始状态,再依次发送器件地址和数据地址的字节1和字节 0,X24128每次接收到一个8位地址字节后,利用第9个时钟脉冲发出应答信号。CPU接收到第3个应答信号后,再发送8位数据和接收应答信号,最后设置结束状态。X24128接收到结束信号后,开始将接收到的数据写入EEPROM阵列的内部写过程。在进行内部写过程中,对外部输入的任何信号都不作反应,SDA管脚输出高阻态。

4.2按页写时序

由CPU给X24128写数据时,可以按页写,每页包括32字节,按页写的方式在开始时如同按字节写,只是每次写完一个字节数据后,X24128内部地址指针自动加1后才可以继续写数据,无需再次写入地址。本页的最高地址写入后,地址指针自动返回到本页的最低地址,如果继续写入数据,则将已写过的数据覆盖,只有发送给X24128结束信号后,X24128才终止接收数据,开始进行内部写过程。

4.3读当前地址数据

如果要读X24128内部地址指针当前所指单元的数据,只要发送给X24128开始信号、器件地址(位为1)和接收到应答信号后,即可接收X24128所发送的当前地址的数据。接收完毕,发送结束信号。X24128发送完数据后,地址指针自动加1。

4.4读取任一地址的数据

先给X24128发送所要读取数据的地址,使其成为当前地址指针所指地址。其中器件地址的位写入0,再按读当前地址数据的方式读取数据。

4.5连续读取数据

连续读取数据如同读取任一地址数据,将所要连续读取数据的首位地址设置成当前地址,在接收完第一字节的数据后,不是发送结束信号,而是发送应答信号,X24128接收到应答信号后继续发送第二字节数据。只要CPU每次接收完一个字节的数据后所发送的是应答信号,X24128就会继续发送下一字节的数据,当发送完整个存储阵列的最高地址的数据后,地址指针将返回到0000H单元。如果继续发送应答信号,X24128将从0000H单元开始继续发送数据。只有接收到结束信号才终止发送。

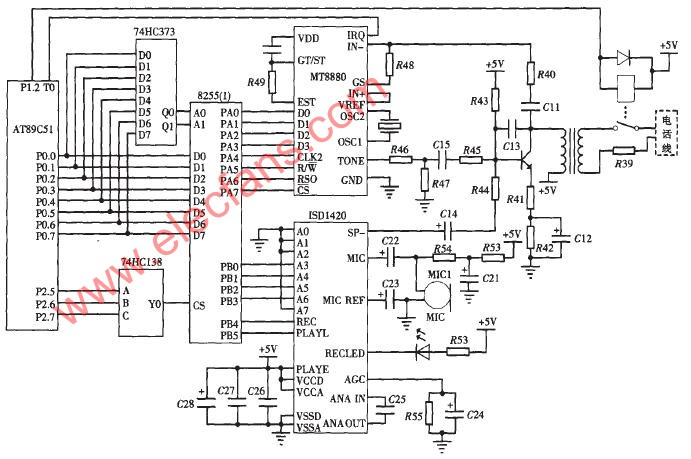

5.接口电路及编程

X24128与AT89C51的接口电路如图2所示。在2线总线上最多可并接8片X24128。以P1.0口线作为时钟信号输出,P1.1口线作为数据输入、输出。总线接4.7kΩ的上拉电阻。下面以AT89C51寄存器R2的数据写入X24128(1)的1000H地址中为例,假设1000H地址未加写保护,则编程如下:

德赢Vwin官网 App

德赢Vwin官网 App

评论