在一篇以前的文章中,Timothy T.曾谈到JESD204B接口标准(该标准越来越受欢迎,因为它能在高速数据采集系统里简化设计)的时钟要求。在本文中,笔者将谈论抖动合成器与清除器的不同系统参考信号

2018-05-14 08:48:18 9732

9732

随着数模转换器的转换速率越来越高,JESD204B 串行接口已经越来越多地广泛用在数模转换器上,其对器件时钟和同步时钟之间的时序关系有着严格需求。本文就重点讲解了JESD204B 数模转换器的时钟

2015-01-23 10:42:18 21149

21149 开发串行接口业界标准JESD204A/JESD204B的目的在于解决以高效省钱的方式互连最新宽带数据转换器与其他系统IC的问题。

2021-11-01 11:24:16 5783

5783

JESD204B 同步时钟。此设计可提供多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏差。此

2018-10-15 15:09:38

的时刻直至模数转换器输出数字表示这段时间内的时钟周期数。JESD204及JESD204A标准中没有定义可确定性设置模数转换器延迟和串行数字输出的功能。另外,转换器的速度和分辨率也不断提升。这些因素导致了该

2019-05-29 05:00:03

的选项。完整的JESD204C规范可通过 JEDEC获得。 本入门文章由两部分组成,旨在介绍JESD204C标准,着重说明其与JESD204B的不同之处,并详细阐明为达成上述目标、提供对用户更友好的接口

2021-01-01 07:44:26

,CML输出驱动器的效率开始占优。CML的优点是:因为数据的串行化,所以对于给定的分辨率,它需要的输出对数少于LVDS和CMOS驱动器。JESD204B接口规范所说明的CML驱动器还有一个额外的优势

2019-06-17 05:00:08

`描述采用均衡技术可以有效地补偿数据转换器的 JESD204B 高速串行接口中的信道损耗。此参考设计采用了 ADC16DX370 双 16 位 370 MSPS 模数转换器 (ADC),该转换器利用

2015-05-11 10:40:44

摘要 随着数模转换器的转换速率越来越高,JESD204B 串行接口已经越来越多地广泛用在数模转换器上,其对器件时钟和同步时钟之间的时序关系有着严格需求。本文就重点讲解了JESD204B 数模转换器

2019-06-19 05:00:06

MS-2503: 消除影响JESD204B链路传输的因素

2019-09-20 08:31:46

和 CMOS 接口提供的优势。有了 JESD204B,您无需再:使用数据接口时钟(嵌入在比特流中)担心信道偏移(信道对齐可修复该问题)使用大量 I/O(高速串行解串器实现高吞吐量)担心用于同步多种 IC

2018-09-13 14:21:49

什么是8b/10b编码,为什么JESD204B接口需使用这种编码?怎么消除影响JESD204B链路传输的因素?JESD204B中的确定延迟到底是什么? 它是否就是转换器的总延迟?JESD204B如何使用结束位?结束位存在的意义是什么?如何计算转换器的通道速率?什么是应用层,它能做什么?

2021-04-13 06:39:06

使用AD6688时遇到一个JESD204B IP核问题。参考时钟为156.25MHz,参数L=2,F=2,K=32,线速率为6.25Gbps,使用的为SYSREF always中的每个SYSREF都

2019-04-11 21:12:09

的优势。有了 JESD204B,您无需再:使用数据接口时钟(嵌入在比特流中)担心信道偏移(信道对齐可修复该问题)使用大量 I/O(高速串行解串器实现高吞吐量)担心用于同步多种 IC 的复杂方法(子类…

2022-11-21 07:02:17

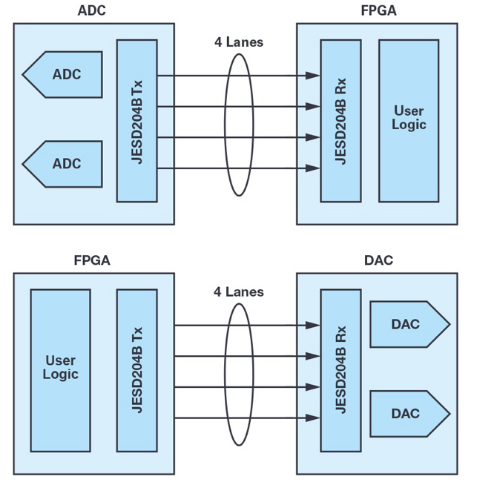

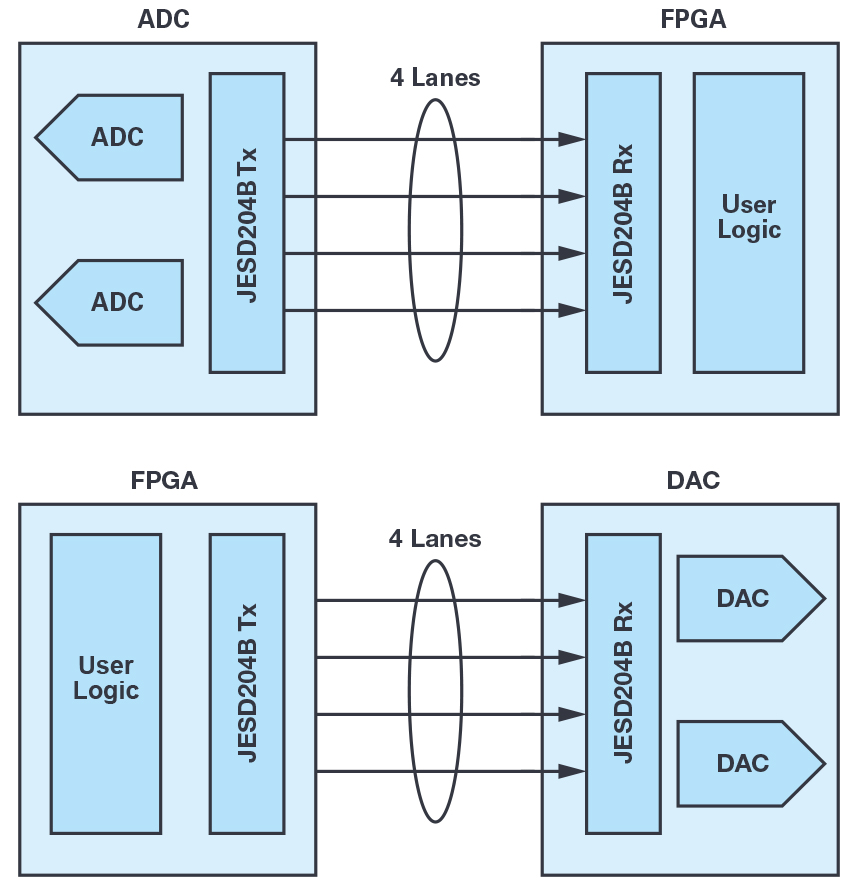

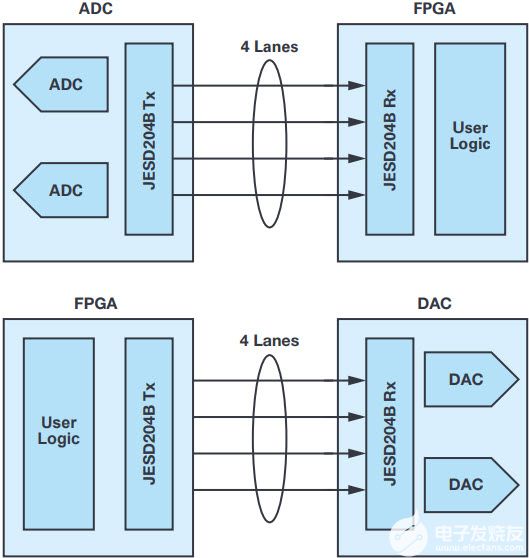

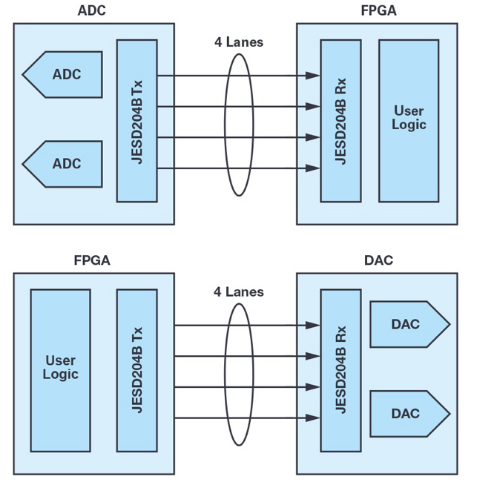

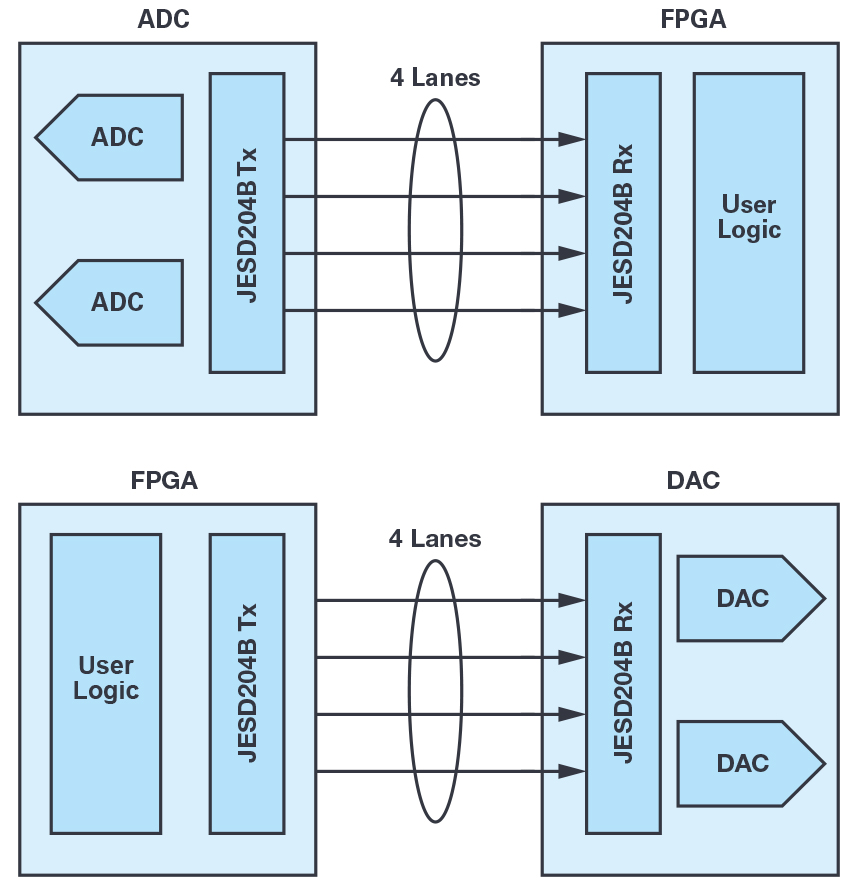

在使用最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。那么在解决 ADC 至 FPGA

2021-04-06 06:53:56

JESD204B的工作原理JESD204B的控制字符

2021-04-06 06:01:20

JESD204B生存指南

2019-05-28 12:08:12

的是 JESD204B 接口将如何简化设计流程。与 LVDS 及 CMOS 接口相比,JESD204B 数据转换器串行接口标准可提供一些显著的优势,包括更简单的布局以及更少的引脚数。因此它能获得工程师

2022-11-23 06:35:43

FIFO方案,则无法正常工作。

该问题的一种解决方案是让双通道转换器使用多点链路JESD204B接口,其中每个转换器都使用各自独立的串行链路输出。然后便可针对每个ADC使用非相干时钟,且每个串行链路

2024-01-03 06:35:04

FPGA 协作。他们特别感兴趣的是 JESD204B 接口将如何简化设计流程。与 LVDS 及 CMOS 接口相比,JESD204B 数据转换器串行接口标准可提供一些显著的优势,包括更简单的布局以及更少

2018-09-18 11:29:29

处理模块之间的任何延迟失配都会使性能下降。对 于交错式处理而言,样本对齐同样是必需的;在交错式处 理时,一个转换器样本后紧跟另一个样本,且时间仅为一 个时钟周期中的一小部分。JESD204B第三代高速串行

2018-10-15 10:40:45

in JESD204B high speed serial interfaces for data converters. This reference design features the ADC16DX370, a

2018-08-09 08:40:10

jesd204B调试经验有哪些?注意事项是什么?

2021-06-21 06:05:50

我最近尝试用arria 10 soc实现与ad9680之间的jesd204B协议,看了很多资料,却依然感觉无从下手,不知道哪位大神设计过此协议,希望可以请教一番,在此先谢过。

2017-12-13 12:47:27

因实际需求,本人想使用JESD204b的ip核接收ADC发送过来的数据,ADC发送的数据链路速率是15gbps, 厂家说属于204b标准。我看到jesd204b的ip核标准最大是12.5gbps,但是支持的支持高达16.375 Gb/s的非标准线速率。请问我可以使用这个IP核接收ADC的数据吗?

2020-08-12 09:36:39

作者:George Diniz,ADI公司高速数据转换器部产品线总监JESD204B简介开发串行接口业界标准JESD204A的目的在于解决以高效率且省钱的方式互连最新宽带数据转换器与其他系统IC

2019-05-29 05:00:04

AD9164 JESD204B接口的传输层是如何对I/Q数据进行映射的

2023-12-04 07:27:34

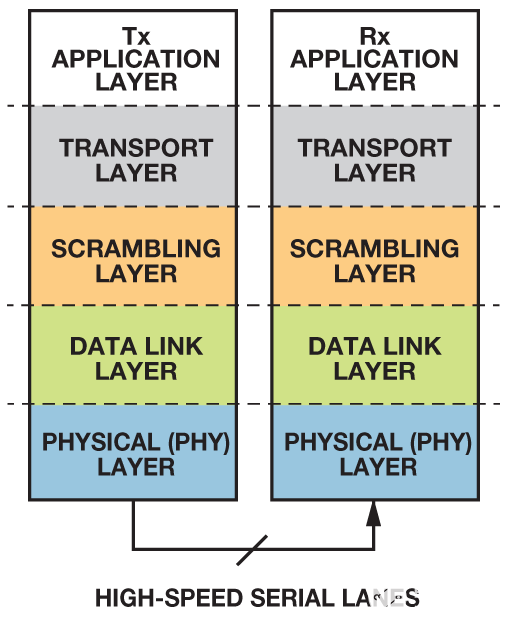

、什么是JESD204B协议该标准描述的是转换器与其所连接的器件(一般为FPGA和ASIC)之间的数GB级串行数据链路,实质上,具有高速并串转换的作用。2、使用JESD204B接口的原因a.不用再使用数据接口时钟

2019-12-04 10:11:26

。与LVDS及CMOS接口相比,JESD204B数据转换器串行接口标准可提供一些显着的优势,比如更简单的布局以及更少的引脚数。也因此它获得了更多工程师的青睐和关注,它具备如下系统级优势:1、更小的封装尺寸

2019-12-03 17:32:13

使用AD9680时遇到一个问题,AD9680采样率为1Gsps,JESD204B IP核的GTX参考时钟为250MHz,参数L=4,F=2,K=32,线速率为10Gbps,使用的为SYSREF

2023-12-12 08:03:49

使用AD9680时遇到一个问题,AD9680采样率为1Gsps,JESD204B IP核的GTX参考时钟为250MHz,参数L=4,F=2,K=32,线速率为10Gbps,使用的为SYSREF

2018-08-08 07:50:35

JESD204B到底是什么呢?是什么导致了JESD204B标准的出现?什么是JESD204B标准?为什么关注JESD204B接口?

2021-05-24 06:36:13

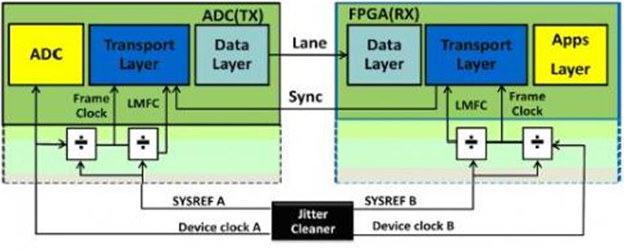

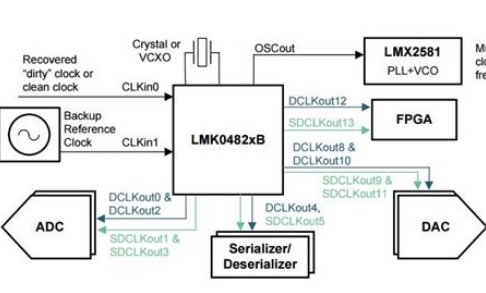

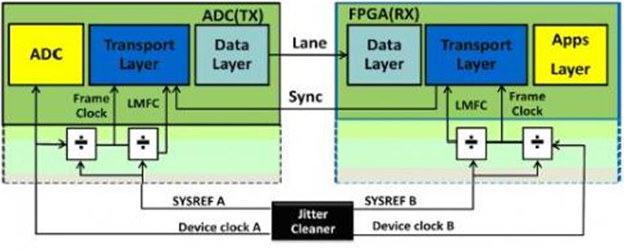

时钟网络。一,JESD204B时钟网络原理概述 本文以JESD204B subclass1来讨论时钟的时序需要以及TI时钟芯片方案的实现。任何一个串行协议都离不开帧和同步,JESD204B也不例外,也

2019-12-17 11:25:21

关于JESD204B接口你想知道的都在这

2021-09-29 06:56:22

具有可重复的确定性延迟。随着转换器的速度和分辨率不断提升,JESD204B接口在ADI高速转换器和集成RF收发器中也变得更为常见。此外,FPGA和ASIC中灵活的串行器/解串器(SERDES)设计正逐步

2018-10-16 06:02:44

描述JESD204B 链路是数据转换器数字接口的最新趋势。这些链路利用高速串行数字技术提供很大的益处(包括增大的信道密度)。此参考设计解决了其中一个采用新接口的挑战:理解并设计链路延迟。一个示例实现

2018-11-21 16:51:43

JESD204B数模转换器的时钟规范是什么?JESD204B数模转换器有哪些优势?如何去实现JESD204B时钟?

2021-05-18 06:06:10

的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA一直支持千兆串行/解串(SERDES)收发器。然而在过去,大多数ADC

2021-04-06 09:46:23

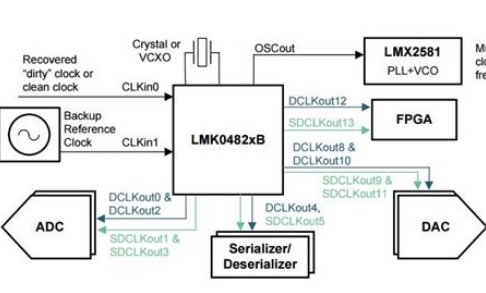

LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们是高性能的双环路抖动清除器,可在具有器件和SYSREF时钟的子类1时钟方案里驱动多达七个JESD204B转换器或逻辑器件。图1是典型

2022-11-18 06:36:26

,JESD204支持的每通道串行链路速率是LVDS的三倍以上。当比较诸如多器件同步、确定延迟和谐波时钟等高级功能时,JESD204B是提供这些功能的唯一接口。所有通路和通道对确定延迟敏感、需要宽带宽多通道转换器

2021-11-03 07:00:00

JESD204b接口已经在国内好几年,但是几乎没有一篇文章和其实际应用相关。其实对于一个关于JESD204b接口ADC项目来讲一共大致有5个部分:ADC内核,ADC的JESD接口,[color

2017-08-09 20:33:19

DC1974A-C,LTC2122演示板,14位,170Msps双通道ADC,带JESD204B输出。演示电路1974A-C支持具有符合JESD204B标准的CML输出的LTC2122,14位双

2019-06-20 08:05:16

时“write_bitstream -force jesd204_tx_example_design.bit”我的许可证经理似乎表明我们的JESD204B核心许可证仍然有效(至少到2013年12月)。许可证管理器显示IP

2018-12-10 10:39:23

中,笔者将谈论抖动合成器与清除器的不同系统参考信号(SYSREF)模式,以及如何用它们来最大限度地提高JESD204B时钟方案的性能。 LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们

2018-09-06 15:10:52

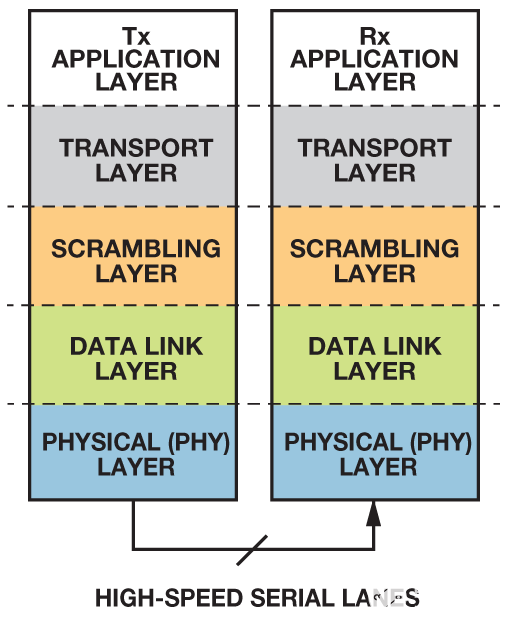

建立了所需的电气连接,如图 1 所示。请注意图中箭头表示信号方向。图1 —JESD204B TX 至RX 链路的信号连接从 TX (tx_dataout) 到 RX 的信号是包含数据链路的串行解串器信道

2018-09-13 09:55:26

连接,如图 1 所示。请注意图中箭头表示信号方向。图 1 — JESD204B TX 至 RX 链路的信号连接从 TX (tx_dataout) 到 RX 的信号是包含数据链路的串行解串器信道信号。这些

2022-11-21 07:18:42

你好,我试图仅在测试模式下测试JESD204B v6.2:001:无限期地发送/接收/K28.5/但首先在desing块中有一个错误:[BD 41-967] AXI接口引脚/ jesd204

2019-04-19 13:06:30

探讨如何同步多个带JESD204B 接口的模数转换器 (ADC) 以便确保从 ADC 采样的数据在相位上一致。特性同步 2 个采样频率为 3.072GHz 的千兆采样 ADC系统可扩展到超过 2 个

2022-09-19 07:58:07

多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏斜。此设计经过 TI

2018-12-28 11:54:19

JESD204 LogiCORE™ IP和ADI AD9250模数高速数据转换器之间的JESD204B实现互操作。实现逻辑和数据转换器器件之间的JESD204B互操作性,是促进该新技术广泛运用的一个重大里程碑。

2013-10-09 11:10:34 1956

1956 Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。

2013-10-17 16:35:20 909

909 随着数模转换器的转换速率越来越高, JESD204B 串行接口已经越来越多地广泛用在数模转换器上,其对器件时钟和同步时钟之间的时序关系有着严格需求。本文就重点讲解了JESD204B 数模转换器的时钟规范,以及利用 TI 公司的芯片实现其时序要求。

2016-12-21 14:39:34 44

44 在使用我们的最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。此外,我还在 E2E

2017-04-08 04:48:17 2131

2131

。随着转换器的速度和分辨率不断提升,JESD204B接口在ADI高速转换器和集成RF收发器中也变得更为常见。

2017-04-12 10:22:11 14645

14645

本设计致力于用SystemC语言建立JESD024B的协议标准模型,描述JESD204B的所有行为,并且能够保证用户可以通过该JESD204B的SystemC库,进行JESD204B行为的仿真

2017-11-17 09:36:56 3002

3002

在本文中,笔者将谈论抖动合成器与清除器的不同系统参考信号(SYSREF)模式,以及如何用它们来最大限度地提高JESD204B时钟方案的性能。 LMK04821系列器件为该话题提供了很好的范例研究素材

2017-11-17 10:31:45 3009

3009

在从事高速数据撷取设计时使用FPGA的人大概都听过新JEDEC标准「JESD204B」的名号。近期许多工程师均联络德州仪器,希望进一步了解 JESD204B 接口,包括与FPGA如何互动、JESD204B如何让他们的设计更容易执行等。本文介绍 JESD204B标准演进,以及对系统设计工程师有何影响。

2017-11-18 02:57:01 13942

13942 随着数模转换器的转换速率越来越高,JESD204B 串行接口已经越来越多地广泛用在数模转换器上,其对器件时钟和同步时钟之间的时序关系有着严格需求。本文就重点讲解了JESD204B 数模转换器的时钟

2017-11-18 08:00:01 1831

1831 JESD204B是最新的12.5 Gb/s高速、高分辨率数据转换器串行接口标准。转换器制造商的相关产品已进入市场,并且支持JESD204B标准的产品预计会在不久的将来大量面世。JESD204B接口

2017-11-18 18:57:16 2789

2789

Arria10接口的JESD204B与ADI9144的互操作性

2018-06-20 00:06:00 4053

4053

该视频将为观众介绍JESD204B接口中的眼图测量。

2019-08-01 06:19:00 3157

3157 该视频将为观众介绍JESD204B接口中的眼图测量。

2019-08-19 06:06:00 4377

4377 來自ADI公司和Xilinx公司的專家齊聚一堂,共同展示兩種JESD204B A/D轉換器至FPGA設計,同時介紹其實現技巧。

2019-07-03 06:14:00 1959

1959 來自ADI公司和Xilinx公司的專家齊聚一堂,共同講解JESD204B介面標準的重要性,同時介紹它在A/D轉換器到FPGA設計中的作用。

2019-07-03 06:13:00 1291

1291 ADI Jesd204B在线研讨会系列第4讲,讨论确定性延迟和多芯片同步,以及在ADI转换器产品中的实现方式。

2019-06-11 06:16:00 2259

2259

Validating ADI Converters Inter-operability with Xilinx FPGA and JESD204B/C IP

2021-02-19 16:05:33 11

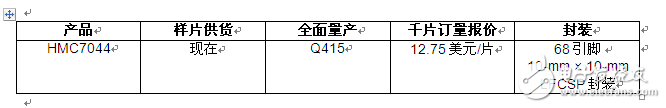

11 HMC7044: 带 JESD204B 接口的高性能、3.2 GHz、14 路输出抖动衰减器

2021-03-21 11:14:44 11

11 验证ADI转换器与Xilinx FPGA和JESD204B/C IP的互操作性

2021-04-09 14:37:51 13

13 LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表

2021-04-22 15:52:09 9

9 LTC2122:带JESD204B串行输出的双14位170 Msps ADC数据表

2021-05-09 21:06:02 11

11 带JESD204B串行接口的14位250 Msps ADC系列

2021-05-18 15:04:50 7

7 LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持数据表

2021-05-19 15:23:53 14

14 LTC2123:带JESD204B串行输出的双14位250 Msps ADC数据表

2021-05-24 08:01:59 8

8 它如何同 FPGA 协作。他们特别感兴趣的是 JESD204B 接口将如何简化设计流程。

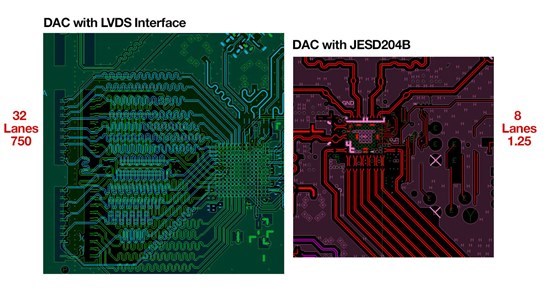

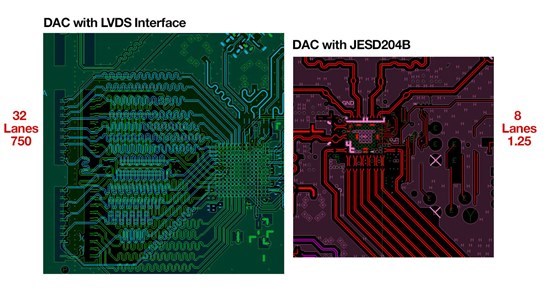

与 LVDS 及 CMOS 接口相比,JESD204B 数据转换器串行接口标准可提供一些显著的优势,包括更简单

2021-11-10 09:43:33 528

528

明德扬的JESD204B采集卡项目综合上板后,可以使用上位机通过千兆网来配置AD9144和AD9516板卡,实现高速ad采集。最终可以在示波器和上位机上采集到设定频率的正弦波。本文重点介绍JESD204B时钟网络。

2022-07-07 08:58:11 1296

1296

本文余下篇幅将探讨推动该规范发展的某些关键的终端系统应用,以及串行低压差分信号(LVDS)和JESD204B的对比。

2022-08-05 14:18:00 1105

1105

如何构建您的JESD204B 链路

2022-11-04 09:52:11 3

3 理解JESD204B协议

2022-11-04 09:52:12 3

3 JESD204B:适合您吗?

2022-11-07 08:07:23 0

0 JESD204A/JESD204B串行接口行业标准旨在解决以高效和节省成本的方式将最新的宽带数据转换器与其他系统IC互连的问题。其动机是标准化接口,通过使用可扩展的高速串行接口,减少数据转换器与其他设备(如现场可编程门阵列(FGPA)和片上系统(SoC))设备)之间的数字输入/输出数量。

2022-12-21 14:44:20 966

966

JESD204B接口一般用在高速的AD和DA芯片上,用于传输采集到的数据。该接口相比LVDS可以减少大量的IO管脚,所以正在逐步取代LVDS接口(引用wp446-jesd204b.pdf)。

2022-12-22 09:45:18 1771

1771 JESD204是一款高速串行接口,用于将数据转换器(ADC和DAC)连接到逻辑器件。该标准的修订版B支持高达12.5 Gbps的串行数据速率,并确保JESD204链路上的可重复确定性延迟。随着转换器速度和分辨率的不断提高,JESD204B接口在ADI公司的高速转换器和集成RF收发器中变得越来越普遍。

2023-01-09 16:41:38 2968

2968

LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们是高性能的双环路抖动清除器,可在具有器件和SYSREF时钟的子类1时钟方案里驱动多达七个JESD204B转换器或逻辑器件。图1是典型JESD204B系统(以LMK04821系列器件作为时钟解决方案)的高级方框图。

2023-04-18 09:25:30 919

919

德赢Vwin官网

网为你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相关产品参数、数据手册,更有AD9207

2023-10-16 19:02:55

德赢Vwin官网

App

德赢Vwin官网

App

评论