CXL (Compute Express Link) 技术是一种新型的高速互联技术,旨在提供更高的数据吞吐量和更低的延迟,以满足现代计算和存储系统的需求。它最初由英特尔、AMD和其他公司联合推出,并得到了包括谷歌、微软等公司在内的大量支持。

一、CXL介绍

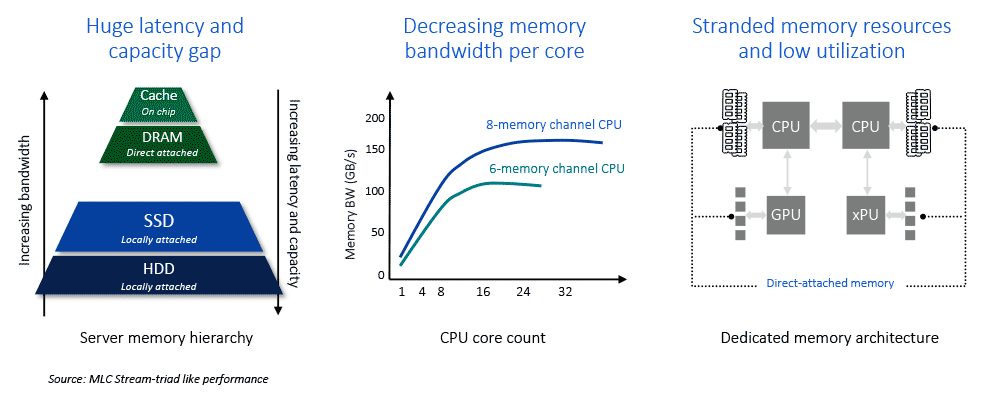

CXL的目标:解决CPU和设备、设备和设备之间的内存鸿沟。服务器有巨大的内存池和数量庞大的基于PCIe运算加速器,每个上面都有很大的内存。内存的分割已经造成巨大的浪费、不便和性能下降。CXL就是为解决这个问题而诞生。

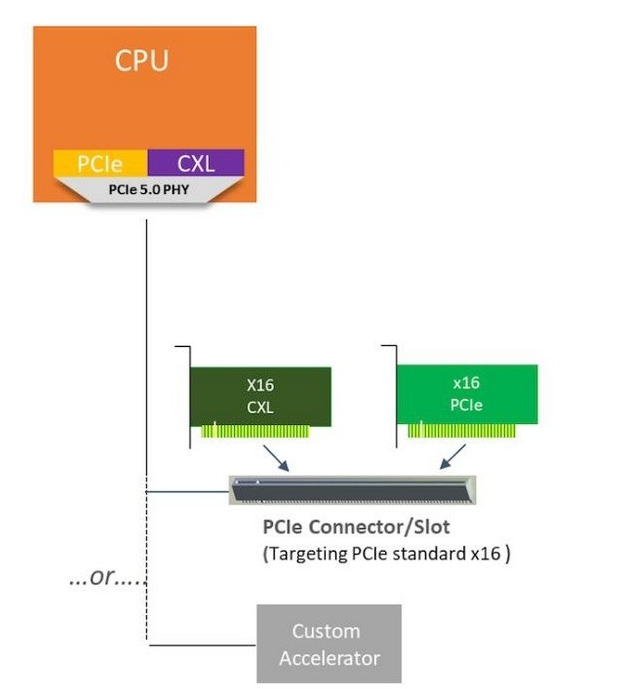

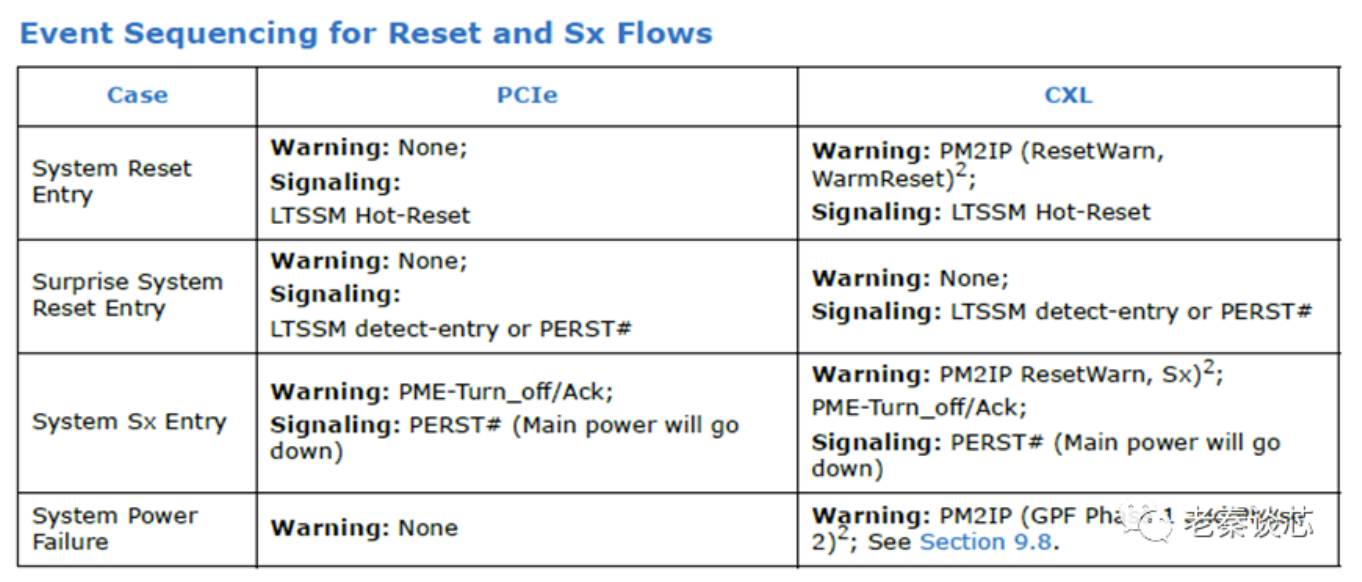

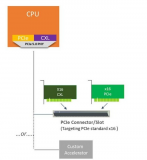

CXL技术的背景可以追溯到PCIe (Peripheral Component Interconnect Express) 技术,PCIe是用于连接计算机内部组件的一种标准接口技术。PCIe设备可以发起一个DMA来访问内存,只要知道目标物理地址即可。在CXL之前就有以IBM牵头的OpenCAPI,ARM为代表支持的CCIX,AMD等支持的GenZ和Nvidia自行提出的Nvlink等等多种协议。虽然PCIe已经有了很多改进,但其难以满足现代计算机处理器和加速器之间的高带宽、低延迟通信需求。于是,CXL技术应运而生。

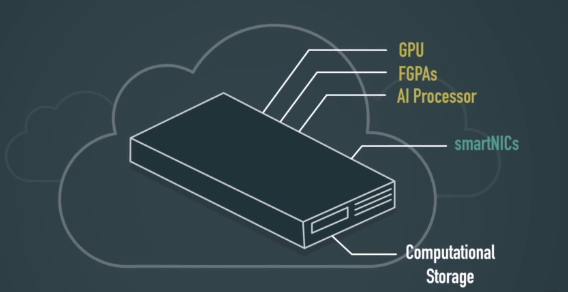

CXL技术的应用场景非常广泛,其中包括数据中心、人工智能和处理器互联等领域。在数据中心领域,CXL技术可以将不同的计算和存储资源进行互联,提高系统性能和效率。在人工智能领域,CXL技术可以使GPU和FPGA等加速器更好地与主处理器进行协作,提高AI模型训练和推理的速度。在处理器互联方面,CXL技术可以实现不同厂商的处理器之间的互联,提高系统的整体性能和灵活性。

二、CXL技术概览

2.1、什么是CXL技术?

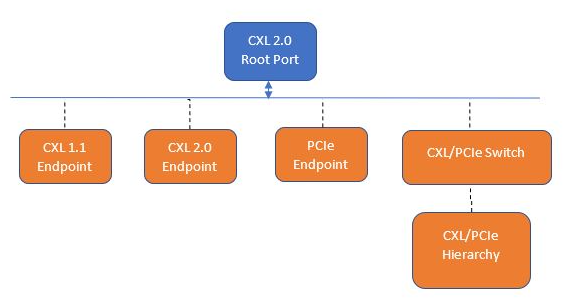

CXL(Compute Express Link)是一种高速串行协议,它允许在计算机系统内部的不同组件之间进行快速、可靠的数据传输。CXL在2020年推出,由英特尔、戴尔和惠普等公司共同设计。它旨在解决高性能计算中的瓶颈问题,包括内存容量、内存带宽和I/O延迟等问题。CXL还可以实现内存扩展和内存共享,并且可与计算加速器(如GPU、FPGA)等外设通信,提供更快、更灵活的数据交换和处理方式。

CXL技术不仅提供了高速传输,还支持内存共享和虚拟化,使设备之间的协作更加紧密和高效。这种技术有助于满足现代数据中心对大规模处理和分析的需求,同时也能够为AI、机器学习、区块链等新兴应用提供更好的支持。

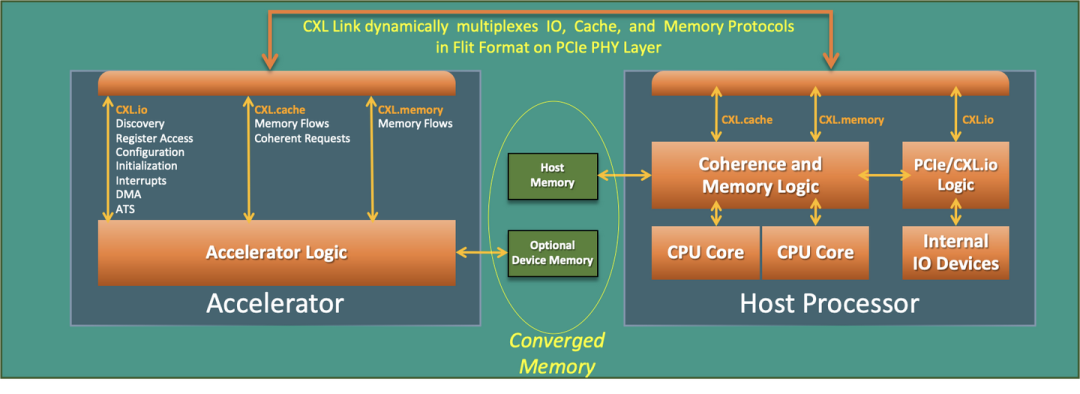

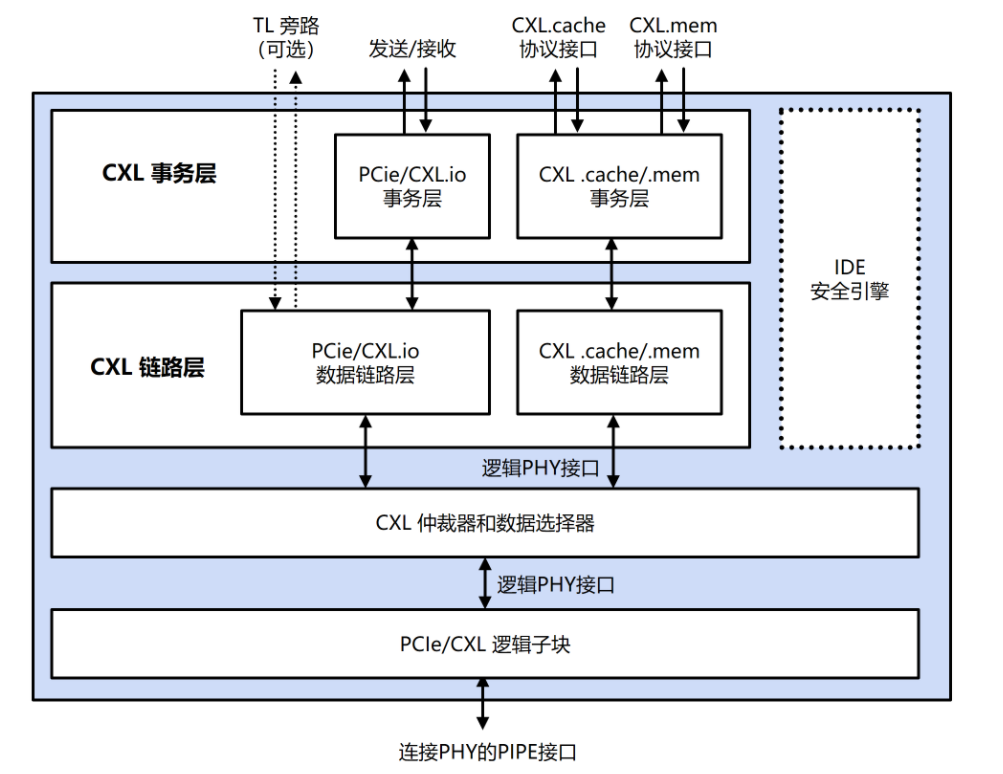

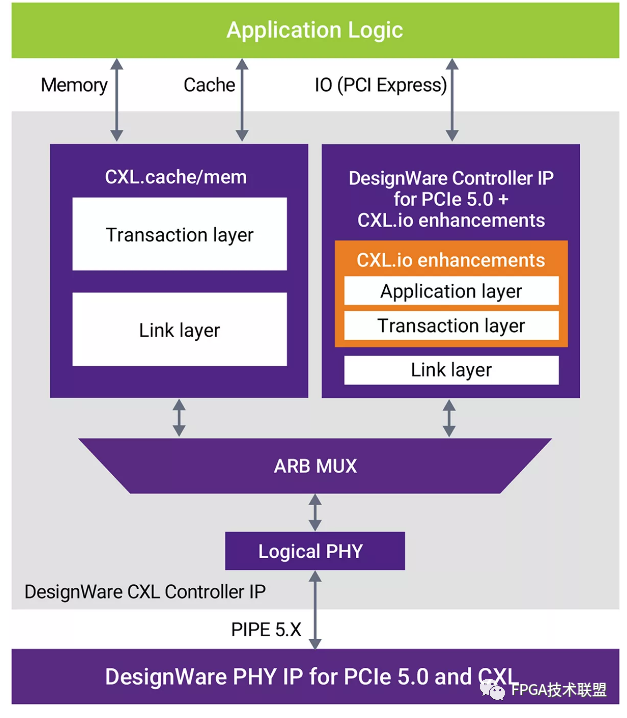

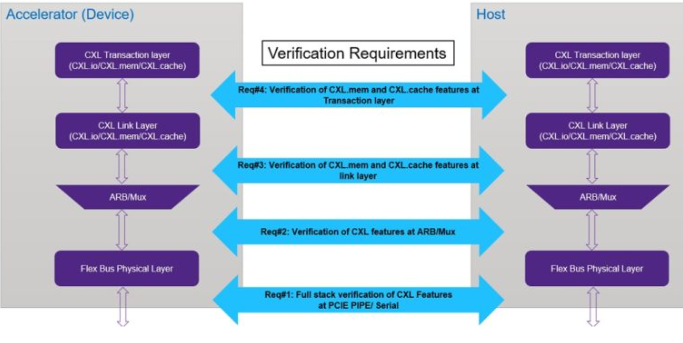

2.2、CXL技术的三种模式:http://CXL.io、CXL.cache和CXL.memory

CXL协议包含三个子协议:

http://CXL.io:这种模式可以将内存扩展到外部设备,使得数据的传输速度更快。http://

CXL.io通过PCIe总线连接CPU和外部设备,这样CPU就可以与外部设备共享内存,并且可以直接访问外部设备的I/O资源。

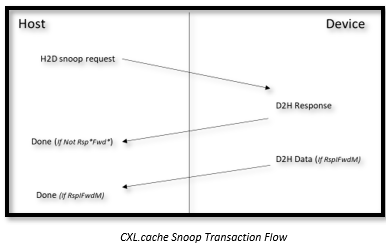

CXL.cache:这种模式可以通过将内存缓存到外部设备中来提高性能。CXL.cache模式允许CPU在本地缓存中保留最常用的数据,而将不常用的数据保存在外部设备中。这样可以减少内存访问时间,提高整体系统性能。

CXL.memory:这种模式可以将外部设备作为主内存使用,从而实现更大的内存容量。CXL.memory模式允许CPU将外部设备看作是扩展内存,从而可以存储更多的数据。这种方式可以提高系统的可靠性,因为即使发生了内存故障,CPU仍然可以通过外部设备继续运行。

http://CXL.io是Compute Express Link(CXL)规范中定义的物理层接口,可以提供比传统PCIe更低的延迟、更高的带宽和更好的可扩展性。

http://CXL.io通过使用SerDes技术(一种将串行数据转换为并行数据以及反向转换的技术),在单个物理通道上同时传输多个不同的数据流。这些数据流可以包括带宽密集型的数据流、低延迟的命令和控制信息以及配置寄存器和状态信息。http://CXL.io还支持热插拔和链路训练等高级特性。 http://CXL.io的物理层规范定义了信号的电气特性、时序要求和连接器接口,以确保高可靠性和高性能。http://CXL.io采用4x25Gbps或3x32Gbps的信号速率,并支持单向或双向通信。连接器方面,http://CXL.io采用40个针脚的SMT连接器,其中27个针脚用于数据传输,其余用于电源、地线和时钟信号。

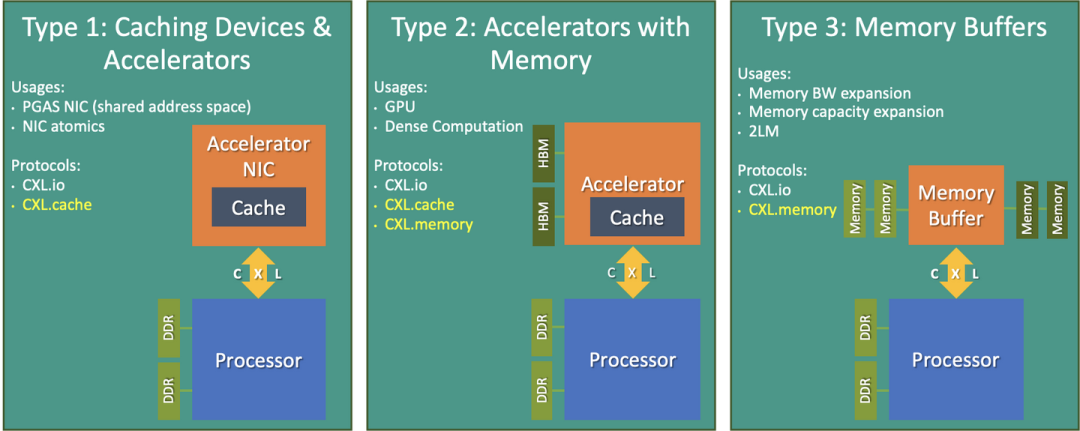

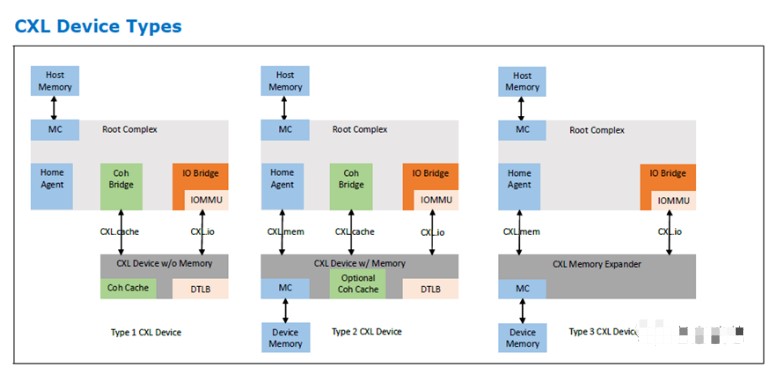

CXL技术的三种类型:

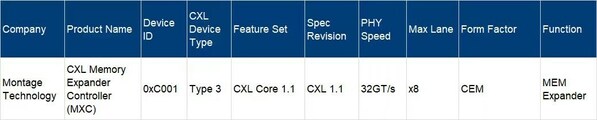

Type 1:通过 PCIe 插槽安装的加速卡或附加卡。这些卡可以与现有系统集成,并通过 CXL 接口与 CPU 直接通信以提供更快的数据传输速度。用于网卡这类高速缓存设备。

Type 2:具有所有 Type 1 设备的功能,通常用于具有高密度计算的场景。比如 GPU 加速器。

Type 3:一种专用的存储设备,与主机处理器直接通信,并且可以使用 CXL 协议来实现低延迟、高吞吐量的数据传输。用作内存缓冲器,用于扩展内存带宽和内存容量。

三、CXL技术的优势

更快的数据传输速度:CXL技术可以实现高达25GB/s的数据传输速度,比目前常用的PCIe 4.0技术还要快。这意味着在数据中心等高性能应用场景下,可以更快地进行数据处理和传输。

更低的延迟:CXL技术可以将CPU、GPU、FPGA等计算设备与内存直接连接,避免了传统的I/O总线带来的时延,从而实现更低的延迟,提高了计算效率。

更高的能效:CXL技术支持在多台计算设备之间共享内存,降低了内存冗余,提高了能效。此外,CXL技术还支持内存虚拟化,可以根据应用负载动态分配内存资源,进一步提高了系统能效。

更强的可扩展性:CXL技术可以支持内存扩展,允许在不停机的情况下添加更多的内存容量,从而增加系统的可扩展性,为未来的应用需求做好准备。

更广泛的应用场景:CXL技术不仅适用于数据中心等高性能计算领域,还可以应用于人工智能、区块链、物联网等多个领域。

一句话:支持高带宽、低延迟数据传输、具有更好的灵活性和可扩展性、可以实现混合使用不同类型的硬件设备。

四、CXL技术的应用

4.1、计算机系统中的应用

CXL可以用于计算机系统中的许多应用:

高性能计算:CXL可以提供低延迟、高带宽的协议,可用于连接CPU、GPU、FPGA等处理器,在高性能计算中提供更快的数据传输。

存储加速:CXL可以用于连接存储设备,如SSD和NVMe驱动器,以提供更快的存储访问速度。此外,CXL还可以与内存控制器集成,为存储加速提供更大的带宽。

人工智能:CXL可用于连接AI芯片,以提供更快的数据传输,从而提高AI工作负载的性能和效率。

网络加速:CXL还可以用于连接网络适配器,以提供更快的网络传输速度,从而提高网络应用程序的性能。

4.2、数据中心中的应用

在数据中心中,CXL可以应用于以下方面:

高性能计算:CXL可以提供比传统PCIe更快的数据传输速度和更低的延迟,从而提高高性能计算的效率和吞吐量。

存储加速:CXL可以将存储加速器与主机CPU直接连接,从而实现更快的数据访问和更高的IOPS,提高存储性能。

AI加速:CXL可以将AI加速器与CPU/GPU/FPGA等处理器直接连接,实现更快的模型训练和推理速度,提高人工智能应用的性能。

大规模虚拟化:CXL可以将多个CPU和内存资源组合成一个大规模虚拟化集群,从而提高资源利用率和灵活性,并降低虚拟化管理的复杂性。

4.3、人工智能领域中的应用

在人工智能领域中,CXL可以发挥以下作用:

提高数据传输效率:对于深度学习等任务,需要大量的数据传输和计算,在传统的PCIe互连中,由于数据传输速度慢,往返延迟高,会导致计算效率低下。而使用CXL互连,可以实现低延迟、高速的数据传输,提高计算效率。

加速模型训练:随着深度学习模型变得越来越复杂,需要更多的计算资源来进行训练。使用CXL互连,可以将CPU、GPU和其他加速器设备进行紧密协作,提高模型训练的速度和效率。

实现AI与物联网的集成:CXL技术可以使AI应用程序直接连接到物联网设备,实现更快速的数据处理和响应。这对于需要快速响应的实时应用程序非常重要。

降低能源消耗:CXL技术可以减少传输数据所需的功耗,同时还可以减少系统中的数据缓存,从而实现更高效的能源管理。

五、CXL技术与其他技术的对比

与PCIe、NVMe等技术的对比:

带宽:CXL的带宽比PCIe高得多,CXL 2.0标准最高可以达到32 GT/s,而PCIe 5.0的带宽只能达到16 GT/s。相比之下,NVMe是一种协议而非互连技术,其带宽取决于所使用的互连技术。

延迟:CXL和PCIe都具有低延迟的特点,但CXL在延迟方面稍微优于PCIe。NVMe协议在延迟方面表现良好。

功能:CXL支持内存扩展、缓存一致性和设备直接内存访问等功能,这些功能不是PCIe或NVMe所具备的。

应用场景:PCIe主要用于连接外部设备,如GPU、网卡和存储设备。NVMe主要用于连接固态硬盘。而CXL则更加灵活,可用于连接处理器、存储设备、网络适配器和其他外围设备,适用范围更广。

兼容性:由于CXL是相对较新的技术,许多旧设备可能无法与其兼容。PCIe则已经成为了一种通用的连接标准,并且得到广泛应用。

成本:目前来看,CXL硬件和设备的成本相对较高,而PCIe则更加普及和经济实惠。

CXL和CCIX都是用于连接不同芯片之间的高速互联标准,但它们在一些方面存在差异。以下是CXL与CCIX的主要对比:

性能:CXL标准提供了更高的带宽和更低的延迟,使其在高性能计算、机器学习、人工智能等领域中具有优势。而CCIX标准则专注于低功耗和高可靠性,适用于物联网、移动设备等场景。

兼容性:CXL标准基于PCI Express协议,因此与现有的PCIe接口兼容。而CCIX标准则需要使用新的物理层和控制层,在一定程度上限制了其兼容性。

应用场景:CXL标准适用于需要高性能和更强的内存扩展的场景,例如大型服务器集群和超级计算机。而CCIX标准则适用于需要低功耗和高可靠性的场景,例如数据中心、物联网、移动设备等。

支持的架构:CXL支持x86、Power和ARM等多种处理器架构。而CCIX则专注于ARM和Power架构,对于x86架构的支持有限。

六、实现CXL技术的挑战及解决方案

CXL技术的实现面临以下挑战:

复杂性:CXL技术的实现需要高度复杂的系统设计和集成,这意味着需要适应不同的硬件、软件和工具。

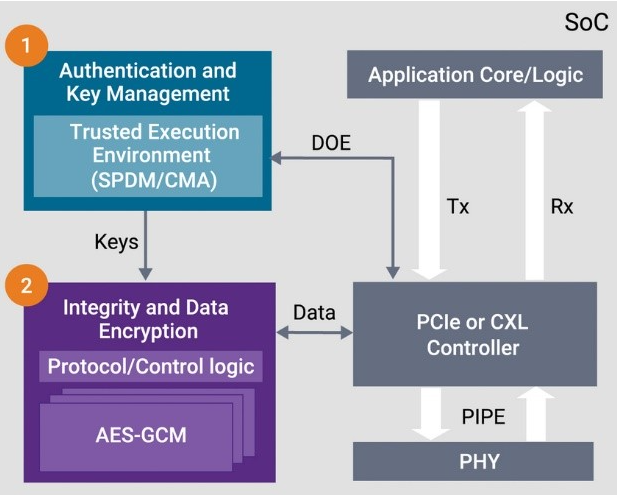

安全性:由于CXL技术涉及到底层硬件操作,并且可能涉及多个设备之间的数据共享,因此安全风险是一个重要考虑因素。需要采取适当的措施确保数据安全和隐私。

性能:CXL技术需要提供高速数据传输和低延迟,以满足对计算能力和存储能力的要求。这需要高效的协议和优化的硬件和软件设计。

兼容性:CXL技术需要与现有的接口和协议兼容,以支持旧设备和系统的升级。这需要适当的转换器和中间件。

为了解决这些挑战,可以采取以下方案:

标准化:制定统一的标准和规范,以确保不同厂商的设备和系统之间的兼容性和互操作性。

优化设计:通过优化硬件和软件设计,提高性能和安全性。例如,增加硬件加速、内存缓存和错误纠正功能。

管理数据共享:采取适当的措施来管理设备之间的数据共享,例如访问控制、认证和加密。

提供中间件:提供转换器和中间件,以支持现有系统的升级和兼容性。

七、结论

更广泛的应用场景:随着数据中心越来越重要,CXL技术将在更多的应用场景中得到应用,比如超级计算机、AI加速器、网络加速器、NVMe SSD等。

更高的带宽和更低的延迟:CXL技术支持更高的带宽和更低的延迟,这使得它在处理大规模数据时具有优势。

更好的内存扩展性:CXL技术允许多个设备共享同一块内存,这极大地提高了内存扩展性和灵活性,在大型计算集群和超级计算机中应用前景广阔。

更好的兼容性:由于CXL技术基于PCIe协议,因此与现有的PCIe接口兼容。这使得CXL技术具有更好的兼容性和可扩展性。

面向不同处理器架构:CXL技术可以支持x86、ARM和Power等不同的处理器架构,这为不同的系统提供了更多的选择。

编辑:黄飞

德赢Vwin官网

App

德赢Vwin官网

App

评论