本文提出了一种基于FPGA的多路光栅信号采集方案,该方案使用I/O口相对较少的低端FPGA,配合多路选择开关,通过内部处理,实现了多路光栅信号的采集,结果表明,该方案成本低廉且能满足精度的要求。

2013-12-30 13:35:40 2174

2174

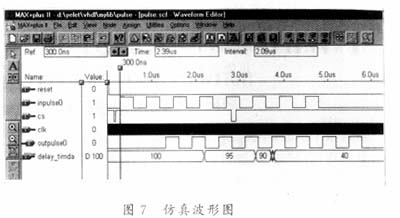

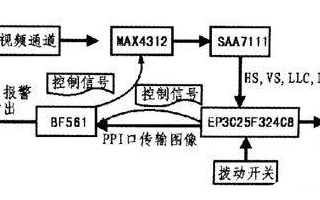

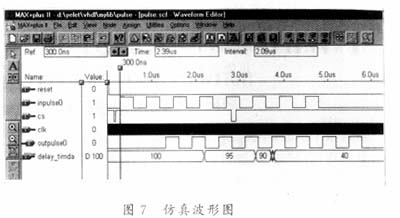

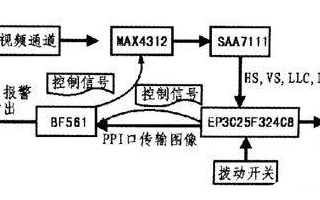

本文以FPGA作为核心处理器,提出了一种基于FPGA多路机载冗余图像处理系统的设计方案。##整个系统显示的分辨率为1600×1200@60 Hz,信号位为真彩色24b,则一帧图像所需需要存储的容量C≈47 Mb。##读写操作交替进行仿真图如图5所示。图5中包含了两个写入操作,一个读取操作。

2014-01-07 10:28:32 2802

2802

多道脉冲幅度分析仪和射线能谱仪是核监测与和技术应用中常用的仪器。##FPGA

2014-06-09 10:42:39 1286

1286

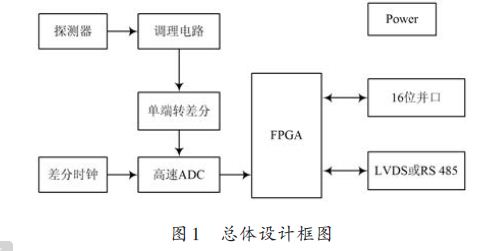

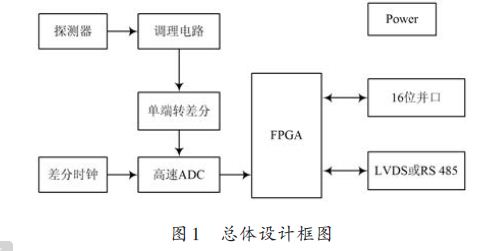

基于FPGA 的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。

2015-02-03 09:55:05 1870

1870

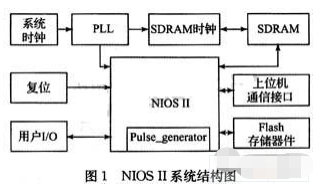

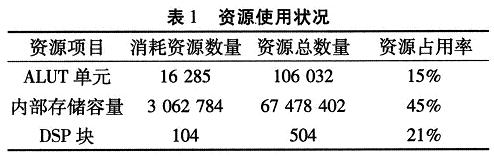

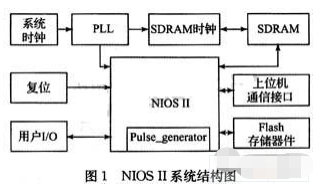

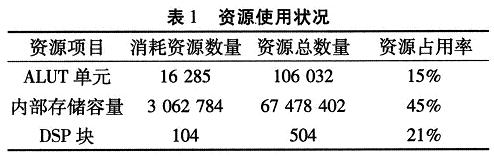

只有设计出了高频率的、参数化的脉冲发生器,脉冲加工电源的精度、参数化才可以实现。该电源系统中采用的是性价比较好的Altera公司的Cyclone II序列的FPGA芯片EP2C8Q208C7。其逻辑资源足够实现系统的功能。

2021-02-23 10:01:45 3091

3091

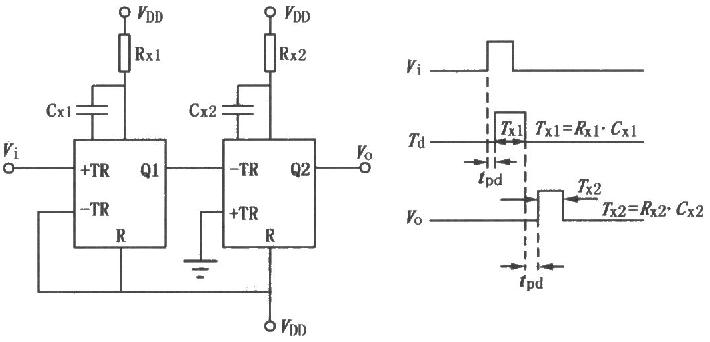

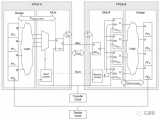

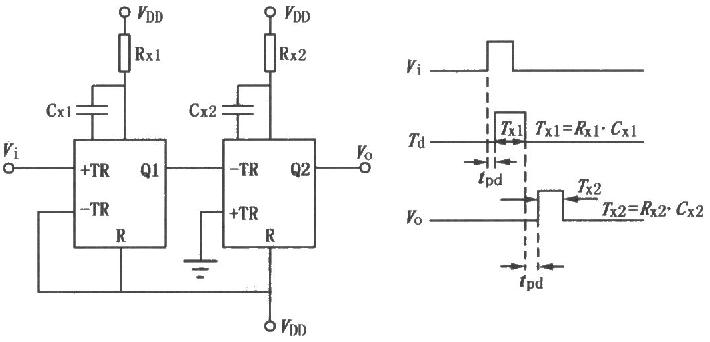

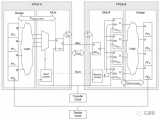

多片FPGA之间的互连,经常提到多路复用的概念,也经常提到TDM的概念,正确理解多路复用在多片FPGA原型验证系统中的机理,尤其是时序机制,对于我们正确看待和理解多片FPGA原型系统的性能有很好的促进作用。下图是一个使用多路复用器后接采样FF的多路复用解决方案的示例。

2023-06-06 10:04:35 579

579

如题,小弟最近做一个用FPGA驱动电机的板子,用STM32把FPGA需要发出的脉冲的宽度和个数都计算好,然后用8位的并口,通过一个时钟上升沿写进FPGA,在FPGA内部进行运算之后发出脉冲,刚开始

2019-01-28 00:41:02

用的ALTREA的FPGA,系统时钟50MHz,下降沿检测,检测50Hz脉宽为20us,下降沿时间为1.5us。结果,我只有把被检测的脉冲频率调到5Hz下,才能够检测的到。望高手指点。

2011-06-16 22:37:12

在FPGA的设计中,毛刺现象是长期困扰电子设计工程师的设计问题之一,是影响工程师设计效率和数字系统设计有效性和可靠性的主要因素。由于信号在FPGA的内部走线和通过逻辑单元时造成的延迟,在多路信号变化

2012-09-06 14:37:54

该文档为基于FPGA的多路模拟数据采集接口设计讲解文档,介绍一种基于 8,RQ 的多路模拟数据采集接口的设计方案。该方案使用Max1281 作为模数转换芯片,在 APA150 FPGA 中设计和实现了相关的接口控制、配置和数据存储模块;给出了系统设计框图、FPGA开发要点和仿真波形。

2018-09-21 14:37:00

。多路红外系统组成如图1所示。 红外遥控发射电路的功能是对输入控制指令信号进行扫描、产生遥控编码脉冲、驱动红外发射管输出红外遥控信号。红外遥控接收电路的功能是接收红外遥控信号并将之放大、检波、整形

2018-11-05 16:09:43

有没有做过用STM32单片机多路脉冲计数,5路到9路,用16位计数器,哪个型号的有这个资源?

2016-09-13 17:15:45

FPGA和高速ECL器件的合成脉冲脉宽的调整方案,通过FPGA内部计数器和可编程延迟芯片的共同配合实现了脉冲宽度的大范围精密连续可调的目标,并详细论述了电路的基本原理及硬件的基本组成。通过实验验证,该方案

2010-05-06 08:57:59

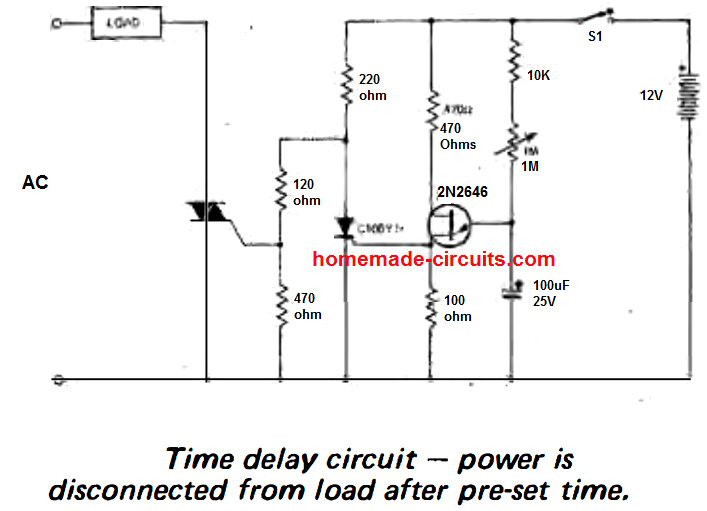

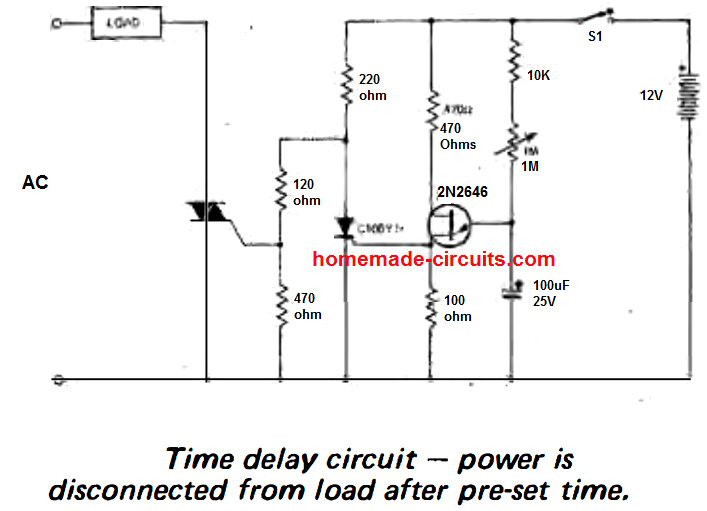

请教各位大神,如图,这个是延迟关断灯的电路,请问这个电路开始按下开关的时候,可控硅是怎么打开的,电路的上可控硅的G极我看不出来有正向的电压啊。。。。2个稳压管的参数我是随便写的,可以的话帮忙算下稳压管大概多少值的。手上没工具测。

2023-10-24 16:05:18

为了提高系统的集成度,同时兼顾精度,介绍用FPGA延迟线插入法来实现较高精度的脉冲激光测时、测距的原理和技术途径。FPGA延迟线插入法是在直接计数法的基础上,采用FPGA内部延时单元将时间间隔转化

2010-05-13 09:04:22

FPGA+DSP构成的光纤传感信号实时处理系统的硬件及软件设计.并针对载波相位延迟造成的解调信号幅度衰减提出了解决方法。本系统具有高速实时数据运算能力。可广泛应用于多路数据采集处理等领域,可升级能力强,应用前景

2021-07-05 11:23:33

时间。针对上述研究现状和分布式采集场景分析,本文介绍了一种基于FPGA和TOE架构,实现TCP/IP协议数据传输的多路采集与切换系统。该系统涉及并行数据采集、多路通道切换、TCP/IP协议通信等模块

2021-07-12 08:30:00

系统的效率和功能可以得到最大限度的提高。 在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形。本文用Altera公司FPGA产品开发工具QuartusⅡ,设计了6路PWM输出接口,并

2019-05-06 09:18:16

)工具给电子设计带来了巨大变革,在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形,这可通过FPGA丰富的硬件资源和可以配置I/O引脚来实现。嵌入式系统中FPGA的应用设计关键是系统

2019-04-25 07:00:05

基于FPGA的多路回声消除算法的实现中文期刊文章作 者:尹邦政 朱静 毛茅作者机构:[1]广州广哈通信股份有限公司,广东广州510663;[2]广州大学实验中心,广东广州510006出 版 物

2018-05-08 10:23:36

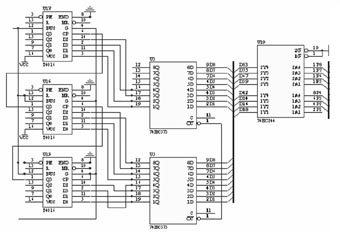

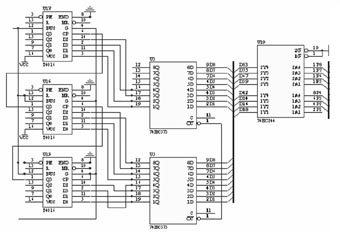

:FPGA芯片区、多路选择与A/D采样电路、时钟电源区、PROM代码下载电路等几部分。结构示意如图1所示。FPGA芯片特点分析及资源分配本系统中的FPGA是采用Altera公司的EP1C20F400。该系

2011-08-23 10:15:34

大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白

2023-03-01 17:10:10

使用。 本文基于快速傅里叶IP核可复用和重配置的特点,实现一种频域的FPGA数字脉压处理器,能够完成正交输入的可变点LFM信号脉冲压缩,具有设计灵活,调试方便,可扩展性强的特点。 1 系统功能硬件

2018-11-09 15:53:22

基于FPGA的数字脉冲压缩技术1.数字脉冲压缩实现原理2.电路设计2.1APEX2OKE系列FPGA 简介2.2 基于FPGA 的算法研究及实现 2.3 脉冲压缩在FPGA 上的实现

2011-03-02 09:41:50

基于FPGA的雷达脉冲压缩系统设计参见附件:

2011-03-02 09:39:11

基于紫光同创FPGA的多路视频采集与AI轻量化加速的实时目标检测系统#2023集创赛#紫光同创#小眼睛科技助力紫光同创高校生态建设@小眼睛科技 获奖作品展示:华南理工大学+CR8_Pro队

2023-11-02 17:51:00

通常输出PWM波形的时候是一直输出的。但是在电机控制中往往只需要输出一定个数的脉冲,不需要一直输出,那么这就需要每次输出PWM时,输出的脉冲个数可控。要实现这个功能,一般有三种方法。 方法一

2021-12-06 07:32:16

高准确度可程控延迟快前沿脉冲信号源系统原理是什么?高准确度可程控延迟快前沿脉冲信号源系统是由什么组成的?如何去设计高准确度可程控延迟快前沿脉冲信号源系统?

2021-04-20 07:31:24

如何实现连续脉冲信号的高分辨率延迟?

2021-04-30 06:07:24

脉冲重新置于FPGA逻辑中,然后将此时钟输入PLL以生成系统时钟。这是一个学校项目,但我不确定这是否会奏效。谁能给我建议这个想法是否有效?如果没有,你能说出理由吗?

2020-08-26 15:09:45

定时器级联-频率 脉冲可控,驱动步进电机

2019-07-16 11:17:00

如何有效解决雷达作用距离与距离分辨率之间的矛盾?基于FPGA的雷达脉冲压缩系统设计

2021-04-08 06:02:27

您好,

我使用FPGA产生一个5MHz的时钟信号,0V-3.3V。为了测试产品的稳定性,需要在这个时钟信号的低电平位置叠加一个脉冲信号,此脉冲信号也是由FPGA产生,频率约为250Mhz。

我

2023-11-27 08:15:24

本帖最后由 一只耳朵怪 于 2018-6-14 08:50 编辑

28035的cap捕获模块,是支持一路脉冲的捕获,还是可以支持多路脉冲的捕获?

2018-06-13 05:37:06

多路ADC系统的硬件设计多路ADC系统的软件设计

2021-04-22 07:06:03

大家好,我目前正在为我的项目寻找评估委员会。我的设计中有一条时间关键路径。该路径需要4个触发器,2个多路复用器和一个用于操作的逻辑门。通过该路径的传播时间(延迟)应小于30ns。这可能与FPGA有关吗?如果是这样,可以推荐哪种评估板和时钟频率?最好的祝福

2019-09-26 10:12:35

谁有全桥可控整流电路的脉冲触发的dsp程序多谢

2014-05-22 16:22:08

高通道密度数据采集系统用于医疗成像、工业过程控制、自动测试设备和40G/100G光通信系统可将众多传感器的信号多路复用至少量ADC,随后依序转换每一通道。 多路复用可让每个系统使用更少的ADC,大幅

2020-12-21 06:11:56

设计制作的等离子体辅助慢波振荡器光控脉冲馈气系统能以任意脉冲宽度给等离子体阴极电子枪馈气,同时以任意时间延迟提供触发信号给调制器,启动空心阴极辉光放电。系统

2009-03-10 20:39:05 16

16 详细阐述一种采用PIC16C55 单片机实现可控数字语音延迟器的设计方案,同时提供控制电路图及软件算法流程图。

2009-04-14 17:40:07 15

15 详细阐述一种采用PIC16C55 单片机实现可控数字语音延迟器的设计方案,同时提供控制电路图及软件算法流程图。

2009-05-14 13:32:14 30

30 提出了一种将高速脉冲信号产生转换为可控直流电平产生、脉冲频率信息产生及脉冲合成输出的设计思想。可控直流电平控制脉冲的高低电平值;脉冲所需的频率信息通过可编程数

2009-05-26 20:57:55 16

16 本文介绍了用单片机实现多路电量脉冲测量的接口设计,说明了接口硬件组成、多路电量脉冲测量算法和软件编程。关键词:单片机;电

2009-09-09 08:57:18 41

41 以太网到多路E1适配电路设计及FPGA实现

摘要:介绍了一种基于现场可编程门阵列(FPGA)的以太网数据-多路E1反向复用器同步电路设计,分析了FPGA具体实现过程中的一些常

2009-11-13 20:59:00 22

22 介绍了在晶闸管监测系统中,多路实时脉冲信号处理的设计方法。采用XC9500XL系列CPLD 进行具体方案的设计,同时给出了相关的Verilog 程序及仿真波形结果。关键词:晶闸管监测

2009-12-18 11:33:26 14

14 本文介绍了一种基于FPGA 的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA 的实现方法。在硬件上FPGA 采用ACEX1K100 器件,用于实现A/D 转换器的控制电路、多路

2009-12-19 16:02:33 50

50 摘要:针对传统设计的快前沿延迟脉冲信号源存在延迟时间调整范围小的主要缺陷,提出了一种基于特殊专用集成电路和计算机控制技术为核心的设计方法,实现了快前沿脉冲延迟

2010-05-30 10:15:30 30

30 高速串并转换器的设计是FPGA 设计的一个重要方面,传统设计方法由于采用FPGA 的内部逻辑资源来实现,从而限制了串并转换的速度。该研究以网络交换调度系统的FGPA 验证平台中多路高

2010-09-22 08:29:41 81

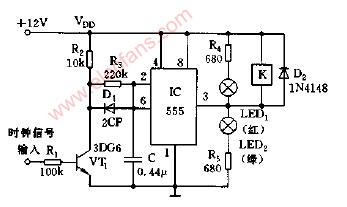

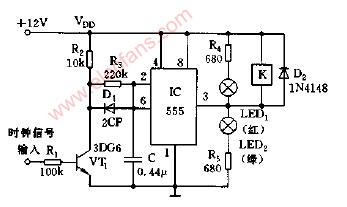

81 可控硅脉冲电路图:D1,D2组成同步电压滤波器,经VT2产生过零正脉冲。555芯片和平共处R4,RP1,C1组成脉冲分频器,只有选择RC充电时间常数大于过零脉冲的周期才产生

2017-06-30 17:12:26 3744

3744

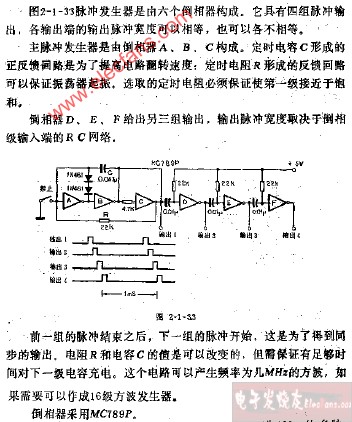

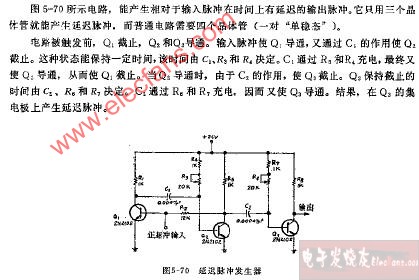

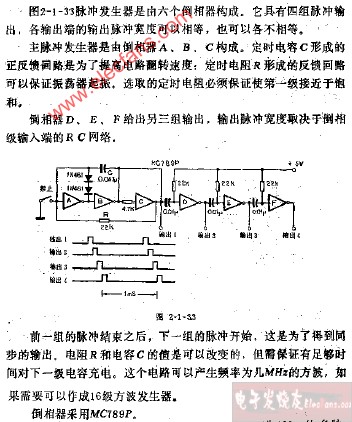

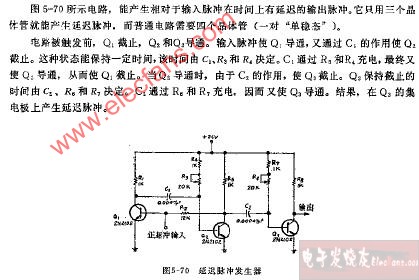

多路时序脉冲发生器

2009-03-23 09:54:16 531

531

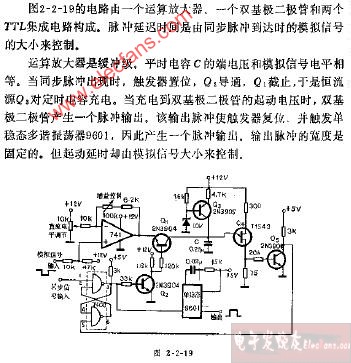

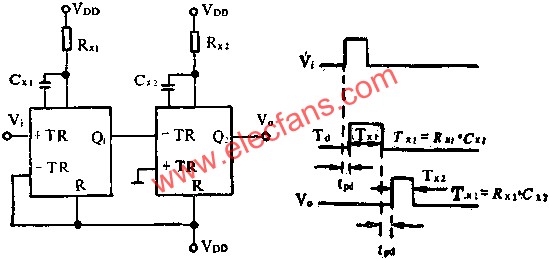

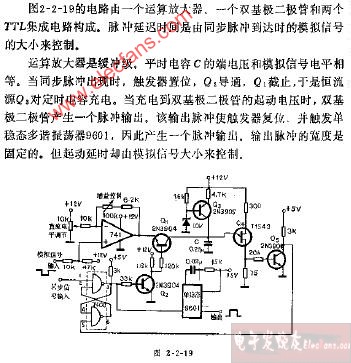

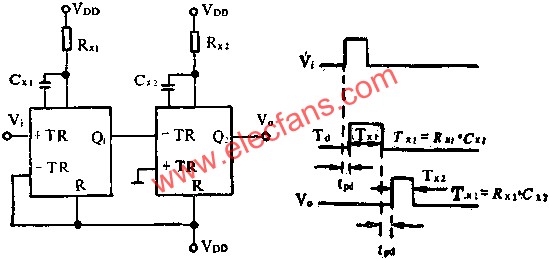

由模拟信号控制脉冲延迟时间

2009-03-29 09:28:55 810

810

摘 要:用VHDL语言设计一个连续脉冲信号延迟线,通过对连续脉冲信号的可控延迟来仿真脉冲多普勒雷达对动目标的跟踪回波包络,分析并建立了直接采样法的系统模型。

2009-05-17 12:38:01 1527

1527

可控硅脉冲消失检测电路图

2009-05-19 13:38:07 378

378

摘要:提出一种基于FPGA技术的多路模拟量、数字量采集与处理系统的设计方案,分析整个系统的结构,并讨论FPGA内部硬件资源的划分和软件的设计方案等。本设计

2009-06-20 15:05:11 1543

1543 摘要: 在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟

2009-06-20 15:34:23 523

523

延迟脉冲发生器电路图

2009-06-26 13:40:02 698

698

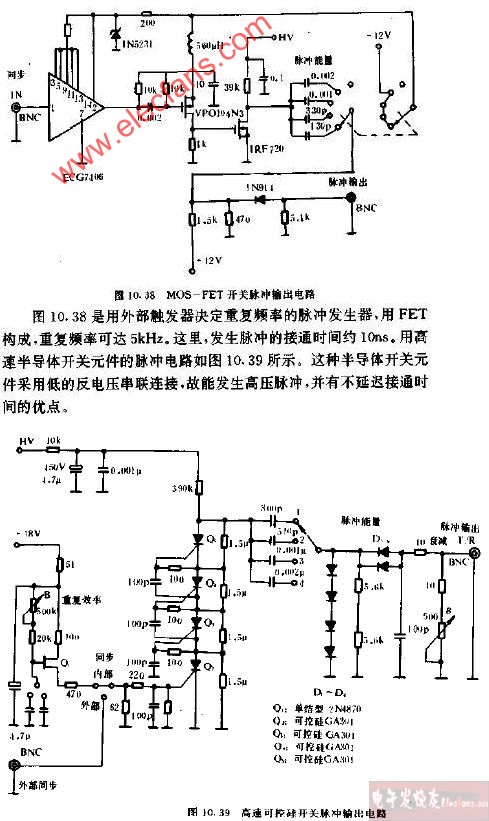

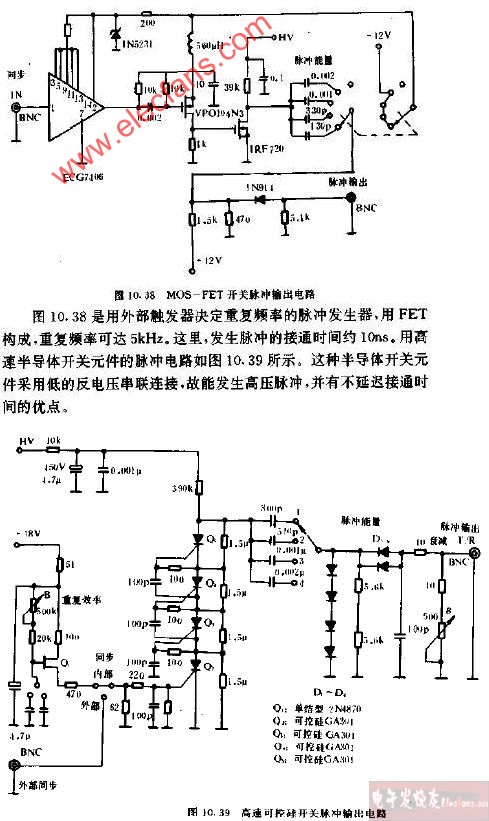

高速可控硅开关脉冲输出电路图

2009-07-06 14:46:11 2226

2226

延时可控高压脉冲发生器的设计

摘要:将数字延时及高压脉冲形成电路结合在一起构成高精度的高压脉冲发

2009-07-15 08:24:23 1862

1862

单片机控制宽脉冲触发可控调压电路?

在交流调压电路中,晶闸管作为可控开关其导通应同时具备两个条件,即承受正向阳极电压的同时给门极施加一正向电压

2009-07-27 11:30:30 2972

2972 J210构成的脉冲延迟电路

2009-08-11 09:00:53 3012

3012

延迟脉冲发生器

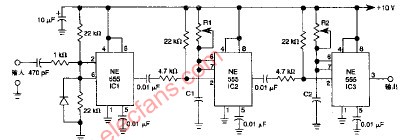

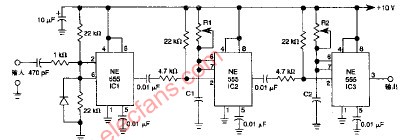

在这个电路中采用的三个555IC

2009-10-05 15:46:59 1278

1278

基于LabVIEW的多路时序控制脉冲发生器设计

0 引 言

在过程控制和自动测量中,经常需要一些时序控制脉冲来触发和关闭不同的控制单元和功能部件的工作。

2009-12-02 11:31:20 3954

3954 基于FPGA雷达成像方位脉冲压缩系统的设计

合成孔径雷达成像算法中较为成熟和应用广泛的算法主要有距离-多普勒(R-D)算法和线性调频变标(CS)算法。R-D算法复杂度相

2009-12-02 11:44:10 1168

1168

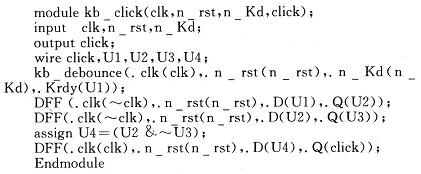

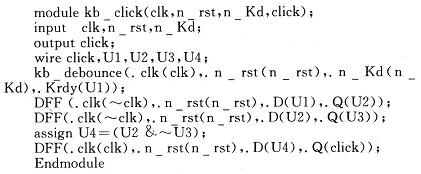

FPGA开发中按键消抖与单脉冲发生器电路

FPGA开发中常用到单脉冲发生器。一些文章介绍过产生单脉冲的电路,产生的单脉冲脉宽和相位都不能与时钟同步,只能用在

2009-12-31 10:36:52 2715

2715

设计原理

随着各种高新前沿技术的迅猛发展,传统设计的固定延迟时间的快前沿脉冲源,已不能满足需要,常常需要在一定范围内可对延迟时间进行任意设置

2010-09-13 09:06:30 2373

2373

图中所示是用J210组成脉冲延迟电路及波形。图示线路是由上升沿触发的线路,如要下降沿触发时,只要将第一

2010-09-24 01:38:52 1228

1228

在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求

2011-03-16 14:39:02 37

37 研究了能够同时对多路 光电编码器 脉冲信号进行细分、计数以及传输的数据采集处理系统。提出了以高度集成的FPGA芯片为核心的设计方式,实现6路光电编码器信号的同步实时处理。坐

2011-08-18 16:33:15 90

90 本课题基于关节臂式坐标测量机的研制需要,研究了 光栅传感器 输出信号的特点和FPGA开发技术,以FPGA为载体,设计了一个基于FPGA的多路光栅数据采集系统。 本文主要介绍了光栅传感

2011-08-18 16:34:55 78

78 用大多数FPGA都可以实现一个数字UWB(超宽带)脉冲发生器。本设计可以创建一个两倍于FPGA时钟频率的脉冲信号(

2011-09-06 11:59:48 5280

5280

多路交换开关是高性能交换部件的核心,本文描述了基于Xilinx公司Virtex-11系列FPGA的特点设计和实现的一种高速多路交换开关,它由输入信道组织、内部无阻塞crossbar交换和仲裁调度器三

2011-12-27 16:45:04 46

46 摘 要:研究一种基于FPGA的多路视频合成系统。系统接收16路ITU656格式的视频数据,按照画面分割的要求对视频数据流进行有效抽取和帧合成处理,经过视频编码芯片转换成模拟信号输出

2012-09-12 17:18:31 99

99 为了能实时监控无人机的状态和提高无人机的安全可靠性,本设计利用FPGA高速率、丰富的片上资源和灵活的设计接口,设计了一套无人机多路监控系统。该监控系统具备了将处于无人机

2013-01-10 16:39:15 126

126 为了实现对多路视频和数据信号的同步传输,提出了一种基于FPGA的视频数据综合传输系统设计方案,并完成系统的软硬件设计。该系统的硬件部分主要由FPGA、CPLD芯片及光模块等设备组成,软件部分采用

2015-12-31 09:26:25 11

11 于FPGA的高速多路数据采集系统的设计。

2016-05-10 13:45:28 41

41 基于FPGA的多路数据实时采集与传输系统_冯希辰

2017-01-08 10:30:29 3

3 基于运放的信号发生器精度低且稳定性和可调节性差,而基于DDS的信号发生器则成本高、电路复杂。为此提出了基于FPGA+PWM的多路信号发生器设计方法。该方法硬件上无需DAC与多路模拟开关,由FPGA产生调制输出波形信号所需的PWM脉冲波,经二阶低通滤波和放大电路后即可得到所需波形信号。

2017-11-18 09:42:01 6332

6332

包括数字上、下变频中的并行DDS和多相滤波,以及延迟模块的实现。完成了基于FPGA及高速A/D、D/A的系统实现,在Xilinx的Vivado开发环境下完成了逻辑设计。实测表明该系统能够正确产生多路延迟后的脉冲信号,具有系统结构简洁、参数设置灵

2017-12-21 16:24:40 1

1 本文开始介绍了什么是脉冲分配器与脉冲分配器特点,其次介绍了脉冲分配器的结构组成与应用领域,最后介绍了用CD4017B制作多路脉冲分配器电路。

2018-01-31 16:54:17 6964

6964 介绍了一种基于FPGA的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA的实现方法,并用v∞L语言设计的状态杌在Qmr啮Ⅱ开发软件中进行仿真。该系统在通用数据采集系统的基础上,增加数

2018-10-12 16:15:09 13

13 结合数据采集系统在航天遥感中的应用“介绍了一种基于FPGA 的多路数据采集系统”给出了硬件原理框图“并对系统进行了分解”而后讨论了影响系统性能的因素实际应用证明“采用该方法设计的系统能有效地完成多路同步高速数据采集任务

2018-10-16 16:18:45 18

18 提出了一种基于FPGA+ARM的多路视频采集系统的设计与实现方法。该视频采集系统不仅能对多路快速变化的视频信号进行采集和处理,而且能应用为系统信号发生设备.系统采用FPGA为核心高速时序逻辑控制

2019-11-19 15:51:42 21

21 目标的信息,就需要有多路视频来对同一个物体在不同方位进行监控。因此需要有一个良好的控制手段,确保多路视频控制稳定,可靠。针对织布机告警系统的需求,提出一种基于FPGA的多路视频通道控制系统,本系统

2020-01-29 17:04:00 553

553

高分辨率的要求;模拟方法采用专用的脉冲延迟器件实现延迟控制,其缺点是抗干扰效果不好,容易产生抖动和电压不稳等问题。于是我们提出构建数模结合的系统,实现连续脉冲信号的高分辨率延迟。

2020-08-11 17:36:46 1060

1060

主要介绍基于FPGA实现多路模拟信号自适应采集系统的设计。该系统主要包括软件和硬件两部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和运放AD824来搭建硬件平台;软件包括FPGA程序

2021-02-02 15:52:34 5

5 针对伺服电机控制系统中的脉冲发送需求问题,提出了一种利用DDS技术,以单片机和CPLD为硬件基础的脉冲输出频率、

2021-04-07 11:18:35 3113

3113

为研究脉冲星X射线辐射脉冲信号的特点需要记录X射线脉冲信号的上升沿时刻与脉冲信号峰值。设计了基于FPGA的X射线脉冲信号数据采集系统。重点介绍了数据采集系统的组成、功能及硬件设计。其中,系统采用11

2021-06-01 09:37:44 13

13 脉冲神经元有监督学习算法通过梯度下降法调整神经元的突触权值,但目标学习序列长度的增加会降低其精度并延长学习周期。为此,提出一种带延迟调整的梯度下降学习算法。将每个突触的延迟作为学习参数,在学习过程中

2021-06-11 16:37:41 12

12 上面的架构是比较通用的架构,官方也有例程可以参考,但是上面架构多了一个VDMA,这就导致视频传输的时候有1到几帧的延迟,这对于低延迟、高分辨率的情形肯定是不能容忍的。

2022-10-08 09:07:59 2813

2813 和set_output_delay命令来设置FPGA范围外的延迟值。两者在含义、约束命令等方面有很多地方是相似的,只不过一个是输入,一个是输出,本文还是分开对两者进行讲述; 输入延迟 set_input_delay命令设定FPGA的输入端口上相对于上游芯片接口时钟边沿的输入路径延迟(不包括FPGA输入端口到第一个触发器数据输

2023-01-01 11:50:07 1747

1747 H.265/HEVC低延迟编码/解码FPGA/ASIC IP, 整体延迟30ms以内,恒速编码不掉帧

2023-02-24 15:01:23 761

761 多片FPGA之间的互连,经常提到多路复用的概念,也经常提到TDM的概念

2023-06-06 10:07:37 221

221

可控硅可设置为延迟定时器电路,用于在设定的预定延迟后打开或关闭负载。

2023-06-19 17:42:59 944

944

德赢Vwin官网

App

德赢Vwin官网

App

评论