调制解调器是一种电子设备,用于实现数字信号与模拟信号之间的转换,从而在计算机之间进行通信。调制解调器通常被简称为“猫”,是计算机中用于实现通信所需的调制和解调功能的设备。

2024-01-12 16:27:09 2855

2855

MSM6882-3是由OKI的低功耗CMOS硅栅技术制造的一种单片MSK(最小移位键控)调制解调器,解调器接收与片上时钟发生器产生的发送定时时钟(ST)同步的待发送数据(SD)。输出由MSK方法调制

2021-04-15 07:26:14

概述:MSM6882-5是由OKI的低功耗CMOS硅栅技术制造的一种单片MSK(最小移位键控)调制解调器,解调器接收与片上时钟发生器产生的发送定时时钟(ST)同步的待发送数据(SD)。

2021-04-13 08:06:06

,输出信号对输入信号的相位有敏感而且放大作用。这就能让我们大概了解了。其实,解调器对于我们并不陌生,我们俗称的猫,即家家户户网线的接入工具,就是解调器的一种。中文称为调制解调器,调制解调器

2014-04-30 17:29:21

组合成一个单元,叫做“调制解调器”。使用什么器件来作调制器和解调器呢?可以想像下在射频世界中任何时候两个信号可以联合起来或分离开,在某些地方需要一个或两个混频器。此外,通常有一个振荡器和合成器,在调相的例子中,有移相器和相位检测器,根据在射频系统中,它们的位置,调制器在发射机之前,解调器在接收机之后。

2017-12-07 14:11:38

单路12V电源ADSL调制解调器线路驱动器,具有低谐波失真性能LT1886,高速双功率放大器,具有出色的高频失真性能

2020-06-01 14:20:31

GSM调制解调器与PSoC 3接口是否有应用说明。首先,我想将GSM调制解调器与PSoC 3接口,并通过发送和接收简单的文本消息与HythMeTime通信。 以上来自于百度翻译 以下为原文

2019-07-22 07:54:45

GSM调制解调器集成传感器节点:简化无线数据采集任务

2021-05-25 06:46:08

概述:DS8500是一款单芯片、可寻址远程传感器通道(HART®)的调制解调器,满足HART协议物理层规范要求。该器件集成了1200Hz/2200Hz FSK信号调制、解调功能,具有极低功耗,由于

2021-05-17 07:32:16

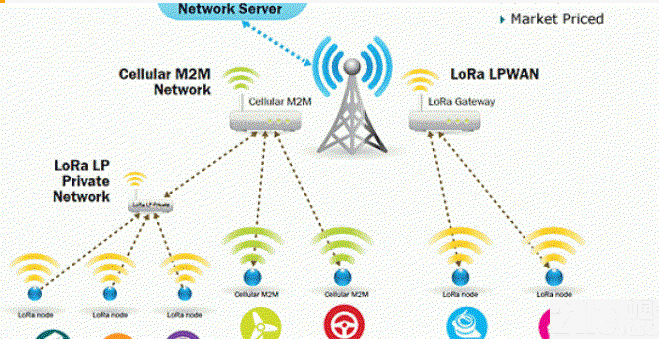

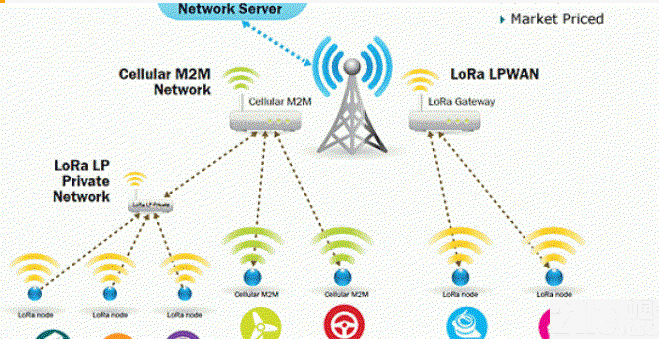

今天继上次跟大家说的SX1276/77/78的概要后,说下有关LoRa™调制解调器相关设计操作。好了,不说废话直接进入主题。LoRa™调制解调器LoRa™调制解调器采用扩频调制和前向纠错技术。与传统

2018-08-03 15:11:37

Qualcomm 212 LTE IoT调制解调器有哪些特性?Qualcomm 212 LTE IoT调制解调器有哪些应用?

2021-06-26 07:55:54

TF232-AF实现RS-232与音频接口隔离转换,单片低速调制解调器包括了完整的频移键控调制器、解调器和滤波器,符合贝尔103标准。可以通过一对电话线实现300波特以下的全双工、半双工数据通信。实现RS-232低速率远距离传输可达20KM。透明传输,无需改动用户协议,工业级设计。

2011-03-03 23:52:20

骁龙855外挂X50 5G 调制解调器是否会引起“功耗过大”的担忧成为了不少明年想抢购5G手机用户的关注点,不过这个问题暂时还需要明年5G手机上市后才能检验。但是,为何曾经内置在SoC中的调制解调器,在5G时代纷纷选择“分居”了呢?

2021-01-06 07:19:03

各位,只是想检查MCUXpresso SDK 中可用的USB主机堆栈是否支持 4G 调制解调器类型的设备。还有 SFTP 协议,因为我在 SDK 的 lwip 堆栈中没有看到任何 SFTP 协议。

2023-04-21 07:10:24

你好,,我做的项目涉及从fpga向任何手机发送消息任何gsm调制解调器...所以需要接口Virtex 2Pro和GSM调制解调器..因为我设计了一个工作在9600波特率的UART ..当我通过

2020-06-13 20:28:50

介绍移动宽带调制解调器的不同设计方案

2021-05-28 06:47:35

FSK调制解调器芯片MC145442和MC145443等,电路比较复杂,灵活性不高,且难以应用于线路干扰强的场合。

2011-03-04 17:24:33

如何去定义调制解调器?Modem分为哪几类?Modem的传输模式有哪几种?Modem的传输数率是由哪几种因素决定的?

2021-05-27 06:22:00

传感器数据。我想要做的是使用 AT 命令更改调制解调器配置以获得最佳连接。我想发送 at_custom_modem_signalling_bg96.c 文件中的“newscanmode”AT 命令,但如何发送该命令?有这样做的功能吗?谢谢

2023-01-04 08:39:53

有时,我的调制解调器挂起,我失去了互联网连接。只有将其关闭并再次打开才能开始连接。

我正在编写一个小程序放入我的 ESP8266 中以检查调制解调器是否挂起,尝试访问某些站点或服务或任何其他可以检查

2023-04-26 07:29:59

本文设计一款抗干扰性强、速率高的无线调制解调器,保证无线测控系统的性能。

2021-05-20 06:27:33

如何选择理想的ADSL调制解调器解决方案?

2021-05-28 06:03:16

本文给出了在一般的HFC网络损耗条件下调制解调器性能的测试结果,根据分析这些结果可以作出一些结论。其中最重要一点是并非所有的调制解调器系统的性能一 样。

2021-05-31 06:12:40

我正在将 X-CUBE-CELLULAR 移植到新的调制解调器和主机 MCU。将命令“AT”发送到调制解调器时,我卡在了 AT 命令通道的初始调制解调器初始化中。调制解调器是 Nimbelink

2022-12-13 08:46:37

嗨,大家好,我正在为嵌入式系统上的调制解调器通信而苦苦挣扎,该系统几乎没有实时执行其他任务。我正在使用内置于调制解调器 (Fibocom G510) 中的 TCP 堆栈。 这似乎并不复杂,但每次我

2022-12-27 08:31:12

描述带隔离功能的 Hart 调制解调器

2022-07-20 07:12:33

怎样去设计一种发射端调制解调器硬件电路?怎样去设计一种接收方调制解调器硬件电路?

2021-05-25 06:54:56

/900调制解调器,但是同样地,使用带有API的RTS来连接。如果有人有任何链接或研究,我可以通过AT命令查看如何使用MQTT,我将非常感激。预先感谢。

2020-04-29 13:31:37

概述:LME2200是一个集成的电力线通信调制解调器芯片,它提供在电力线上发送和接收数据的全方位解决方案。此芯片采用了多载波调制解调技术,此技术专门针对电力线较差的信道条件,因而具有很好的传输性能。此芯片内置了数模转...

2021-04-21 08:01:35

线缆调制解调器(简称CM),Cable是指有线电视网络,Modem是调制解调器。平常用Modem通过电话线上互联网,而线缆调制解调器是在有线电视网络上用来上互联网的设备,它是串接在用户家的有线电视

2019-09-27 09:11:00

学了LabVIEW,做了一个简单的虚拟调制解调器!

2015-04-05 18:21:28

补偿干扰的ADSL调制解调器设计

2020-12-28 07:09:54

大家好,调研了一些调制解调器,看应用里面都没有写5GNR的情况,请问一般IQ调制解调器支持5GNR信号的应用吗?

下图为官网LTC5588-1的应用介绍:

2023-12-01 07:06:27

好的,开始了。我无法让调制解调器睡眠来做任何事情。我几乎在互联网上进行了大量调查,并尝试了我能找到的一切。据我所知,这个功能根本不起作用。很多悲伤。我正在运行来自 git 的最新 Arduino

2023-02-27 06:51:36

通信和电信>xDSL 调制解调器/DSLAM xDSL 调制解调器/DSLAM德州仪器 (TI) 的 xDSL(数字用户线)调制解调器/DSLAM 解决方案方框图 (SBD) 方框图

2012-12-24 11:26:49

基于PLD和嵌入式存储器实现W-CDMA调制解调器的设计

2020-12-28 06:04:37

单片调制解调器MSM7512B

2009-04-30 17:34:09 32

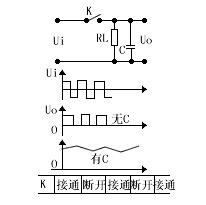

32 调制解调器电路在仪用放大器中的工作和应用:

2009-05-31 10:07:09 13

13

诺基亚 3650系列调制解调器驱动下载

2010-01-18 14:14:35 17

17 夏新 M690 手机调制解调器驱动.rar

2010-01-22 15:34:18 6

6 提出了一种基于FPGA 的数字MSK 调制解调器设计方法,应用VHDL 语言进行了模块设计和时序仿真。硬件部分在Altera 公司 EP2C15AF256C8N FPGA 上实现。结果表明,数字MSK调制解调器具有

2010-01-25 14:29:53 53

53 调制解调器的错误代码

2010-09-07 15:45:06 0

0 研究软件无线电中的通用调制解调器的设计方法。针对软件无线电调制解调器的性能要求,提出以可编程片上系统SoPC(System on a Programmable Chip)技术为核心,以坐标旋转数值

2010-12-30 15:59:07 23

23 调制解调器(MODEM)介绍

一.调制解调器用途:

调制解调器经由公共电信网络实现远程通信的重要设备。主要用来将二进制数字信息转换成可以通过普

2009-08-01 09:55:56 2112

2112 为什么电缆调制解调器的速度会变化不定?

这是电缆调制解调器所具有的一个根本性问题。每个电缆调制解调器都连接到一个回路,这个回路从有线电视公司的交换中心出

2009-08-06 08:06:51 1019

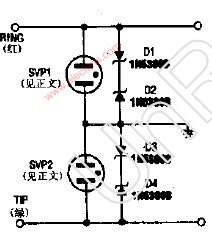

1019 调制解调器保护装置

这个

2009-10-05 14:48:04 403

403

电力线通信调制解调器原理图

2009-11-23 09:46:16 1773

1773 调制解调器(Modem) 调制解调器(Modem)是为数据通信的数字信号在具有有限带宽的模拟信道上进行远距

2009-12-17 15:00:26 855

855 什么是Modem(调制解调器)

Modem(调制解调器)是Modulator

2009-12-28 13:33:37 1448

1448 调制解调器速度 需要传真的

2009-12-29 13:35:45 560

560 传真机的调制解调器速度

2009-12-29 16:37:55 752

752 无线视频的调制解调器 调制解

2010-01-06 14:42:48 1322

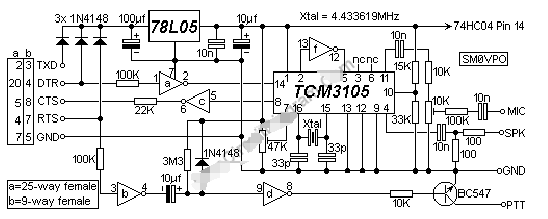

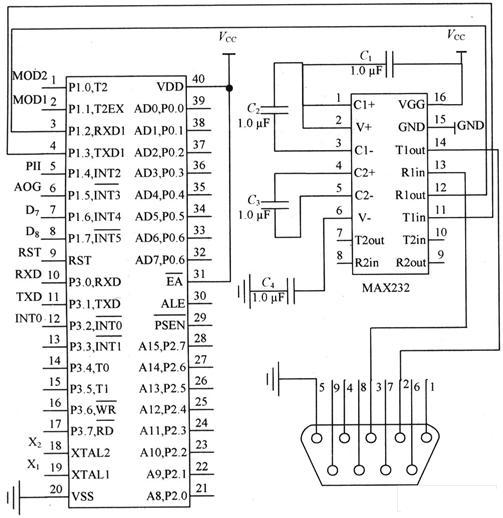

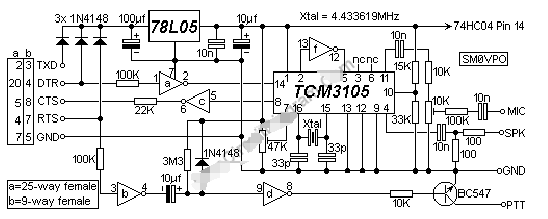

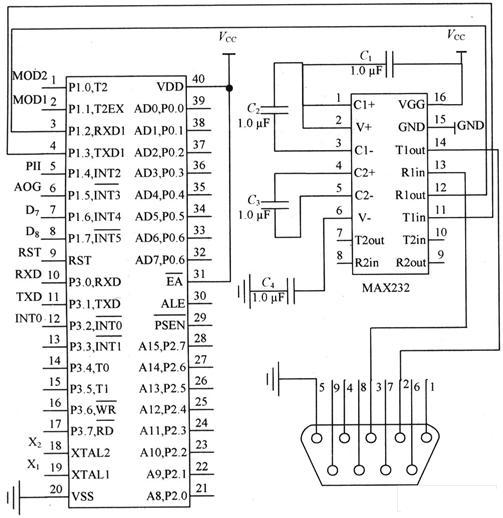

1322 调制解调器与电脑接口电路

调制解调器与PC机接口实际上也就是调制解调器中单片机W77E58与PC机的接口电路,W77E58支持TTL电平,而微机串行

2010-02-16 11:59:08 1355

1355

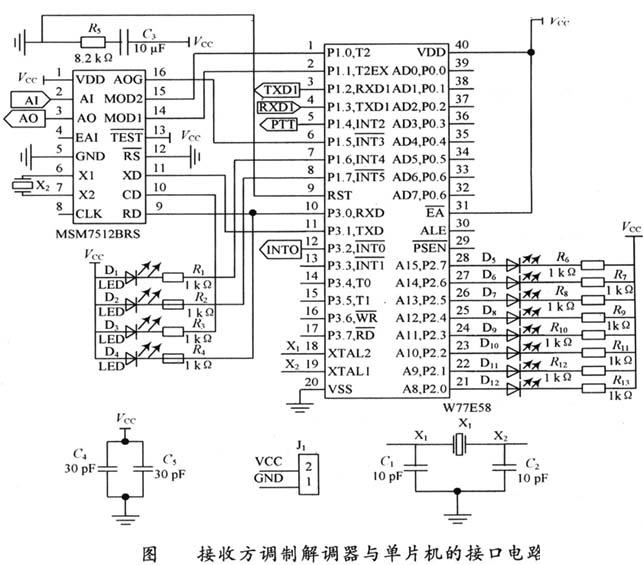

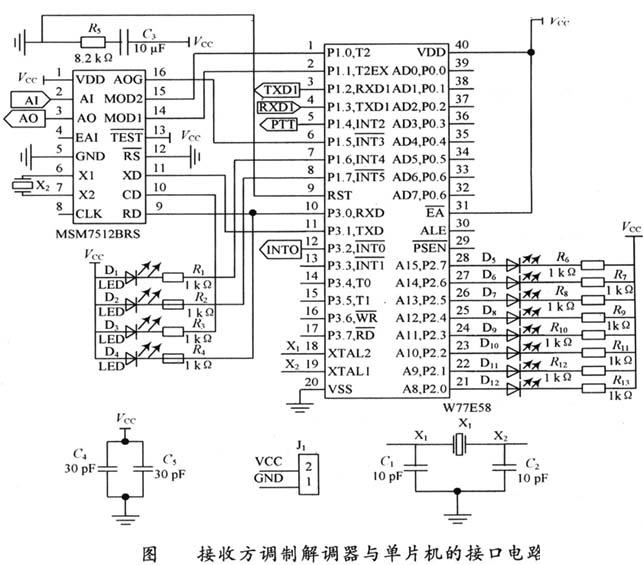

接收方调制解调器与单片机的接口电路

接收方调制解调器电路与战场传感器方调制解调器电路在单片机和调制解调芯片的使用和控制是一样的。所不同的

2010-02-16 13:49:35 1165

1165

调制解调器(Modem),调制解调器(Modem)是什么意思

调制解调器,是一种计算机硬件,它能把计算机的数字信号翻译成

2010-03-19 14:15:13 3209

3209 调制解调器的作用和相关语术手册

调制解调器的作用:Modem (MOdulator-DEModulator),意味着转换信号频率的工具。当你使用调制

2010-03-19 14:19:39 696

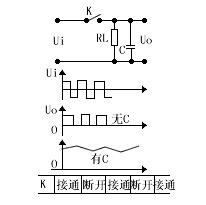

696 调制解调器的原理

解调器是调制式直流放大电路中的一个重要组成部分。它把已放大了的交流电压还原为直流电压,其大小和极性与

2010-09-17 19:36:24 5706

5706

在无线电中,分析调制解调器的转换作用和,认知无线电中自适应调制解调器的FPGA实现。

2011-10-13 16:44:43 45

45 本文设计实现了一种新型的BPSK信号调制解调器,利用m序列的随机性来产生输入基带信号,详细介绍了基于FPGA的BPSK信号调制解调器的设计方法,提供了VHDL源代码在Quartus II环境下的仿真

2012-03-31 15:06:56 67

67 本内容提供了7650诺基亚调制解调器驱动下载

2012-05-22 16:27:59 159

159 解决频段零散化问题 LTE调制解调器支持载波聚合

2017-01-11 12:46:31 12

12 所谓调制,就是把数字信号转换成电话线上传输的模拟信号;解调,即把模拟信号转换成数字信号。合称调制解调器。调制解调器的英文是MODEM,它的作用是模拟信号和数字信号的“翻译员”。电子信号分两种,一种是“模拟信号”,一种是“数字信号”。

2017-10-27 09:43:40 56648

56648

ADSL和调制解调器是两种不同的概念,ADSL是一种技术,而调制解调器是一种设备,调制解调器只是实现了ADSL技术的一种设备,ADSL用的猫是只是调制解调器中的一种而已,像光猫也叫调制解调器等还有很多的设备,调制和解调是一种技术,因此很多实现两种功能的都叫调制解调器。

2018-01-30 11:51:06 9128

9128 苹果将在下一代iPhone上放弃使用高通调制解调器(MODEM)。放弃长期以来处于诉讼关系的高通,取而代之使用因特尔调制解调器。

2018-07-31 08:56:53 3183

3183 本视频主要详细介绍了调制解调器分类,分别有外置式Modem、内置式Modem、PCMCIA插卡式Modem以及机架式Modem。

2018-12-19 16:01:59 6910

6910 苹果总是可以在第一时间用上最新的工艺制程,考虑到2025年,届时5G调制解调器的体积将会更加小巧,并且可以集成在SOC中。所以自研5G调制解调器可以降低iPhone的功耗和厚度,考虑到5G调制解调器研发需要耗费大量资金,所以价格可能不会降低。

2019-05-21 10:09:05 764

764 众所周知5G调制解调器的重要性,而苹果自研的做法是挖走了英特尔5G项目的重要工程师乌玛先卡·斯亚咖依,同时有意收购英特尔德国调制解调器部门,尽管如此,苹果自研的5G调制解调器也不太可能在很多时间推荐市场,最快也要在2022年、2023年左右才会推向市场。

2019-07-08 09:45:04 470

470 我们平时用的手机,外表非常光滑,看起来非常漂亮,但其实它的内部集成了很多电子元器件,其中有一个电子元件,它与手机的信号息息相关,它就是手机调制解调器。那么,什么是手机调制解调器?手机调制解调器又有什么用呢?一起来看看吧。

2020-06-11 17:36:48 15919

15919 电子工业:嵌入式调制解调器

2021-05-17 16:34:04 6

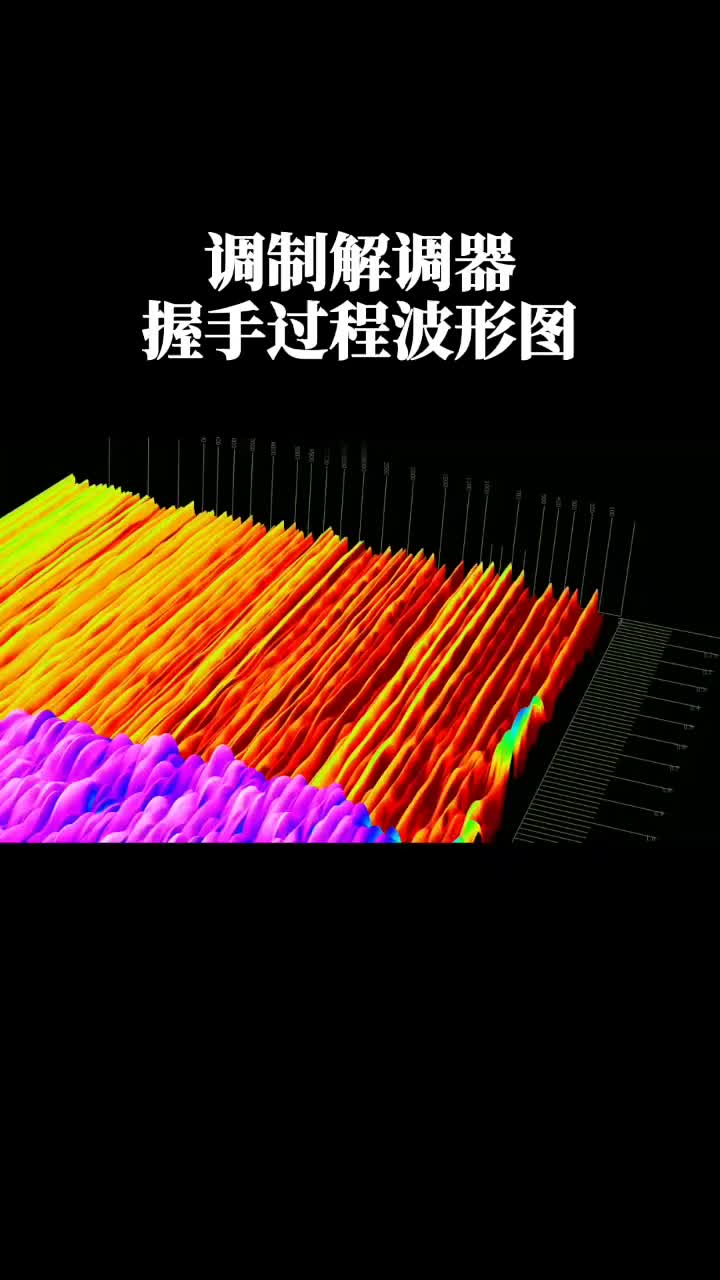

6 继续讲解程序!MSK也能进行相干解调?是的!同样是采用锁相环!先来看看MSK的优点,这是由于下面的这两个主要优势才得以被应用! 看看功率谱! 注意观察带外的衰减比较情况! Tb是符号率! 尽管MSK

2021-09-18 11:43:11 3316

3316

调制解调器和路由器之间的区别在于调制解调器连接到互联网,而路由器将设备连接到 Wi-Fi。我们对两者进行了审查,以消除对其工作方式的困惑,并帮助您选择满足互联网需求的设备。

2021-11-24 14:38:24 10044

10044 德赢Vwin官网

网站提供《带隔离功能的Hart调制解调器.zip》资料免费下载

2022-07-18 10:53:03 10

10 PLC 调制解调器的电源同步

2022-11-14 21:08:11 0

0 本方案是使任何调制解调器(无论是阿尔卡特还是华为)可以通过 USB 连接到 Raspberry pi 的解决方案。避免许多问题和一些操作系统麻烦。将 4G/3g USB 调制解调器安装

2022-12-22 11:24:19 0

0 R9A06G037 调制解调器 LSI 数据表

2023-02-03 19:15:10 0

0 调制解调器的英文单词为Modem,它来自英文术语MODulator/DEModulator(调制器/解调器),它是一种翻译器。它将计算机输出的原始数字信号变换成适应模拟信道的信号,我们把这个实现调制

2023-05-25 14:52:57 2093

2093 调制解调器,是调制器和解调器的缩写 ,一种计算机硬件 [1] ,它能把计算机的数字信号翻译成可沿普通电话线传送的模拟信号,而这些模拟信号又可被线路另一端的另一个调制解调器接收,并译成计算机可懂的语言。这一简单过程完成了两台计算机间的通信。

2023-05-25 17:19:36 1388

1388 调制解调器是“调制器解调器”的缩写,意思是调制传输以接收和传送数据。它是一扇通向互联网的门,通过电缆/电话线和你家里的所有设备接收和发送数据。把它想成是使一切成为可能的翻译,把互联网从庞大的基础设施高速公路翻译成家庭和办公室内的小通道。

调制解调器是你连接万维网的入口。

2023-05-25 17:32:31 3183

3183 R9A06G037 调制解调器 LSI 数据表

2023-07-04 19:46:49 0

0 德赢Vwin官网

网站提供《基于VHDL的MSK调制解调器的建模与设计.pdf》资料免费下载

2023-10-18 10:46:44 0

0 调制解调器和路由器的详细对比 调制解调器(Modem)和路由器(Router)是现代互联网连接中不可或缺的设备。它们在网络通信的不同阶段发挥着不同的作用。本文将详细对比调制解调器和路由器的功能

2023-11-27 15:40:14 539

539 调制解调器需要相应的驱动程序来正常工作。可能是驱动程序出现问题导致调制解调器无法正常工作。可以尝试重新安装或更新调制解调器的驱动程序。可以通过设备管理器或调制解调器制造商的官方网站获取最新的驱动程序,并按照说明进行安装。

2024-01-17 15:30:00 1212

1212 LoRa调制解调器采用专利扩频调制和前向纠错技术,它融合了数字扩频、数字信号处理和前向纠错编码技术。

2024-03-15 18:08:57 688

688

德赢Vwin官网

App

德赢Vwin官网

App

评论