最近在做频率计,求大神指教!!有程序最好!!

2014-11-25 20:28:15

of the MC8051 IP core. March 2010: Oregano Systems - Design & Consulting GesmbH

2018-07-03 07:03:23

美国 进口 Agilent 53220A 频率计产品名称:通用频率计数器/计时器产品品牌:Agilent安捷伦/keysight是德 如若平台没有留有本公司咨询方式,请在浏览器搜索东莞市塘厦佳华

2020-04-20 15:58:26

要求(1)当按下开始键时,能够对0~250kHz的信号频率进行准确计数,计数误差不超过Hz;(2)要求所设计的频率计能够测量各种波形,如正弦波、方波、三角波等(在设计时需对被测信号进行放大和整形处理)。本课题用proteus和Keil 实现。

2018-01-08 15:28:32

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

FPGA上对OC8051IP核的修改与测试FPGA上对OC8051IP核的修改与测试单片机与嵌入式系统 解放军信息工程大学 杨先文 李峥引 言20世纪80年代初,Intel公司推出了MCS-51

2012-08-11 11:41:47

FPGA嵌入8051单片机 IP核编程,编写的c语言矩阵键盘程序可以在stc89c54单片机上正常工作,但是下载到FPGA中8051单片机ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

本教程的过程中,请读者注意以下几点: 本教程在编写时充分借鉴了周立功编写的mc8051 IP核教程,同时针对其中较为落后的一些内容进行了更新(周立功的教程使用的是Cyclone系列的器件,软件版本也很低

2019-05-24 04:35:33

本帖最后由 eehome 于 2013-1-5 10:04 编辑

这个资料主要是介绍用verilog语言写频率计的,介绍了频率计基本原理

2012-11-29 18:20:43

基于Proteus的频率计板图

2015-04-14 11:51:09

有木有基于8086的频率计,谁懂,能不能帮我修改下代码和电路啊?

2016-06-26 13:18:04

`请问频率计为什么要分频?`

2019-08-23 16:41:15

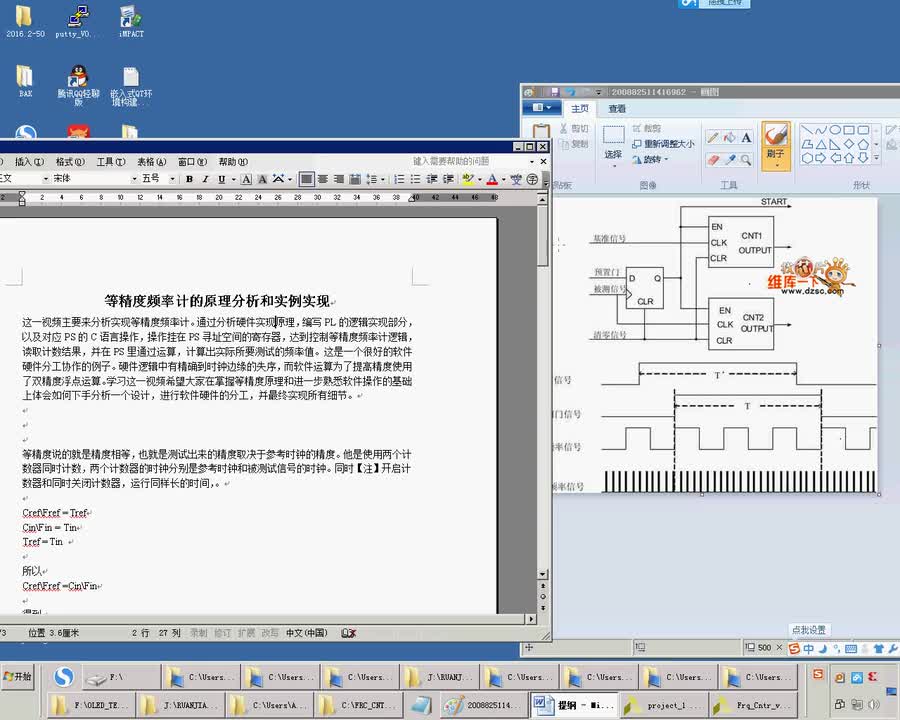

频率计是测量频率或时间间隔信息的仪器,精度高,价格低,设计独特。只利用计数器即可实现高精度的测量,可见当初发明者的聪明和智慧。图1频率计结构框图从图1的频率计结构框图中可以看出,频率计包括几个部分:1)信号调理部分2)事件门和时间门3)事件计数器和时间计数器4)处理器和显示器5)时基电路

2019-07-01 07:33:31

请问各位大神,我在做毕设,关于基于fpga的高频频率计的设计,请问幅值怎么确定啊?

2017-04-16 17:30:25

请教高手……频率计的测量范围如何调整(或者原理)?网上的资料大部分都是测到K而且大部分没有说明能够测量最大值得原因,本人做的频率计测量范围0-200MHZ,分频用的74HC4017十进制计数器,但是对于它的分频原理还是云里雾里……求赐教【单片机用的AT89C51,数据选择器用的74151】

2014-05-01 10:58:57

基于AT89C51的频率计的设计

2012-11-09 11:32:10

LCD显示频率计

2017-06-15 00:05:03

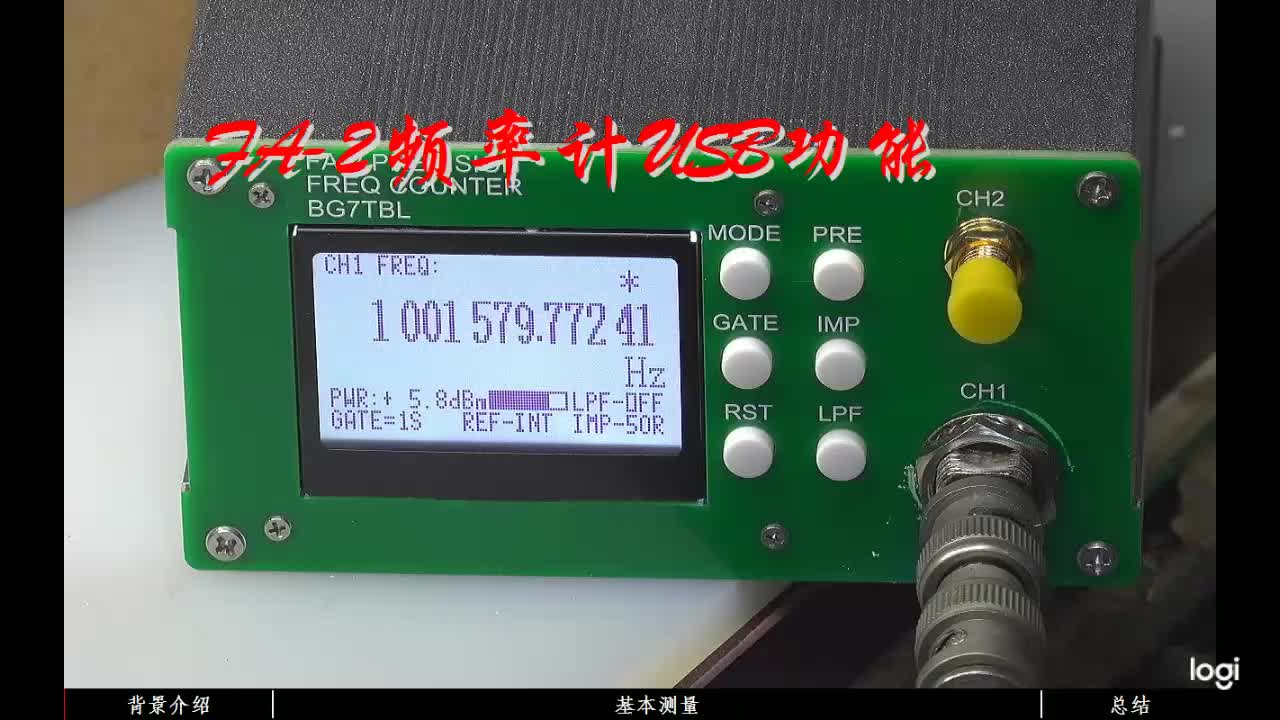

`该频率计以PIC16F877A为核心,采用LCD1602为显示器件,采用PIC单片机的CCP捕获功能记一定脉冲数所需要的时间来计算频率。能测出20到20KHz频率范围内的频率,后期将加入FPGA

2015-11-13 19:14:32

网上能找到的资料都是用altera的FPGA做的,有人用过xilinx FPGA搭建8051核吗?请与我联系

2017-06-03 14:59:23

请问大神们有没有会用labview做频率计的,就是基于labVIEW的频率计设计,大概是这样的

2017-04-07 22:00:48

本帖最后由 今世小浪子 于 2017-8-14 13:16 编辑

基于FPGA频率计设计--拟定设计方案一、设计设备: Xilinx的SEED-XUPVZPro芯片配套实验箱,quartus

2012-07-23 00:03:25

本帖最后由 Harvestlamb 于 2017-7-24 17:44 编辑

项目名称:基于fpga的数字频率计试用计划:基于fpga的数字频率计,能达到2015年全国大学生电子设计大赛频率测量测技术指标(100M),并且达到精准测频,误差符合题目要求。

2017-06-19 15:32:34

本视频是Runber FPGA开发板的配套视频课程,本实验设计频率计,用于测量频率,测量范围1-9999。将系统时钟信号分频,得到一个低频信号,该信号可以通过按键KEY0设定16种不同的频率值,并用

2021-04-13 14:32:09

十、MC8051软核在FPGA上的使用本教程内容力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及相关设计软件的使用,并激起读者对 SOPC 技术的兴趣。本实验

2017-02-17 19:54:23

源文件。 2.3.2 建立MC8051应用工程, 这一小节将讲述如何使用以上移植的mc8051的核建立一个实际的Quartus II 工程并能够在芯航线FPGA学习套件的主板上运行。 具体步骤如下

2017-02-17 22:17:50

本教程的过程中,请读者注意以下几点: 本教程在编写时充分借鉴了周立功编写的mc8051 IP核教程,同时针对其中较为落后的一些内容进行了更新(周立功的教程使用的是Cyclone系列的器件,软件版本也很低

2016-03-11 17:59:02

分享一个频率计设计

2019-01-30 20:24:28

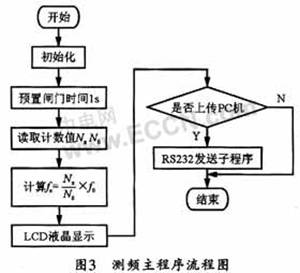

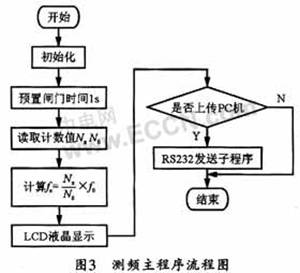

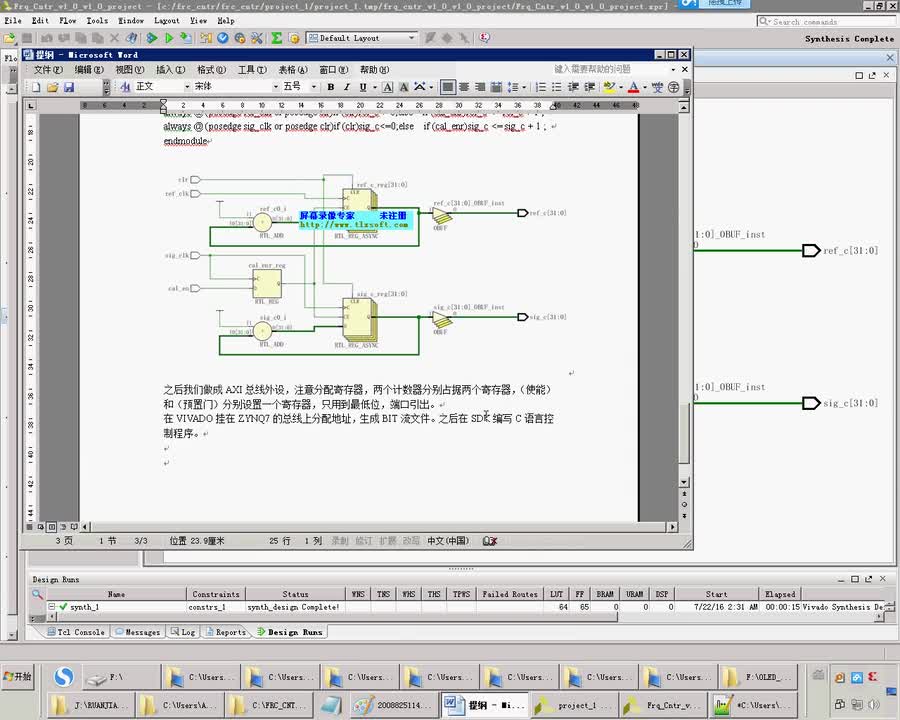

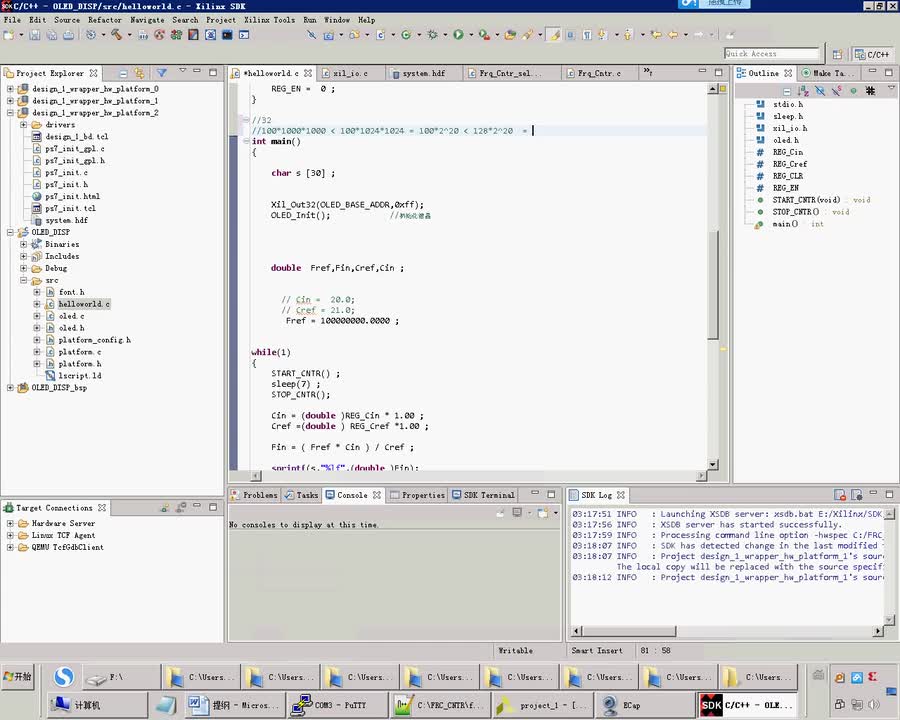

单片机控制的高精度智能频率计的FPGA 实现

2012-08-20 16:08:22

导致测量的时间过长。2.占空比测量:这里借鉴了基于FPGA的简易频率计设计这篇文章的测量方法。通过门控时间内,对PLL倍频的200MHz时钟clk_200计数,读出待测信号连续的四个边沿的计数值,通过

2022-02-09 07:07:00

基于FPGA的IP核8051上实现TCPIP的设计

2012-08-06 12:18:28

受到业内人士的青睐。本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2019-07-04 06:02:19

最近学了一段时间的FPGA,求助大神,可以给我发一些关于基于FPGA的数字频率计的资料,做个小东西练练手1287368714@qq.com

2017-07-26 23:53:53

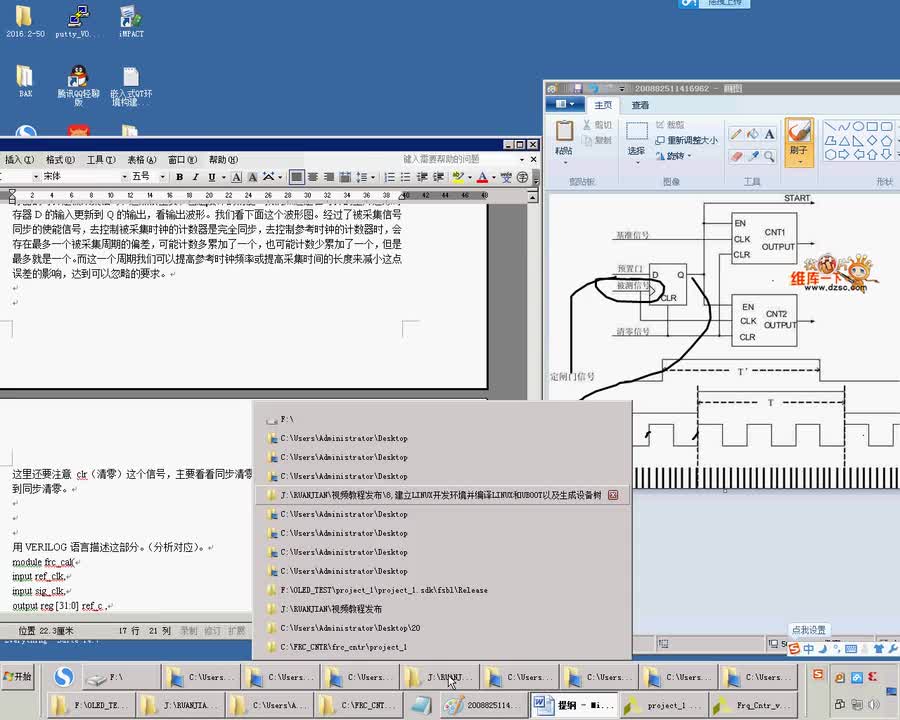

基于FPGA的等精度频率计的设计与实现摘 要:利用等精度测量原理,通过FPGA运用VHDL编程设计一个数字式频率计,精度范围在DC~100

2008-08-19 09:46:02

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

做的一个基于xilinx fpga的一个数字频率计,用单片机显示

2015-09-30 11:38:23

有哪个大神会基于VHDL数字频率计的设计与仿真吗求求求

2020-03-30 23:14:40

1、声级频率计权声级频率计权的基本定义是指其恒幅稳态正弦输入信号级与显示装置上指示信号级两者之间作为频率函数关系而规定的差值,频率计权用分贝(dB)表示。声级计的频率计权通常有A、B、C、D计权

2021-09-16 08:39:03

本人学生一枚,现在需要一个频率计,基础功能加上测试范围三档调节,并且具备超限报警功能的,需要在FPGA开发板上调试。。希望高手能帮助一下。。。

2013-12-11 18:21:23

刚刚学习FPGA我使用Verilog写的,对它还不算是太懂,然后就一个做频率计的任务,由于不是太懂所以就不理解频率计分频之后的闸门信号不是太懂,当然也就谈不上自己的理解了,所以在这想问问各位大神频率计用Verilog如何写?

2014-11-19 19:44:40

关于a计权声级的对采样声音信号的频率计权要怎么编程有没有懂的求教图片是编程的原理

2015-05-20 23:26:43

影响频率计频率的因素有哪些

2015-11-07 21:57:16

本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2021-05-08 06:22:32

怎么实现基于STM32频率计的设计?

2021-11-16 06:20:17

怎么实现基于STM32频率计的设计?

2021-12-02 07:40:49

怎么实现基于单片机的频率计的设计?

2021-11-02 07:54:14

老师要求弄一个频率计,不懂呀,求教

2014-06-16 15:08:01

怎么才能在嵌入FPGA的IP核8051上实现TCP/IP的设计?

2021-04-29 06:51:27

在测试测量中测试精度一直是最为关心的问题。频率计作为高精度的频率和时间测试仪表,测试精度高于普通的频谱仪和示波器,所以测试精度的计算就更加为人关注。影响测试精度,或者说产生误差的因素很多,而其

2019-08-07 08:06:58

的其它设计部分尽量不相关。为了满足上述的要求, 在FPGA中嵌入一个比较理想的选择, 而这个即通用又控制简单的IP核最好选择8051微处理器。

2019-08-26 06:27:15

今天考试,求一个labview的虚拟频率计设计

2015-12-08 10:32:45

求助基于FPGA的数字频率计怎么做

2015-08-13 09:11:07

在做高频电容三点式振荡电路时,示波器和频率计测量频率有什么不同

2011-10-18 20:28:12

新手一枚,编写的等精度频率计

2016-01-28 16:07:49

大家好,跟大家分享一下基于单片机的LED显示的频率计设计。

2013-02-17 10:02:53

简易频率计,测量范围0---999Hz

2016-12-25 00:47:52

谁有基于FPGA的LCD屏显示的频率计代码啊, 万分感谢啊

2017-07-31 10:43:16

8051单片机内核VHDL源代码

This is version 1.1. of the MC8051 IP core.

Jan 31st 2002 - Oregano Systems - Design & Consulting GesmbH

2007-11-12 23:00:18 64

64 8051参考设计,与其他8051的免费IP相比,文档相对较全,Oregano System 提供

This is version 1.3 of the MC8051 IP core.

2008-05-20 11:34:20 84

84 介绍了一种运用FPGA开发软件Quartus II设计的数字频率计。该数字频率计的1 Hz~1 MHz输入被测脉冲信号具有频率测量、周期测量、脉宽测量和占空比测量等多种用途,其测试结果由3 只

2009-03-17 10:31:31 184

184 This is version 1.3 of the MC8051 IP core.

September 2002: Oregano Systems - Design &

2009-05-14 11:29:02 25

25 介绍了基于IP 的可重用的SOC 设计方法;选用MC8051 IP 核为核心控制器,自主开发了UART IP 核、I2C IP 核、USB IP 核,采用Wishbone 片上总线架构,集成了一个MCU 系统;同时设计了针对此MCU

2009-11-30 15:06:20 33

33 提出了一种星载IEEE 1394智能终端的设计方案,介绍了基于MC8051软核与Actel APA系列FPGA开发IEEE 1394总线接口的设计过程与要点,实现了灵活、小型化、易于扩展的1394总线接口。

2010-08-06 14:33:39 20

20 C8051F041的高精度频率计设计

0 概述频率测量是电子测量中最基本的测量之一。随着电子科学技术的发展,对信号频率测量的精度要求越来越高。目前采用的测

2010-04-01 14:13:02 1233

1233

MC8051是与MCS一5l系列微处理器指令集完全兼容的8位嵌入式微处理器,通过芯核重用技术,可广泛应用在一些面积要求比较苛刻,而对速度要求不是很高的片上系统中。 1 MC8051功能特点

2012-05-22 11:16:23 6950

6950

MC8051 硬件模块 单片机 作为一个大型设计,其内核由定时器时钟管理单元、ALU算数逻辑单元、串口及控制单元、存储单元RAM及ROM等模块组成。 1 时钟管理单元 MC8051内核采用完全同步的时

2012-05-22 11:40:12 2035

2035

基于Altera公司FPGA芯片EP2C8Q208,嵌入MC8051 IP Core,用C语言对MC8051 IP Core进行编程,以其作为控制核心,实现系统控制。在FPGA芯片中,利用Verilog HDL语言进行编程,设计了以MC8051 IP Core为核

2012-11-09 17:30:53 213

213 本教程内容力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及相关设计软件的使用,并激起读者对 SOPC 技术的兴趣。本实验重点讲 8051Core 的应用,并通过一个简

2012-11-13 14:30:21 126

126 文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法

2013-01-07 11:17:31 4566

4566

FPGA MC8051移植 100M频率计设计详细步骤

2015-11-05 16:17:15 21

21 MC8051_IP核简单指令的仿真步骤。

2016-05-06 11:47:41 0

0 基于8051的Proteus仿真-数码管显示的频率计

2016-09-01 23:36:35 28

28 基于8051的Proteus仿真-字符液晶显示的频率计

2016-09-01 23:37:29 117

117 用户交互界面设计的控制核心。采用正弦查找表IP核+D/A的方式实现DDS技术并产生系统扫频信号,以异步FIFO作为FPGA与MC8051内核之间数据传输的缓存模块,同时采用TFT彩屏液晶进行显示界面设计。 在现代电力电子系统中,随着内场测试和外场维护工作量的增加,对目前通用的测

2018-01-19 20:36:01 308

308 本设计采用FPGA技术,在FPGA中实现8051单片机的软核,将外部SPI Flash中的代码数据加载到FPGA内部ram,然后复位 MC8051,实现外部flash启动MC8051。

2019-06-11 17:47:00 3

3 本文档的主要内容详细介绍的是FPGA频率计与串口通信的设计资料说明。

2021-03-07 08:00:00 5

5 MC8051 IP指令使用资源表说明。

2021-03-28 10:39:31 8

8

德赢Vwin官网

App

德赢Vwin官网

App

评论