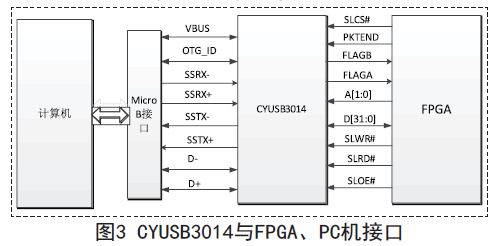

本文介绍了以FPGA为控制核心,以cypress的FX3系列CYUSB3014芯片为总线接口芯片,实现了对USB3.0总线技术的开发应用,实际测试的传输速度能够达到1.43Gbps.##FPGA

2014-02-27 09:48:58 5036

5036 本文设计了一种高速实时数据采集系统。该系统首先对传感器输出信号进行放大滤波处理,然后将其转换为数字信号。经FIFO缓存后,使用USB的猝发传输模式传输到计算机,文中给出了硬件电路,并简要介绍了CYUSB3014芯片的特点和固件程序。##系统硬件设计与上位机软件设计。

2014-03-26 12:05:49 9492

9492 CYUSB3014 - EZ-USB FX3 SuperSpeed USB Controller UART support up to 4 Mbps - Cypress Semiconductor

2022-11-04 17:22:44

做过一个类似的板子,RX/TX没有过孔,线宽25mil线距6mil,可是识别到3.0但速度只有240M

(3)这次我们想再改改试试,于是又做了一次,结果不行了。。。,CYUSB3014芯片是上次用

2024-02-28 06:33:17

CYUSB3014的USB 3.0和2.0 的这几组信号是否有在芯片内部上拉,因为根据规范,3014作为device应该有1个上拉电平,但是在参考设计上没有做上拉?

2、如果要测试USB3.0信号眼图,是否有对应的设备来使得USB接口发指定pattern的信号?

2024-02-29 07:30:43

使用的芯片的CYUSB3014,在最近的使用中,初次上电开机(有固件在ROM启动),在电脑的设备管理器 和 Cypress Controlcenter中均找不到USB设备,然后对芯片进行复位,复位后

2024-02-27 08:04:47

你好,

CYUSB3014 USB 端口的 TX (SSTXP/N) 和 RX (SSRXP/N) 的 Vcm(共模电压)分别是多少?

问候。

2024-02-23 07:48:26

当前PMODE[2:0]设置为Z11,即USB启动。连接PC后安装驱动,设备显示如下:

实验室有编写好的固件(这个固件在别的设备的CYUSB3014上能正常使用),使用Control Center

2024-02-27 08:26:21

我们这边在开发一个带USB3.0接口的CAN通讯监控工具的时候,USB出现了一个问题。在USB3.0接口上通过control center工具给flash下载程序的时候,会提示SPI flash下载

2024-02-28 07:04:55

FPGA在传输数据给CYUSB3014时单次采集数据正常,但在多次传输数据时出现USB接口重复启动情况;

传输模式采用连续传输,异常是发生在数据写入CYUSB3014芯片fifo时,FLAGB

2024-02-28 07:09:37

CYUSB3014型USB3.0+FPGA电路设计详解小梅哥2016年12月29日星期四芯航线AC6102开发板上,使用了一片Cypress的USB3.0全协议芯片CYUSB3014作为FPGA

2019-01-29 06:35:19

不需要那么多数据(比如1024个字节)。

我请教了从事USB3.0开发的朋友,他告诉我,需要使用CUYUSB3014的I2C/SPI/UART接口发送自定义的指令给FPGA,但是我觉得,我已经具备高速

2024-02-27 07:26:54

CYUSB3014工作在2.0模式下会对视频进行压缩,请问文档中的这句话是指用3014对视频进行压缩么,还是只用主处理器进行,多谢!

2024-02-29 08:01:20

公司想用CYUSB3014 做USB3.0/2.0 enumeration 测试治具。因为在网上也看到一些相关的方案,但是有些不明白的地方想咨询下:

1.从datasheet上面看

2024-02-27 06:17:07

首先,我想知道CYUSB3014是否可以输出时钟作为FX2LP外部传感器…第二,当我使用GPIF与外部传感器通信时,是否需要与外部设备时钟同步?谢谢!! 以上来自于百度翻译 以下为原文first

2018-12-11 14:55:24

当hs-otg CYUSB3014芯片的特点作为主持人,我怎么能建立FX3装置?有没有关于CYUSB3014芯片的特点作为fx3apiguide主机hs-otg .pdf。我想了解hs-otg主机

2019-04-19 14:37:18

我在官方的开发板原理图中发现,CYUSB3014的SSRXP管脚接到了USB连接器的STDB_SSRX-管脚上,为什么要把rx±反接呢?

2024-02-28 07:58:35

CYUSB3014固件使用的官方的例程slfifoasync,我使用FPGA向USB发送数据,然后在PC端读取,但是因为需要得到最新上传的数据,因此需要先读空FIFO里的数据,但读空之后的下一次读取

2024-02-27 06:55:04

1、本工程采用USB3.0芯片CYUSB3014,通过同步从设备FIFO接口与FPGA进行通信;

2、USB固件程序在AN65974文档提供的基础上进行更改设计,更改内容如下:

数据带宽由32位

2024-02-29 06:22:19

你好,我正在为 Cyusb3014 开发固件。 我想将固件中的数据保存到 Cyusb 附带的 EEPROM 中,然后将其插入主机,通过上层计算机从 EEPROM 读取数据。 我该怎么办? 谢谢

2024-02-27 06:18:32

USB3.0 和 USB2.0 总线的主要区别,见下图(点击图片,可放大些):BTW,我个人近期想使用CYUSB3014 这个芯片来设计一款USB3.0 的精简、Mini型开发板。有感兴趣的朋友吗? 大家一起可以来DIY,一起众筹制作!这样成本低很多!QQ群(USB技术交流群):818914013

2019-05-08 18:36:14

项目中使用Cypress的CYUSB3014实现FPGA与PC的通信,目前需要做备选方案,有没有推荐的可以实现该功能的其他USB控制芯片?谢谢各位!

2018-12-18 10:03:52

支持QQ群: 91335135 - Cypress USB3.0技术中心(仅限已购买客户加入)USB3.0开发板至尊版主要特性: ●FPGA芯片:EP3C40F484C8N(资源更丰富,功能更强

2019-01-22 14:19:35

支持QQ群: 91335135 - Cypress USB3.0技术中心(仅限已购买客户加入)USB3.0开发板至尊版主要特性: ●FPGA芯片:EP3C40F484C8N(资源更丰富,功能更强

2018-10-15 10:32:03

支持QQ群: 91335135 - Cypress USB3.0技术中心(仅限已购买客户加入)USB3.0开发板至尊版主要特性: ●FPGA芯片:EP3C40F484C8N(资源更丰富,功能更强

2019-01-09 14:26:03

CYUSB3014之间数据传输采用双通道设计,高速的数据传输通道和低速的控制指令传输通道是独立的。●丰富的软件功能支持,让您可以更快更高效的进行学习开发。USB3.0开发板至尊版清单1、 u

2019-01-15 10:47:00

支持QQ群: 91335135 - Cypress USB3.0技术中心(仅限已购买客户加入)USB3.0开发板至尊版主要特性: ●FPGA芯片:EP3C40F484C8N(资源更丰富,功能更强

2018-09-20 15:10:04

支持QQ群: 91335135 - Cypress USB3.0技术中心(仅限已购买客户加入)USB3.0开发板至尊版主要特性: ●FPGA芯片:EP3C40F484C8N(资源更丰富,功能更强

2018-10-22 13:26:33

精心设计的一款FPGA+USB3.0开发板,主芯片架构为:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2选1)+MT47H64M16HR

2018-10-18 14:46:05

精心设计的一款FPGA+USB3.0开发板,主芯片架构为:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2选1)+MT47H64M16HR

2019-01-22 14:40:01

精心设计的一款FPGA+USB3.0开发板,主芯片架构为:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2选1)+MT47H64M16HR

2018-11-21 11:25:31

2.5V或3.3V可配置 IO(支持LVDS传输)●U***3.0芯片IO均已引到FPGA,使用更方便;USB3.0开发板主要软件资源●完整的固件下载方案,通过应用程序下载固件程序到CYUSB3014中

2019-01-15 10:50:33

精心设计的一款FPGA+USB3.0开发板,主芯片架构为:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2选1)+MT47H64M16HR

2019-01-08 14:30:50

精心设计的一款FPGA+USB3.0开发板,主芯片架构为:CYUSB3014(FX3系列USB3.0芯片)+EP3C40F484/EP3C16F484(FPGA芯片,2选1)+MT47H64M16HR

2018-09-20 15:22:52

://www.huanor.com)精心设计的一款USB3.0 + FPGA传输架构的模块,主芯片架构为:CYUSB3014(CYPRESS公司FX3系列USB3.0芯片)+ XC6SLX45(XILINX公司Spartan 6

2019-01-15 10:40:28

://www.huanor.com)精心设计的一款USB3.0 + FPGA传输架构的模块,主芯片架构为:CYUSB3014(CYPRESS公司FX3系列USB3.0芯片)+ XC6SLX45(XILINX公司Spartan 6

2018-09-20 15:08:33

://www.huanor.com)精心设计的一款USB3.0 + FPGA传输架构的模块,主芯片架构为:CYUSB3014(CYPRESS公司FX3系列USB3.0芯片)+ XC6SLX45(XILINX公司Spartan 6

2019-01-08 14:28:08

CYUSB3014通过SPI和FPGA通信时,通过SPI向FPGA写数据,在一个片选时钟周期内,片选会被打断,然后又恢复正常,数据接着被打断前传输,但一帧的结束时间还提前了,这样一帧的数据就丢了

2024-02-28 06:43:54

我参考cysub3kit-003设计了一块cyusb3014板子,焊接完成后测试了19.2MHZ时钟和电源,都正常,我附上了XTALIN、XTALOUT、V1P2(1.2V±16mv)、V3P3

2024-02-27 08:22:39

自己做了个板子。测试时发现cyusb3014只能被识别为USB2.1设备。USB线是插到电脑的USB3.0 接口上的。其他USB3.0设备在这个接口上能够被识别为USB3.0的设备。调试了几天,情况任然是这样。

请问,为什么会出现这种问题啊?有什方法解决这个问题吗?

2024-02-29 08:13:14

你好,我已经用 cyusb3014 编写了固件,开机后可以成功枚举。 现在我正在开发 USB 的 dp altmode 功能。 当视频信号通过USB成功传输时,我的usb3.0连接将断开(我

2024-02-23 08:17:45

最近用cyusb3014做了一个项目,采用的type-C接口,系统识别为USB2.1接口,不知何故?

2024-02-29 06:04:26

这个 CYUSB3014Layout 有什么要求了?u***3.0官方开发板cyu***3014原理图,这个开发板的配套的资料在那里下了?有没有USB3.1的芯片了?

2017-09-06 13:49:34

【USB专业超级开发群】CYUSB3014 CY7C68013 QQ群号:77497621(目前群友990多人)注意:本群由于人数众多,为了让新群友能加入,会不定期对久不发言的群友进行清理,如果想再加入的可以再次加入!致力于Cypress产品推广和技术交流

2015-08-28 09:33:53

FPGA和USB3.0通信-FX3硬件设计简谈本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB...

2022-01-26 07:04:31

我参考的是CYPRESS官方例程AN65974。FPGA以100MHz的时钟读取CYUSB3014的数据没问题。但由于后续存储器比较慢,现在想以50MHz的时钟读取CYUSB3014的数据,数据线

2024-02-29 08:09:43

现在在做基于FPGA的USB3.0与PC的数据传输,用的是FX3 CYUSB3014芯片,片子和xilinx的S6芯片集成在一个开发板上,按照厂家提供的固件程序,采用同步从FIFO模式,PC传数据

2016-12-08 22:05:32

我遇到了一些问题,我现在用的芯片命名cypress3014肿消,意识到设备(cypress3014)连接到主机(USB3.0)与USB3.0的表,当USB模式是USB3.0,没有问题。但我想知道,当

2018-10-10 14:49:59

CYUSB3014型USB3.0+FPGA电路设计详解小梅哥2016年12月29日星期四芯航线AC6102开发板上,使用了一片Cypress的USB3.0全协议芯片CYUSB3014作为FPGA

2016-12-29 21:04:26

` 本帖最后由 小梅哥 于 2017-8-10 14:38 编辑

AC6102开发板通过一片Cypress的CYUSB3014芯片实现对USB3.0高速传输的支持。CYUSB3014又称FX3

2017-08-10 14:35:52

我正在使用名为 cyusb3014.Yesterday 的芯片开发我的应用程序, 我发现当 USB 设备与PC连接时,以下代码将崩溃。 同时,\"控制中心\"将无法正常工作

2024-02-23 08:31:08

我们使用CYUSB3014作为USB3.0数据传输方案,目前处于试产阶段。试产过程中偶尔出现板卡连接至PC后,USB3.0无法识别的情况。

固件使用的官方SlaveFifoSync固件。问题板卡上电

2024-02-23 06:12:21

需求是STM32的数据通过FSMC传输给CYUSB3014,再USB传给PC。

1.请问使用STM32的FSMC与CYUSB3014通信,3014的GPIF要设置成什么模式?是否是同步从设备FIFO

2024-02-27 07:52:56

对于slavefifoasync这个固件,想要在里面启用control endpoint,但是FPGA的信号线应该连接CYUSB3014的哪个引脚?

另外,请问在slavefifoasync这个固件中如何增加control endpoint的功能。

2024-02-27 06:49:52

在使用CYUSB3014时,如果VBUS pin悬空,VBATT pin供电3.6V~4.2V(其他power pin都正常供电)的情况下,3014可否通过USB2.0跟上位机通信

是不是只有

2024-02-28 07:17:59

CYUSB3014芯片选用连续传输模式,但由于数据量有限,平时不传输数据时候,将CYUSB3014设置为不可用,在传输数据时将芯片选择为可用,在传输数据,不知道这么使用是否正常,会不会影响CYUSB3014工作状态;

2024-02-28 07:29:24

运行,但是不能使用USB3.0功能了。请问我应该怎么样能让FX3被识别出USB3.0呢?谢谢!麻烦了。

2024-02-28 08:14:22

USB3.0总线的软件部分该怎样去设计?USB3.0总线的硬件部分该怎样去设计?

2021-05-21 06:01:20

满足设计高速数据采集系统的设计要求,而USB3.0技术的出现无疑解决了上述窘困。因此,本设计选用了USB3.0芯片CYUSB3014作为USB3.0控制芯片,不仅提高了数据传输的速率还能保证数据传输

2018-08-09 14:18:42

我在 cyusb3014 的 spi 主机上安装了一个 spi 从属设备来读取电压。 我知道芯片读取电压值的过程,但我不知道该如何使用 cyusb3014 的 API 来读取 adc 芯片收集的电压

2024-02-23 07:50:04

您好,我想通过上层机测试cyusb3014在 USB 2.0和 USB 3.0模式下的读写速度。 如何在不更换固件的情况下控制是通过上位机以 USB 2.0 还是 USB 3.0 速度连接? 谢谢。

2024-02-27 06:24:46

到CYUSB30142、将板上的USB连接器连接到测试夹具(KEYVIEW),图片上传3、运行TX测试软件(KEYVIEW的U7243B)4、断开测试夹具并复位CYUSB3014(如软件要求)5.将固件下载

2019-10-25 07:54:20

, my design contains an FX3 USB3.0 controller CYUSB3014 and Artix-7 FPGA. I want to configure my FPGA

2019-01-22 11:06:25

question is how to deal with DM (pin A10) and DP (pin A9) of CYUSB3014 if USB 2.0 protocol is not applied.

2018-10-08 10:17:06

对cyusb3014经Control Center写入slavefifo + CDC固件后,低概率被枚举为 USB2.0 接口,正常为 USB3.0 接口 , 这个问题通常要考虑哪些原因所致呢?

2024-02-27 07:36:10

急求 LATTICE 3 USB3.0方案技术支持,BT1120信号源,USB3.0输出无视,寻高手救急!!!

2016-01-22 10:17:16

现在使用cyusb3014,将数据通过FPGA发送到CYUSB3014再到电脑端, 每次发送1024个字节,固件使用的官方的固件, 时钟是100M,总线是32位宽,总的数据速率在640Mbps

2024-02-28 07:33:12

我在使用CYUSB3014的过程中,将芯片配置为了USB3.0 + UART模式,然后遇到两个问题

1> 在32位总线下 UART的TX和RX配置在GPIO55 和 GPIO56

2024-02-28 07:48:22

使用 cyusb3014 主模式时出现数据宽度问题。

我将 AutoMaster 的示例更改为在 FPGA 中访问标准 FIFO。 有两个变化:

1. GPIF 状态机要兼容标准 FIFO 接口时序

2024-02-23 06:16:59

如题,请问各位大神,用CYUSB3014的时候,怎么样增强芯片的抗干扰能力,目前在测试EFT(+/-2kv 5Khz和100Khz)和ESD的时候,都会导致CYUSB3014和PC的连接断开,感觉和按下FX3_RESET按键的效果一样,针对RESET电路,怎么样增强抗干扰能力呢?

2024-02-28 07:35:29

现分享一份知名USB老鼻祖厂商---Cypress公司的一份关于基于USB3.0 芯片CyUSB3014的硬件设计。其内容包括了该芯片的电源、时钟,以及特别是关于USB信号方面的布线考虑,很不错

2019-05-10 09:28:53

[i]请问CYUSB3014 支持安卓设备吗?应该使用什么驱动呢

2024-02-28 06:34:02

请问CYUSB3014有没有提供MacOS系统驱动?如果有,我可以在哪里获取得到?与其它MacOS驱动相比有没有使用注意事项?

2024-02-27 08:34:59

我正在学习CYUSB3014芯片。 当我使用 USB控制中心时,我发现了三种刻录方法。有人能解释一下RAM模式和SPI闪存模式之间的区别吗? 当我选择 RAM 方法或 SPI FLASH 方法时,IMG 程序是如何加载和运行的?

2024-02-26 07:27:04

您好,请问FX3 有USB3.0 OTG HOST功能吗?

我司需要用MCU(STM32F4)高速采集AD数据,MCU把数据传给FX3 (CYUSB3014),FX3再通过USB3.0(速度需要大于

2024-02-28 07:19:26

跪求一个cy3014 USB3.0的SlaveFIFO固件,32位、FLAGA、flagb,带FLAG标签,flagd都有作用的,谢谢!《周易蓝天XY@ 163.com》以上来自于百度翻译 以下

2018-08-29 16:09:26

通常情况下CYUSB3014枚举后的结果都会显示为Bootloader

如果我向让USB3.0连接以后,将我连接的设备识别成ChinaBeijing .请问我应该如何操作??

2024-02-28 08:01:18

CYUSB3014中文数据手册,用于USB3.0的开发设计

2017-01-22 14:05:59 0

0 可以和FPGA搭配使用的USB3.0 PHY芯片 通过之前的介绍FPGA和USB3.0通信-USB3.0协议介绍,我们大致了解到USB3.0整个协议异常复杂,就连物理层都需要SerDes(FPGA

2021-11-09 09:36:32 7322

7322

FPGA和USB3.0通信-硬件测试(一)SDK的安装 本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB

2021-11-18 14:20:45 2206

2206

FPGA和USB3.0通信-FX3硬件设计简谈本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB...

2021-12-01 20:06:08 23

23 可以和FPGA搭配使用的USB3.0 PHY芯片通过之前的介绍<FPGA和USB3.0通信-USB3.0协议介绍USB3.0 PHY简介首先我们需要了解PHY具体完成哪些工作以及我利...

2021-12-20 19:11:16 32

32 USB3.0开发之bulkLoop上位机程序 一、开发测试软件 硬件平台:Cypress公司的CYUSB3014 软件平台:Visual Studio 2017 + Qt5.12 实现应用程序产生

2023-05-29 15:16:36 7

7 要求用qt编写上位机程序,实现FPGA通过cyusb3014芯片完成数据的收发。下面是采用通过cypress并安装usb官方驱动的环境搭 建,后续继续更新程序的编写。

一、安装nodejs ①下载

2023-05-29 16:05:34 3

3 泛的还是USB3.0,本篇也是主要介绍USB3.0。它是超高速传输接口,可以提供最高5.0Gbit/s的传输速率,并且相比与USB2.0,增加了新的电源管理功能,支持待机,睡眠等,更加省电。并且也从半双工

2023-11-07 11:01:54 578

578

德赢Vwin官网

App

德赢Vwin官网

App

评论