,我们依旧借助PYNQ_z2来完成。 1. ZYNQ

功能块 ZYNQ中包含两大

功能块:

PS部分和

PL部分。

PS部分指Processing System,一个

2020-12-25 14:11:50

6843

6843

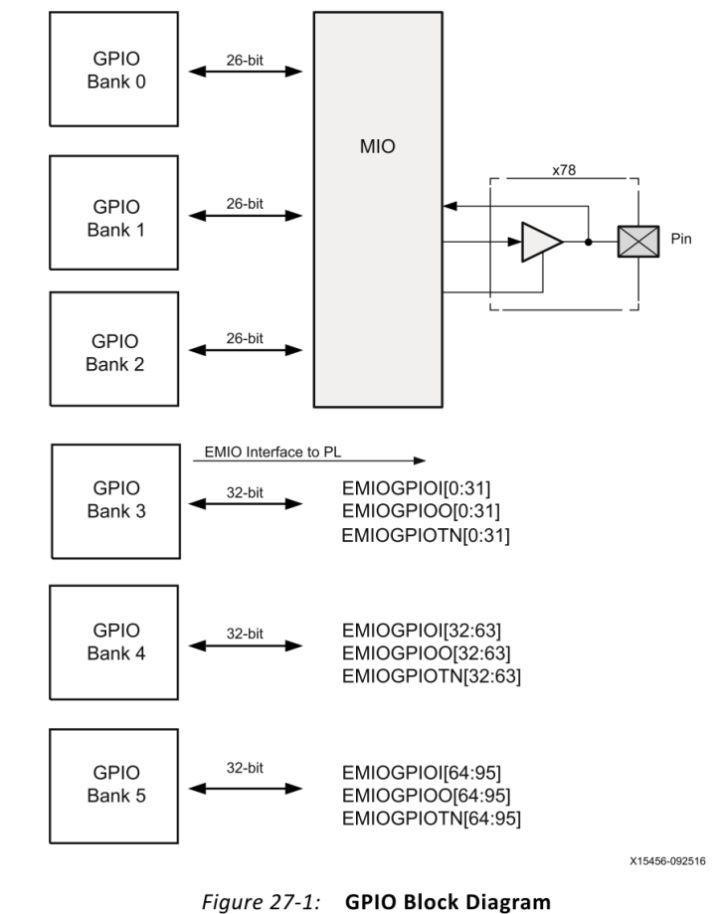

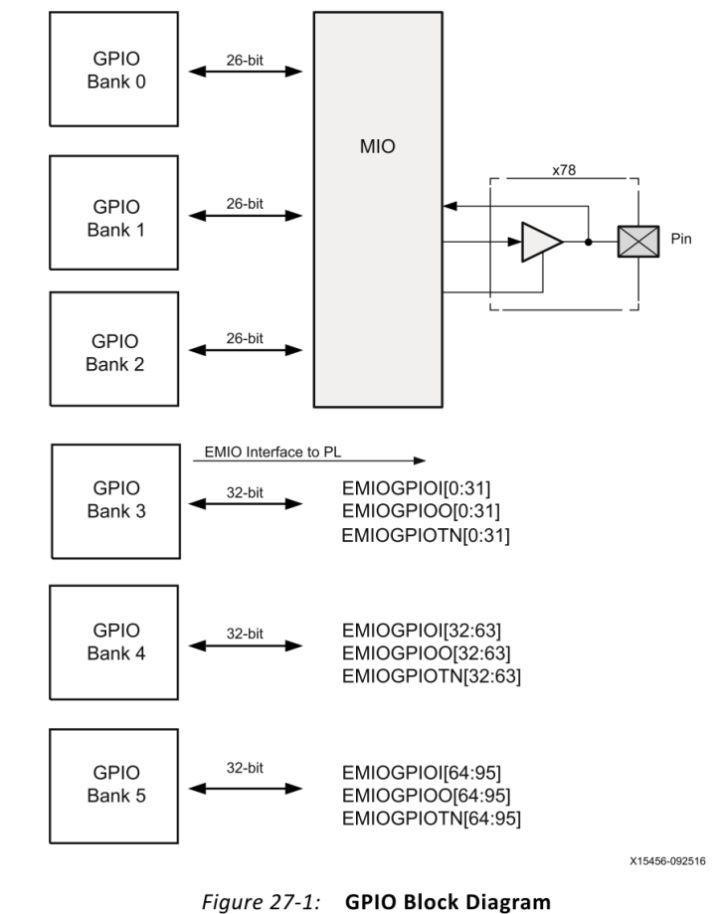

如果想用

PS点亮

PL的LED灯,该如何做呢?一是可以通过EMIO控制

PL端LED灯,二是通过AXI GPIO的IP

实现控制。本章介绍如何使用EMIO控制

PL端LED灯的亮灭。同时也介绍了,利用EMIO连接

PL端按键控制

PL端LED灯。

2021-01-30 10:05:00

6730

6730

使用zynq最大的疑问就是如何把

PS和

PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让

PS端通过AXI总线控制

PL端的LED灯,实验虽然简单,不过可以让我们了解

PL和

PS是如何结合的。

2021-02-01 10:06:00

6183

6183

PL和

PS的高效交互是zynq soc开发的重中之重,我们常常需要将

PL端的大量数据实时送到

PS端处理,或者将

PS端处理结果实时送到

PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00

12917

12917

有时CPU需要与

PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM

实现此要求。本章通过Zynq的GP Master接口读写

PL端的BRAM,

实现与

PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

2021-02-22 13:51:00

7359

7359

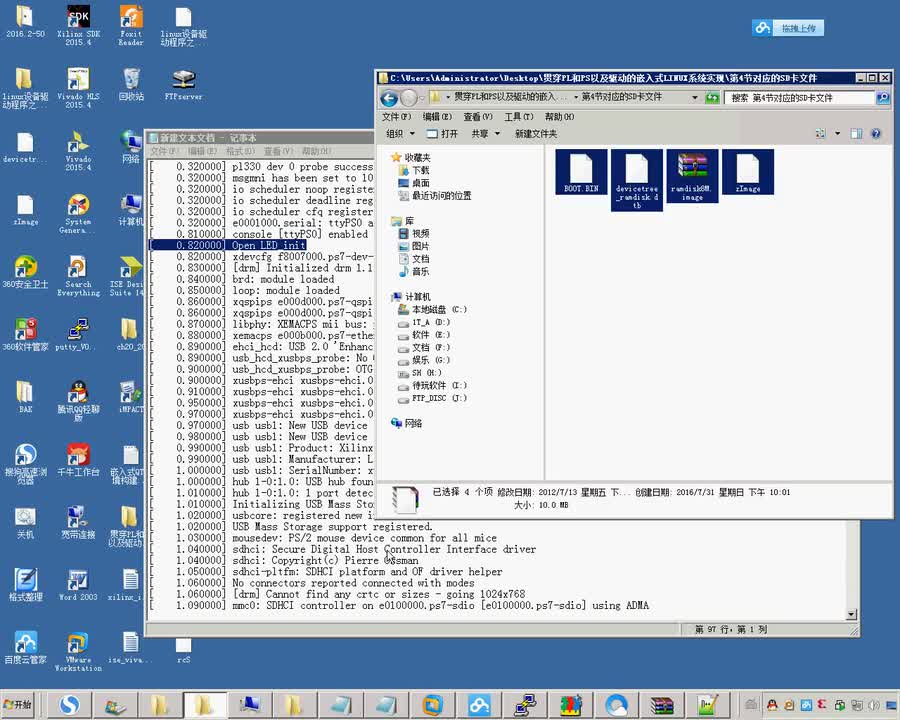

(Progarmmable Logic), 就是 FPGA 部分。 ZYNQ7020的整体架构如下图所示 Zynq 就是两大

功能块,

PS部分和

PL部分, 说白了,就是 ARM 的 SOC 部分,和 FPGA

2021-05-12 10:25:31

13960

13960

。 axi_timer_pwm_demo案例 1 案例

功能案例

功能:

PS端通过AXI4-Lite总线发送命令至

PL端AXI Timer IP核,IP核再根据命令通过PWM方式控制评估底板

PL端LED5的状态

2021-09-07 17:03:30

2881

2881

xilinx mpsoc 平台中,

PS和

PL进行交互时,

PS需要获取

PL发出的中断信号。从 mpsoc 技术参考手册 ug1085 TRM 中可知,

PL给到

PS的中断有两组

2023-08-24 16:06:22

560

560

拉挂适配器的现象。该芯片将功率管内置从而

实现较少的外围器件并节约系统成本。

PL7501C 的升压开关充电转换器的工作频率为 600KHz, 最大 2A 输入充电,转换效率为 90%。

PL

2020-12-09 22:08:48

ZYNQ进阶之路9--

PS端

实现FreeRTOS嵌入式系统导论FreeRTOS简介

实现步骤导论在之前的章节中我们我们完成了

PS端、

PL端和

PS+PL的一些工程,本章节我们插入一个小插曲,讲解

2021-12-22 08:29:20

。光照传感器Po188(SMD1206)+ 取样电阻就可

轻松

实现。我们是原设计开发商,有绝对的价格优势。 深圳市欧恩光电技术研究所高小姐QQ:597720281TEL

2009-01-21 12:02:50

本帖最后由 何立立 于 2018-1-9 15:03 编辑 ZYNQ 、AXI协议、

PS与

PL内部通信 三种AXI总线分别为:AXI4:(For high-performance

2018-01-08 15:44:39

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含

PL端Vivado工程,主要使用Xilinx提供的标准IP核配置

PL端资源

实现接口扩展,同时包含

PS端裸机

2021-05-28 14:28:28

大家好! 最近要做一个控制仪器的项目。仪器的型号基本定了,现在考虑的问题是扩展性。假如程序最后

打包交付给用户以后,客户又想添加一个仪器型号,这时有没有一种方法,不用重新

打包交付程序,给用户一个

功能模块,按照说明放大某一位置就可

实现? 请各位高手给个思路,不胜感激!

2016-07-26 14:47:55

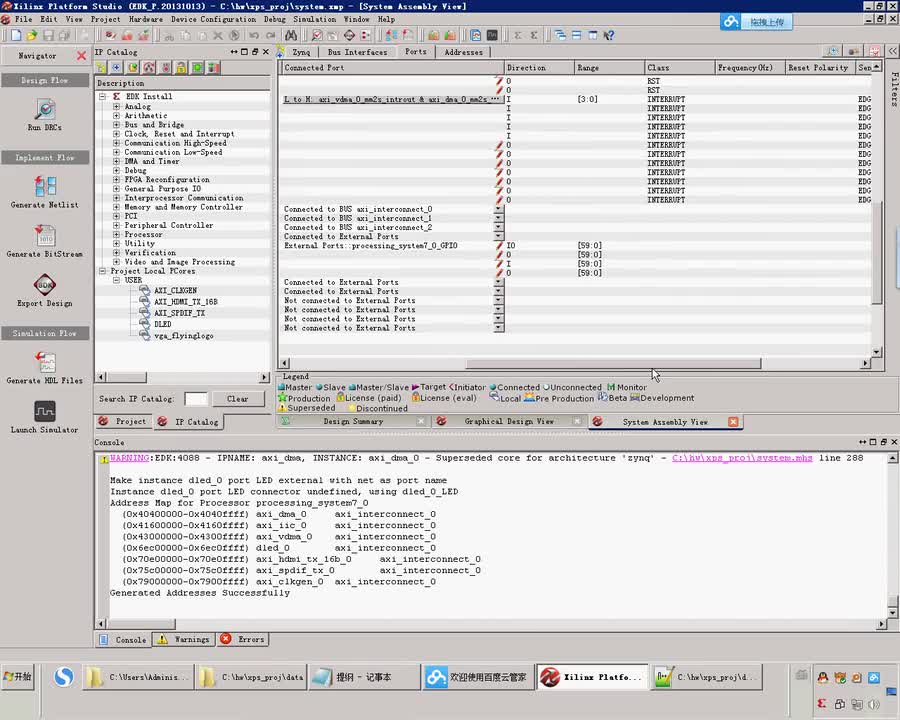

使用XPS时,然后将.xmp导入planahead,生成一个比特流文件。我可以使用chipcope / impact进行配置,从

PS->

PL运行获取FCLK还是我必须导出到sdk?我正在

2019-09-05 06:03:46

难道

pl的时钟放在底板上了?

2016-02-16 00:07:37

嗨,我必须找出zynq 7020

PS和zynq

PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从

PS转移到

PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

一直纠结于怎样给

PL提供时钟,zynq开发不同于一般的FPGA开发。其中时钟和复位问题就是相当重要的问题,有两种方式可以为

PL部分提供时钟和复位:1、

PS部分可以产生四个毫无关系的输出时钟和复位信号

2015-06-08 17:29:32

本帖最后由 blackroot 于 2015-6-10 17:06 编辑 一直没搞懂

PS怎样给

PL提供复位和时钟,今天这个问题终于解决了~~~~~用一个简单的例子来说明一下,怎样使用

PS输出

2015-06-10 16:59:53

配置

PS和

PL,把这些时钟信号利用起来。此时我们就可以充分利用Vivado提供的强大的集成开发

功能,

轻松

实现

PL“

打包”

PS的

功能——这与通常我们看到的ZYNQ的概念有点不同:

PS是主体,而

PL做为一

2015-06-01 11:54:12

核是我们自定义的IP核,

实现了

PL端从BRAM中读出数据的

功能,除此之外,

PS端通过AXI总线来配置该IP核读取BRAM的起始地址和个数等。由框图可知,本次实验创建的BRAM为双端口的RAM,其中一个

2020-09-04 11:08:46

错误。然后,我在SDK中编程

PS端,led闪烁正确的频率!我的问题,当锁定Zynq

PL时钟?

PS程序之后?需要多长时间?是不是意味着,

PL配置期间LED闪烁错误,在非易失性Flas Boot中编程

PS期间(或之后)闪烁?谢谢的Berker

2020-08-27 15:09:19

我想给板子接上一个u***接口的键盘,不跑操作系统,只用

ps部分接收键盘的数据然后传递给

PL,不知道如何编写sdk的代码来跟u***的phy通信呢?有没可以参考的例程或者文档?

2015-12-16 17:12:38

连出,亦可通过EMIO从

PL端引脚连出。同时,亦可通过

PL端逻辑资源使用IP的方式

实现网口

功能。本文通过外接的TL-MultiEthP多网口模块,分别在

PS端和

PL端进行了千兆网口拓展。图 3

2021-10-22 09:43:10

如何

轻松地

实现对步进电机的控制?

2021-10-15 06:02:04

pyton

打包成exe命令有哪几个?如何利用Python

实现

打包exe文件?

2021-07-12 08:04:00

你好,我已经创建了一些示例SDSOC项目并注意到了这一点。我已经检查过,在执行一个持续很长时间的

功能的

PL期间,处理器没有停止,Zynq FPGA中的Core A9仍然保持在100%。如果

2020-05-08 10:00:52

而无法再操作。我的目标是使用一个仅包含

PL部件设计的比特流,不需要任何

PS描述或

PS和

PL之间的连接来配置

PL,而linux(

PS)运行良好。实际上,我想设计一个系统来逐个配置来自不同用户的许多不同位

2020-05-21 07:07:50

嗨,我有一个zc702板。我是EDK的新手。我为

PL点了一个小代码来点亮LED。我没有在SOC中使用

PS。我已经通过JTAG编程了它,它的工作原理。但是当我尝试从SPI FLASH编程时,我无法正常

2019-09-12 10:22:59

我的设备是zedboard702,我知道如何在使用

PS和

PL时使用SDK生成启动映像和程序闪存。问题是我只是使用

PL,现在如何编程flash?

2019-09-30 09:43:18

亲爱的大家,我只是想知道如何找到Ultrascale +的

PL和

PS的地址转换(映射方案到DRAM-我的意思是哪个等级,库等)?

2019-10-16 08:35:37

领域。

PL5501控制器在降压、升降压和升压运行模式下采用恒定的时间控制,以

实现的负载和电压调整。可编程开关频率,可以设置开关频率为150kHz、300kHz、600kHz或1.2MHz。该芯片还具

2021-09-29 10:18:16

性能:◆是一款适用于输入电压高达100V的超宽输入范围、高性能同步降压DC-DC的PWM控制器。◆通过驱动-对外部整流和续流MOS-FET

实现大输出电流(可达10A)、超宽出入范围( 12-100V

2021-11-24 15:17:58

大家好,我已经在

PS中产生了一个100Mhz的时钟信号,并使其在外部被

PL接收。我使用了原始的ODDR但没有成功我可以从引脚输出100 Mhz时钟。有什么建议么??以上来自于谷歌翻译以下为原文

2019-02-22 09:09:05

用430

实现心电信号的接收,处理和发送,发送时需要数据

打包,求数据

打包程序与方法

2014-11-04 18:20:53

为什么一个简单的程序运行不了,请求帮忙看一下。做个LED流水灯,是想用

PS部分生成100MHz的频率,然后用这个频率来

实现

PL部分三色led移位,但是好像

PS部分有问题,不知道怎么配置了。这是

PS

2016-01-02 21:35:38

对应的信号

功能后,在

PL的代码里面就不需要写任何的逻辑,甚至引脚分配都不需要(生成的

PS系统会自动分配)。但是EMIO就要在

PS的系统中引出,然后在

PL顶层源码中申明端口类型,做引脚分配(因为EMIO用

2019-10-12 17:35:16

给照片

轻松换背景(让

ps更

轻松)在

PS图象处理时常常会遇到去除图象背景操作,通过

PS去除有时候非常的墨迹,通过“照片

轻松换背景”软件可以轻

轻松松去除背景,本软可以图像合成最困难和最费时的操作是抠图

2008-09-19 10:00:23

请问zynq 怎么

实现

PS与

PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

XAPP1251说明显示,可以在Zynq ARM处理器上运行XVC服务器来控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一个FPGA中控制

PLJTAG?可以使用运行在设备

PS部分上

2020-07-30 13:51:19

PL7502/

PL7504 是一款集成锂电池充电管理、同步升压转换器、电池电量管理和保护

功能的带指示灯蓝牙充电座 SOC。

PL7502/

PL7504 芯片完整的

功能集成

2022-05-21 15:18:11

摘要:在数据库管理系统GKD-BASE上设计并

实现了兼容Oracle

PL/SQL V2.3语言规范的

PL/SQL引擎,扩展了GKD-BASE过程处理

功能。GKD-BASE数据库是一

2006-03-11 13:22:41

840

840

用鼠标一点刚用Authorware做的一个小课件,主文件还不到1MB,真是短小精悍,我非常满意。哈哈,现在开始

打包。咦?怎么搞的,

打包后一拷

2009-06-17 00:00:05

601

601

32位高性能单片机

轻松

实现连接

功能 Microchip(美国微芯科技公司)近日在80 MHz 32位 PIC32单片机(MCU)产品组合的成功基础上推出3个全新系列单片机,提供高达128 KB RAM

2010-01-12 16:23:49

764

764

一步一步学ZedBoard:使用

PL做流水灯:目的是为了学习不使用ARM

PS情况下,只对Zynq

PL的编程方法,同时学习Xilinx PlanAhead工具的使用方法。(本资料是其相应的完整工程文件下载)

2012-12-05 13:52:39

185

185

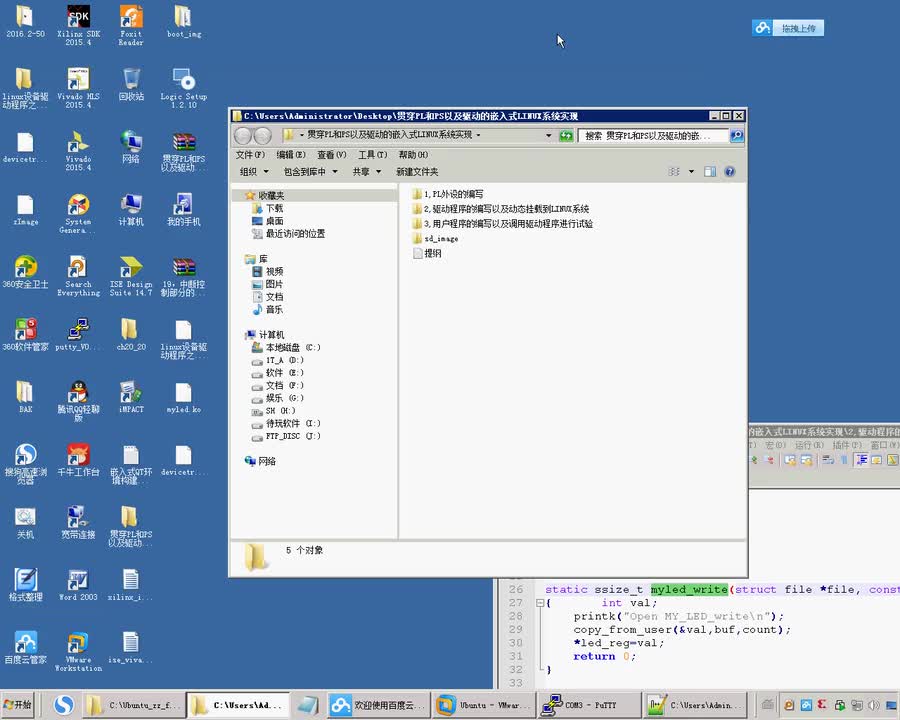

本文通过实例详细解析如何利用Zynq-7000的

PL和

PS进行交互。实际上,Zynq就是两大

功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,

PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22

53205

53205

分享下

PS与

PL之间数据传输比较另类的

实现方式,

实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、

PL端接口为FIFO接口;

PS到

PL的数据传输流程:

PS

2017-02-08 01:00:11

1431

1431

到目前为止,我们已经在之前的文章中聊过Zynq SOC内部的

PS和

PL,以及在Zynq SoC

PS部分的ARM Cortex-A9处理器上运行的操作系统。但是有一个领域我们还没有去探索过,那就是在芯片的

PL上构建软核处理器。

2017-02-08 14:04:41

989

989

了解Zynq

PS/

PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的

PS(处理器系统)与

PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11

957

957

我们先来了解一下上节中介绍的Zynq SoC

PS/

PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41

469

469

《一步一步学ZedBoard & Zynq》系列第二篇,目的是为了学习不使用ARM

PS情况下,只对Zynq

PL的编程方法,同时学习Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11

3749

3749

构建SoC系统,毕竟是需要

实现

PS和

PL间的数据交互,如果

PS与

PL端进行数据交互,可以直接设计

PL端为从机,

PS端向

PL端的reg写入数据即可,本节研究如何再

实现

PL端对DDR3的读写操作。

2017-09-18 11:08:55

23

23

Zynq芯片中,

PS(ProcessorSystem)和

PL(Programmable Logic)之间提供了一共9个双向读写的通信端口,他们分别是: M_GP0 M_GP1 S_GP0 S_GP1

2017-11-17 10:03:39

11543

11543

zedboard可以将逻辑资源和软件分别映射到

PS和

PL中,这样可以

实现独一无二和差异换的系统

功能,主要分为两大部分,处理系统和可编程逻辑。以及二者之间的互联特性。这篇笔记主要记录zedboard的大体架构。

2018-06-26 06:24:00

6394

6394

承德科胜纸箱侧面

打包机|侧面

打包机|河北

打包机 承德科胜自动纸箱侧面捆扎机 适合产品;化妆品,食品,农药纸箱的

打包设备简介:侧面

打包机可对灰尘,粉末较多的大型物体,和重量较重的物体进行

2018-08-21 10:46:49

213

213

/60HZ)3PH-220V/380V(50/60HZ)功率:0.85KVA原理及特点: 自动

打包机外形设计简单美观;电机+减速器+凸轮+紧缩臂运作;

打包紧力卓越,故障少,维修方便;

打包机零部件均由电脑数控机床精密加工;

打包动作柔和,耐用性卓越,

打包

功能完善;

打包结束后电机马上停止,省电实用。

2018-08-21 10:47:23

290

290

承德科胜低台

打包机|瓷砖

打包机|河北

打包机 承德科胜瓷砖低台

打包机 主要用途:袋装酱油,袋装醋,食盐的

打包机 型号规格: SK-3型低台型

打包机 主要用途: 适用于各种大小货物的

打包

2018-08-21 10:48:03

351

351

承德科胜高台

打包机|隔热板

打包机|河北

打包机 承德科胜高台pp带

打包机 主要用途:辣椒酱,酱菜,奶茶,藕粉高台

打包机 型号规格: SK-1高台

打包机 主要用途: 适用于各种大小货物的

打包

2018-08-21 10:48:34

179

179

承德科胜双变频

打包机|书本

打包机|河北

打包机 承德科胜双变频书本

打包机 适合

打包;柿饼,书本,咖喱粉,适合各种大小货物的

打包技术参数:

打包速度:1.5sea/strap最小

打包物:60mm

2018-08-21 10:51:08

258

258

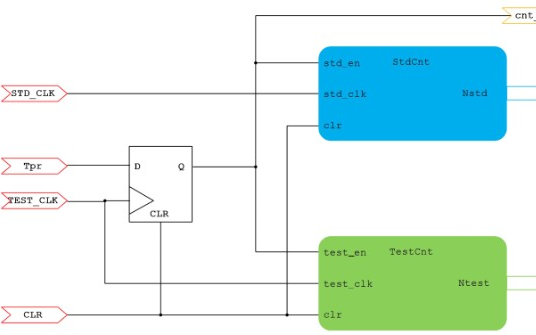

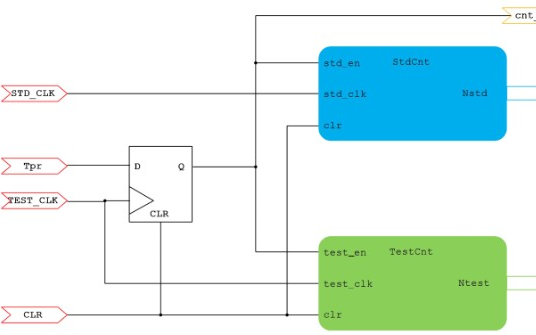

这一节我们

实现一个稍微复杂一点的

功能——测量未知信号的频率,

PS和

PL通过AXI总线交互数据,

实现我们希望的

功能。

2018-12-08 11:00:30

1406

1406

Zynq在

PS和

PL之间有9个AXI接口。

2018-12-30 09:45:00

6907

6907

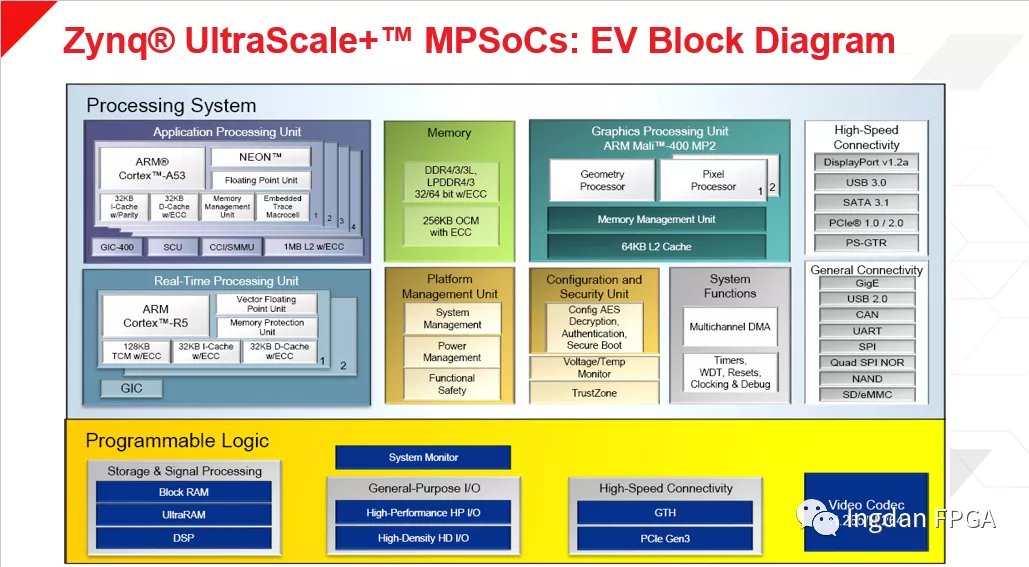

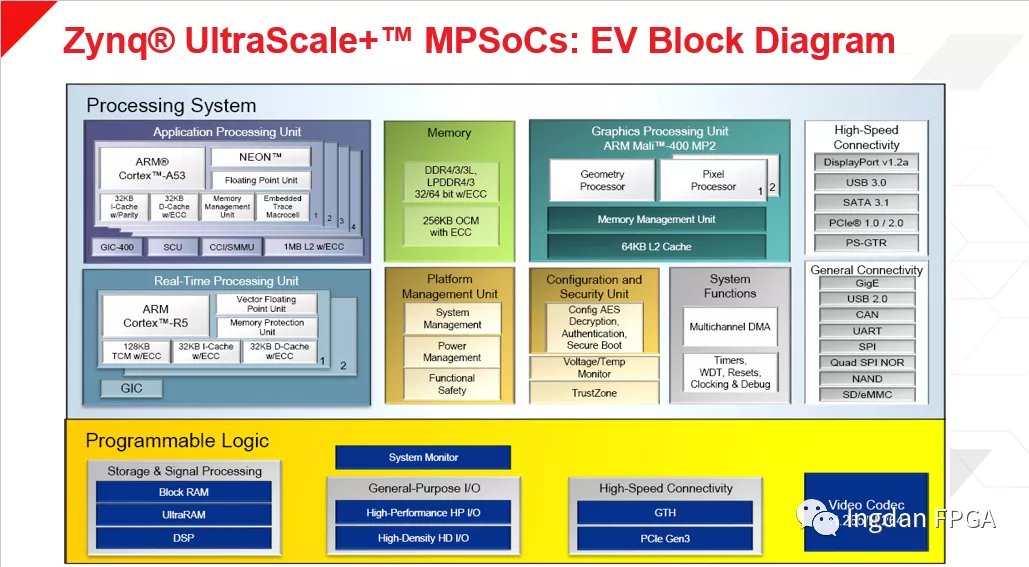

MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对

实现

PS/

PL之间的数据交互感到头疼。

2020-09-15 09:27:00

11208

11208

DMA的总结 ZYNQ中不同应用的DMA 几个常用的 AXI 接口 IP 的

功能(上面已经提到): AXI-DMA:

实现从

PS内存到

PL高速传输高速通道 AXI-HP----AXI-Stream

2020-10-09 18:05:57

6391

6391

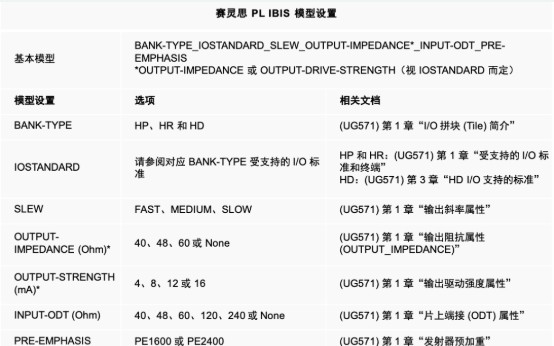

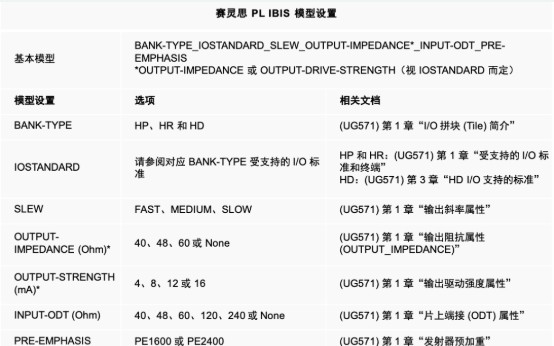

。 本篇博文旨在提供有关如何为可编程逻辑 (

PL) 和处理器系统 (

PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。 本文主要分 3 个部分:

PLI/O 标准

PSMIO

2020-10-15 18:29:15

2147

2147

刚学ZYNQ的时候,看到里面反复提到

PS和

PL,还以为

PS是PhotoShop的意思,

PL是哪种型号的简称。 稍微了解之后才知道,ZYNQ是ARM和FPGA的组合,

PS是programming

2021-06-18 16:09:46

8666

8666

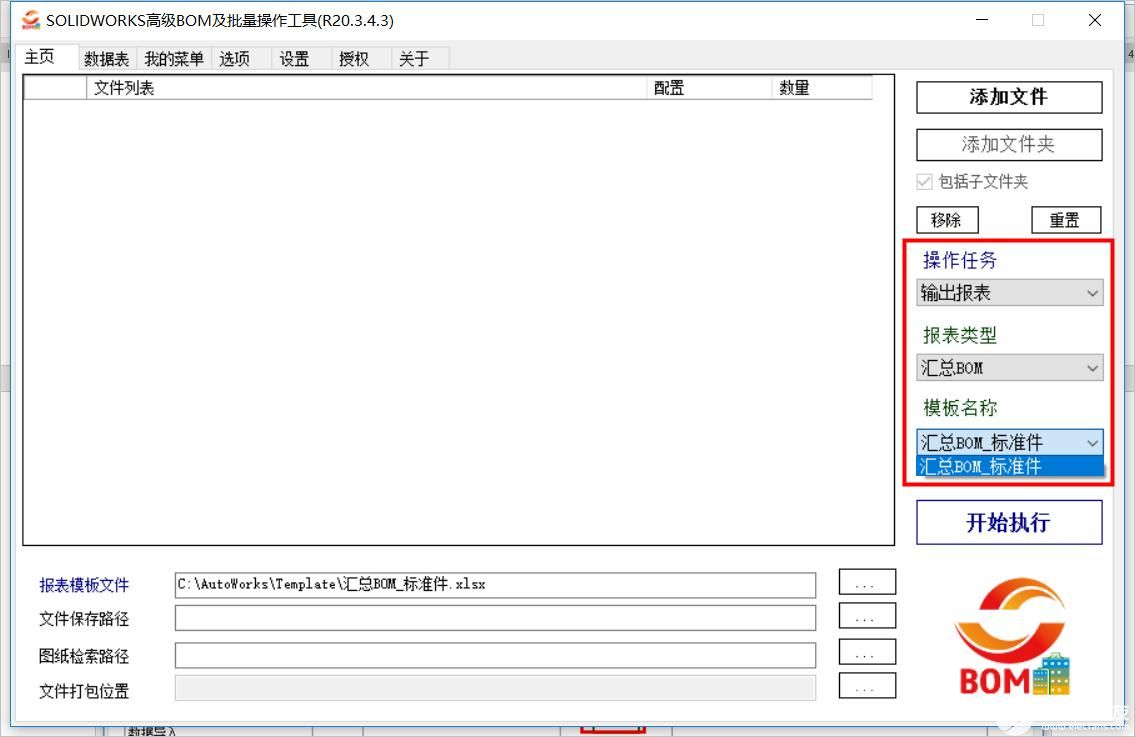

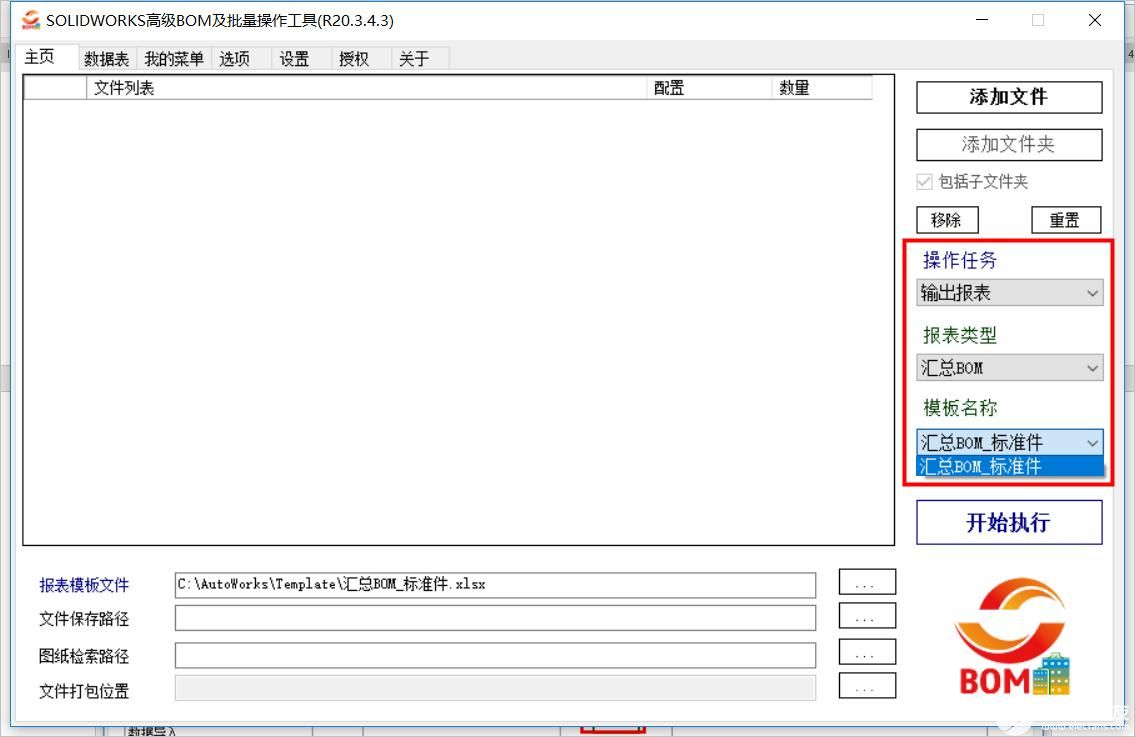

SolidKits BOMs高级BOM及属性批量导入工具的

打包

功能,无需打开SOLIDWORKS,即可高效、准确的一键完成各种结构BOM导出,汇总BOM生成,批量导入属性,自动建立结构,

实现规范化管理,并自定义

打包操作。

2022-02-21 17:04:02

1441

1441

这篇文章记录ZYNQ7020的

PS端的基本开发流程,关于

PL端的开发流程,参考之前文章,这里放个超链接。

2022-07-24 18:12:57

5860

5860

目前基于MPSOC的一些参考设计中并没有

实现开机画面的

功能,那在一些带显示屏的产品在设计的时候就需要这一

功能,基于原来传统的方式也可以在FPGA中来

实现,今天分享一个在

PS侧来

实现开机画面,以节省

PL侧的宝贵资源。

2022-08-02 10:23:20

851

851

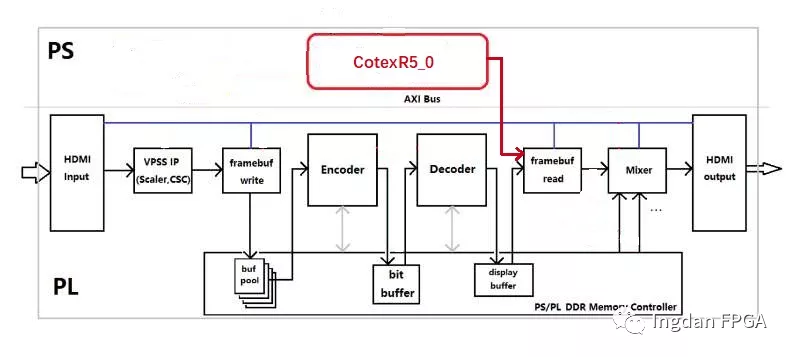

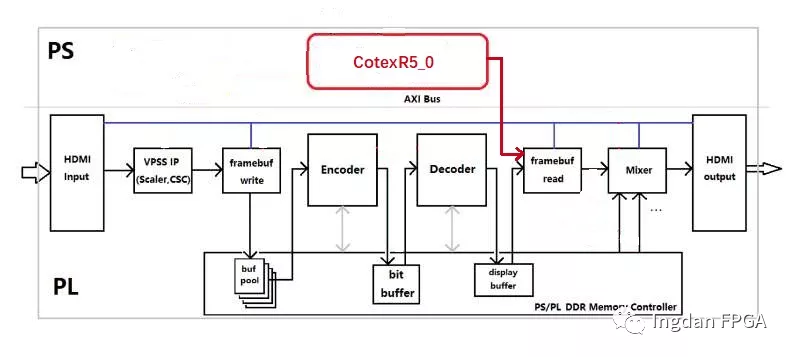

部分 ZynqUltraScale+MPSoC的可编程逻辑(

PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自

PL或

PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

2022-08-02 16:48:15

2472

2472

MPSoC含有

PS、

PL;在

PS和

PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,

PS和

PL之间有接口和信号线被关闭。加载bit后,软件才会打开

PS和

PL之间的接口和信号线

2022-08-02 09:45:03

676

676

德赢Vwin官网 网站提供《将Zynq

PS和

PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29

2

2

S_AXI_ACP_FPD接口

实现了

PS和

PL之间的低延迟连接,通过这个128位的接口,

PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故

PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53

1708

1708

德赢Vwin官网 网站提供《基于

PS和

PL的1G/10G以太网解决方案应用笔记.pdf》资料免费下载

2023-09-15 10:29:25

1

1

德赢Vwin官网 网站提供《基于

PS和

PL的1G/10G以太网解决方案.pdf》资料免费下载

2023-09-15 10:05:18

0

0

资料\Demo\All-Programmable-SoC-demos\”目录下。案例包含

PL端Vivado工程,主要使用Xilinx提供的标准IP核配置

PL端资源

实现接口扩展,同时包含

PS端裸机/Linu

2023-01-03 15:50:37

18

18

德赢Vwin官网 App

德赢Vwin官网 App

评论