德赢Vwin官网

网核心提示:本文为玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯,内容精彩,敬请对德赢Vwin官网

网保持密切关注。基于Zynq PL的流水灯是使用PL做流水灯实验,目的是为

2012-12-05 14:25:41 12770

12770 8.5部分实例

2015-03-12 17:44:47

。如图所示,在Zstar板子左侧靠下的位置有一排的LED指示灯,从左往右数第4个、第5个和第6个LED指示灯分别是D3、D2和D1。 2 板级调试参考文档《玩转Zynq-环境篇

2019-08-28 09:26:47

and Configuration 《Xilinx Zynq Soc与嵌入式Linux设计实战指南》第3章更多资料共享 链接:https://share.weiyun.com/5s6bA0s`

2019-04-16 06:56:32

灵活性也就越小。在Xilinx的FPGA器件中,IP核设计是非常重要并且必不可少的一部分,应该说,前述的软IP、固IP和硬IP,在我们Zstar板载的Zynq上都能够找到踪影。而对于Vivado来说

2019-09-06 08:13:18

`玩转Zynq连载28——[ex50] 第一个Zynq系统工程“HelloZynq” 更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接

2019-09-30 12:57:32

`玩转Zynq连载30——[ex52]基于Zynq PS的GPIO控制 更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https

2019-10-10 11:21:06

的就是PL的引脚)。关于MIO和EMIO的关系,更形象直接的可以示意如图所示。MIO和EMIO都是PS的一部分,但是MIO可以直接连接到Zynq芯片的引脚上,和PL无关;而EMIO需要通过PL的IO

2019-10-12 17:35:16

不同通道使用情况下的数据吞吐量。大家可以在此基础上,更改不同的AXI HP总线时钟频率,以评估时钟频率对AXI HP总线的影响。2 AXI总线协议介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍

2019-11-28 10:11:38

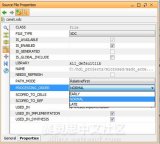

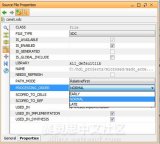

参考xilinx下述3个文档。●pg091-xadc-wiz.pdf●ug480_7Series_XADC.pdf●ug585-Zynq-7000-TRM.pdf的Chapter 30

2019-12-03 11:17:44

一些良好的干净的怪异乐趣。对于那些使用过不同EDA工具的人,我希望easyEDA.com的一瞥至少是有趣的,如果不是鼓励,如果你想尝试不同的东西。在本系列的第2部分中,我将分享我对KiCad的经历

2018-11-01 15:54:02

Wind Turbine (Part 1) 垂直轴风力机(第1部分)以ANSYS 17.0为例。该算例分为两个部分,第一部分将采用运动参考系(Moving Frame of Reference(MRF...

2021-07-12 06:38:54

本帖最后由 飞儿朵朵2012 于 2016-11-3 22:20 编辑

GB 7000.1-2015 灯具 第1部分:一般要求与试验

2016-09-18 22:02:20

GBT 20234.2-2015 电动汽车传导充电用连接装置 第2部分 交流充电接口

2018-03-22 08:02:30

IEC 62305-1(雷电防护 第1部分 总则)前言3简介31. 范围和目标.42. 规范性参考文件.43. 术语和定义.44. 雷击电流参数... 95. 雷电的损害... 95.1 对建筑物

2011-01-22 17:03:54

PADSlogic电子档第2部分有需要的可以下载

2013-09-21 18:00:38

Protel99se 安装好了,一部分ddb文件能打开,一部分pcb格式打不开,该怎么办

2011-12-21 20:14:15

STM32 F 103 C 6 T 7 xxx 1 2345 6 78 第1部分:产品系列名,固定为STM32 第2部分:产品类型;F表示这是Flash产品,目前没有其它选项 第3部分

2014-10-09 19:03:28

TCL 9321/9421部分/9621部分(TDA3505/TEA1014)原理图文件下载

2021-06-25 08:32:05

YY 0505-2012 医用电气设备 第1-2部分 安全通用要求并列标准 电磁兼容 要求和试验 (见附件)

2015-06-03 12:49:54

”的pdf文档。 《深入浅出玩转FPGA(第2版)》 的主要读者对象为电子、计算机、控制及信息等相关专业的在校学生、从事FPGA/CPLD开发设计的电子工程师以及所有电子设计制作的爱好者们。目录第一部分

2017-02-04 17:06:09

`第58章 SPINBOX控件 本期教程讲解STemWin支持的SPINBOX控件。 58. 1 SPINBOX控件介绍 58. 2 官方WIDGET_Spinbox实例 58. 3 使用官方

2015-05-23 11:56:07

本信号链电源优化系列文章的第1部分讨论了如何量化电源噪声以确定其影响信号链器件的哪些参数。通过确定信号处理器件可以接受而不影响其所产生信号的完整性的实际噪声限值,可以创建优化的配电网络(PDN)。在

2021-12-19 08:00:00

使用高速转换器时,有哪些重要的PCB布局布线规则?第一部分讨论了为什么AGND和DGND接地层未必一定分离,除非设计的具体情况要求您必须这么做。第二部分讨论了输电系统(PDS),以及电源层和接地

2018-10-30 14:56:34

使用高速转换器时,有哪些重要的PCB布局布线规则?(第2部分)本RAQ的第一部分讨论了为什么AGND和DGND接地层未必一定分离,除非设计的具体情 况要求您必须这么做。第二部分讨论印刷电路板(PCB

2018-10-30 14:57:01

固件和硬核 IP,我们将把它们留给我们的下一部分——第二部分和第三部分。 在本系列文章中,我们将把我们的谈话分为以下几个部分: 保护您的 IP 内核——第一部分软 IP,第一节:HDL 代码的加密保护您

2022-02-23 11:59:45

关于Zynq的理论部分,文大部分截图摘抄自《zynqbook》ZYNQ架构双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样

2021-07-23 10:11:25

GB 9706.1-2007 医用电气设备 第1部分:安全通用要求

2014-12-23 16:12:22

如何玩转STM32-F429系列

2021-10-13 06:45:39

如何玩转STM32-F429系列控制器?

2021-11-12 06:06:38

/Adam-Taylor-s-MicroZed-Chronicles-Part-180-All-about-the-Xilinx/ba-p/756988但该芯片自带板,Zynq 7020属于Zynq家族。是否可以在电路板上使用它?如果没有,支持reVision的官方(Xilinx / AVNet / ...)主板的最低成本是多少?筹码怎么样?

2019-10-10 06:25:58

如何零死角玩转STM32-F429系列

2021-10-13 08:47:02

如何零死角玩转STM32-F429系列?

2021-10-12 07:43:14

的C2000™ F28379 MCU,开发人员现在可以避免上文提到的很多缺点。

在本系列的下一部分中,我们进一步研究将FPGA引入到驱动和伺服机控制架构中时所遇到的其它挑战。

原文链接

2018-08-31 15:41:28

布局电源板以最大限度地降低EMI:第1部分

2019-09-05 15:36:07

布局电源板以最大限度地降低EMI:第2部分

2019-09-06 08:49:33

问题:1.第1部分看懂一点,第2部分完全不知道要干什么,第3部分那样处理也不知道是要做什么。2.这个电路要实现的功能是一个从几十到几百赫兹的带通滤波。3.已经用Multisim仿真过,得到的结果是

2018-07-26 10:00:39

构建混合测试系统第1部分:为成功过渡奠定基础

2019-11-06 09:36:06

DN110- 微功率降压/升压电路,第2部分:将四节电池转换为5V *

2019-06-11 16:31:41

。图1.抽取系数为8时,每8个样本仅选择第8个样本,抛弃7个样本。你们猜猜第二个问题是什么?在第2部分中,我们将看看其他常见问题之一,敬请期待。

2018-10-26 11:16:21

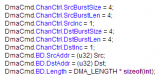

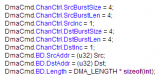

我昨天才发现我的两块microZED板都有相同的MAC地址(第一次将它们同时插入网络)。通过u-boot代码,我看到MAC地址被烘焙到环境中(在zync_common.h中)。#define

2019-09-16 14:57:55

STM32部分知识共享:

2015-08-10 13:43:15

基础普及 笔记1 初识FPGA 笔记2 应用领域 笔记3 开发流程 第二部分 设计技巧 笔记4基本语法 笔记5 漫谈状态机设计 笔记6 复位设计 笔记7 FPGA重要

2012-02-27 10:45:37

STM32标准库的引入视频课程-第3季第6部分 互联网课程品牌《朱老师物联网...

2021-08-03 06:31:06

跪求《深入浅出玩转FPGA(第2版)》这本书电子版

2015-10-08 07:44:27

在学习运算放大器稳定性分析(TI合集)第5部分的时候,计算beta是有点疑惑,为什么beta = VFB / delta VOA ?而不是beta = VFB / VOA?

2022-04-01 10:21:51

野火系列之STM32从初级到玩转单片机PDF教程全集

2013-11-21 20:28:50

本文基于FPGA的 PicoBlaze嵌入式平台,开发了一种利用串口通信,可实时控制的计时器系统。分析了PicoBlaze和串口的结构、原理,提出了计时器的设计方案。基用Virtex-II Pro系列FPGA开发

2010-01-20 15:48:37 19

19 摘要:详细分析8位微处理器IP core PicoBlaze的结构、原理与设计方案;介绍PicoBlaze的指令集和调试工具pblazeIDE,讨论PicoBlaze的编程方案和应用设计实例;列

2009-06-20 10:54:39 741

741

By Adam Taylor 到目前为止的文章中,我们已经研究了MicroZed开发板上使用以太网的数据传输问题。我们还没有涉及片上外设通信的问题:实时时钟,非易失内存以及独特的传感器。这些通信涉及到I2C或者SPI总线。

2017-01-13 11:07:11 748

748 在Adam Taylor玩转MicroZed系列的前期部分中,我们介绍了IP栈的概念。(见Adam Taylor玩转MicroZed系列第79部分:Zynq SoC以太网第3部分)接下来就是在我们的设计中使用该协议栈了。SDK开发环境允许我们创建BSP的时候包含一个轻量级的IP栈(lwIP)。

2017-01-13 11:17:11 1033

1033

By Adam Taylor 在本系列博客的前两部分中,我们研究了带有Zynq SoC PS(处理器系统)的以太网MAC(介质访问控制层),包括深入探讨了一个MAC使用范例。以太网MAC是一个基础的构建模块,它允许我们实现一个IP栈,然后因此给我们的工程创建联网条件。

2017-01-13 11:24:11 669

669 By Adam Taylor 在约束系列的最后,我们讲讲关联布局宏(RPM)的约束。RPM允许你在FPGA的布局中将DSP、FF、LUT和RAMS等资源组合在一起。与PBlocks不同,RPM并不

2017-11-10 14:49:02 748

748 By Adam Taylor 在过去一周中,我接到了很多不同人的来信,他们正在使用以Zynq为基础的开发工具。他们非常想知道怎么样去把MicroZed系列博客教程应用到他们所选择的硬件平台上。加上

2017-02-08 02:12:49 426

426

研究了相关的时序约束后,在设计中我们也不能忽视所能运用到的物理约束。一个工程师最常用的物理约束是I/O管脚的放置和与每个I/O脚相关的参数定义(标准、驱动能力等)。然而,还有其它类型的物理约束: •放置约束——定义元件位置 •布线约束——定义信号布线 •I/O脚约束——定义I/O脚位置和I/O脚参数 •配置约束——定义配置方法 按照惯例,有一些约束独立于这些组之外。Vivado套件有三个约束,并且主要用于网表: •DONT_TOUCH——用来防止

2017-02-08 02:20:11 206

206

By Adam Taylor 在先前的博客中我们研究过I/O约束,下一个合乎逻辑的步骤就是研究如何在我们的设计中用FPGA进行放置和布线约束。使用放置约束的原因如下:为了帮助实现时序,或者

2017-02-08 02:22:11 238

238 通过前面的学习,我们已经对Zynq系列的PL和PS部分已经有了相当多的了解。其中有关约束的部分我们曾经提到过但是没有重点关注。约束可以添加特定的信息到你的设计,并在综合工具和实现工具中可以得到实现

2017-02-08 03:58:43 645

645

上周的博客中我们完成了硬件的搭建,并且把硬件部分导入到SDK,见Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通过写一个简单的程序

2017-02-08 05:53:11 303

303

作者Adam P. Taylor,e2v首席系统工程师 PicoBlaze是一个紧凑型8位软核处理器,FPGA工程师可以在他们选择的赛灵思FPGA将其例化。一旦实现,该核完全位于FPGA架构

2017-02-08 06:22:11 210

210 上周的博客中我们学习了Zynq SoC的AXI DMA,我解释了怎样利用AXI DMA控制器将数据从PL搬运到PS。在本期博客中我们将学习怎样完成硬件的搭建。 首先我们要更深入的了解一下AXI

2017-02-08 08:10:39 286

286 有意思的方面,就是它能够将数据从PL(可编程逻辑)部分移动至存储器中——例如片上存储器或者DDR SDRAM,而存储器是映射到PS的地址空间上的。 作为工程师我们一直想这样做,将在Zynq PL部分实现的硬件存储器映射到PS部分的地址空间中,这是非常有用的,因为这样做可以允

2017-02-08 08:14:11 153

153

在本系列上一篇博客中,我们学习了解了使用XMD和XSDB来调试我们的应用和系统。然而为了确保我们的应用在性能上是优化的,另一个非常重要的方面就是对应用程序进行详细分析。 分析不同于调试,就分析功能

2017-02-08 09:53:00 130

130 在此系列博客的前面几期中,我们已经可以运行示例应用并获得用于分析的程序运行数据。运行分析器可以生成一个gmon.out格式的文件,它包含了分析数据。当应用程序运行自然结束或者通过SDK来终止应用程序

2017-02-08 09:56:49 180

180

在上一篇的MicroZed系列博客中,我们学习了两种与XADC进行通信的方法:Zynq SoC 的AXI或者DevC接口。通过在每个驱动程序中输出XADC的基地址,我演示了这两种XADC通信方法

2017-02-08 09:58:42 221

221 讨论,这个问题解决之后我们将回来继续学习PicoBlaze。 前面的博客中提到,有多种方式可以实现XADC与Zynq之间的交互,除了JTAG接口: 1.我们可以借助DevC接口实现XADC与PS(处理器系统)之间的直接交互,使用这种方式时,Zynq SoC的PL(可编程逻辑)部分不需要进行配置。然

2017-02-08 10:04:11 242

242 前面的几篇博客中,我们通过介绍怎样驱动CCD的一些知识了解了PicoBlaze的一些特点,同时也知道了通过Zynq PS(处理器系统)可是实现PicoBlaze的动态可重配置,我觉得在这次博客当中

2017-02-08 11:11:37 134

134 作者:Adam Taylor 在上一篇博客中我们已经知道了如何动态更新PicoBlaze的运行程序,现在我们要学习一个完成的设计应用。一个非常相关的应用就是驱动CCD(电荷耦合元件)图像传感器,因为

2017-02-08 12:31:33 144

144 正如我上周所讲,Petalinux是Xilinx针对Zynq SoC提供的Linux官方版本。为了攫取该版本最大资源,我们需要创建自己的版本。这就需要我们在Linux环境下进行开发。现在,并不是

2017-02-08 13:58:08 164

164 如果在我们的虚拟机上已经安装好了SDK,我们就得使用Linux操作系统来建立我们自己的应用程序。这通常需要对 Zynq SoC的硬件重新进行定义。 首先,我们要做的就是确保将VIVADO设计套件以及

2017-02-08 13:58:11 300

300 我必须承认这是一篇我从来不希望要写的博客。当我开始写玩转MicroZed时,我还不确定每周一篇写到52篇。达到这样的里程碑并拥有150,000的浏览量,我想回顾过去的一年在Zynq SoC上涵盖

2017-02-08 15:35:37 108

108 作者:Adam Taylor 在上一篇博客中我们了解了Zynq SoC的OCM(片上存储器) ,利用它可以实现在AMP模式下内部处理器内核之间的通信。现在我们将写一些程序代码将这个设备(OCM)利用

2017-02-08 15:38:12 606

606 作者:Adam Taylor 在最近的几篇博客中,我们花了主要精力讲解操作系统和AMP(非对称多进程处理),接下来我们希望看到Linux系统在microzed板上运行。我们目前还没有讨论

2017-02-08 15:42:12 529

529

作者:Adam Taylor 上篇博客中我们看到了在ZynqSoC的两块ARM Cortex-A9 MPCore处理器之间共享数据。我提到方法可以改进——使得更加高效——我们可以使用软件中断来进行

2017-02-08 15:47:34 222

222 介绍完操作系统后我将会在Zynq SoC上演示,我打算首先在MicroZed上实现的操作系统就是Micrium公司的uC/OSiii。这是一个硬式实时操作系统,可以点击这里下载。 该OS已经用于大量

2017-02-08 18:26:11 149

149 最近的几篇关于MicroZed系列的博客中我们介绍并了解了RTOS(实时操作系统)的概念,既然已经介绍了基本知识,是时候在MicroZed开发板上实现运行我们的第一个操作系统。我们将使

2017-02-08 18:27:06 323

323

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 在我前面的一篇博客(查看Adam Taylor玩转MicroZed系列40:MicroZed操作系统第二部分)中,大家已经见识

2017-02-08 18:27:11 202

202 我本来打算在这篇博客中继续介绍探讨运行于Zynq SoC上的操作系统。然而由于上周有人提问过一些关于Zynq SoC外设XADC,中断和alarms的问题,我认为我们应该快速的了解一下以及我们怎样

2017-02-08 18:30:02 312

312

在这期博客前面的几期,我们介绍了驱动Adafruit Neopixels设计实例的解决方案架构。我们使用Vivado方块图设计这个解决方案(具体可以查看Adam Taylor玩转MicroZed系列

2017-02-08 19:05:11 281

281

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 By Adam Taylor 我们采用基于Zynq的MicroZed板来实现Adafruit NeoPixel驱动器,前后花了

2017-02-08 19:06:11 152

152 到目前为止,我们已经从Zynq/MicroZed系列博客中看到了很多设计的例子,但是这些设计都没有使用到操作系统。裸板系统对于目前我们博客中涉及到的例子已经足够满足设计要求了,但是如果我们想使用更加

2017-02-08 19:09:11 111

111 最近我拿到了一块MicroZed I/O 扩展板卡,这个扩展板补充完善了MicroZed系统化模块(SOM)设计方法,通过分解位于MicroZed开发板背面的两个小型的I/O引脚集管上的I/O引脚

2017-02-08 20:20:29 359

359 作者是Adam Taylor,该文章发表在 第87期XCell期刊 上。Adam经常给XCell期刊投稿,在XCell日报上,他的“MicroZed Chronicles”系列文章已经发表了近30期,最近他成为了e2v科技的系统工程主管。

2019-10-06 17:09:00 3013

3013

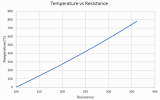

Adam Taylor's博客系列讲解在基于ARM的Zynq SoC芯片可编程逻辑上实现定点数学函数计算。 我们已经在MicroZed 系列的前期博客中学习了在PL(可编程逻辑)内实现定点运算,现在

2017-02-09 02:07:37 210

210

在上一篇博文中,我介绍了让人着迷的Adafruit NeoPixel RGB LED,并且大概描述了NeoPixel驱动设计的基本要点。(参见” 亚当泰勒玩转MicroZed连载31:系统模块驱动

2017-02-09 03:41:03 280

280

。 与我们在本博客系列中的方法一样:加上所生成的头文件作为BSP的一部分。这些头文件提供了宏和函数,我们可以用来驱动DMA 。我们将在这个示例中加入: Xscugic.h和xil_exceptions.h

2017-02-09 05:47:33 211

211

Adam Taylor's博客系列讲解基于ARM的Zynq SoC芯片可编程逻辑实现定点算法以提高性能。 这个博客系列每周发布,迄今为止已经发布了6个月,我们在Zynq SoC处理器系统(PS

2017-02-09 07:58:12 193

193 了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 957

957

我们先来了解一下上节中介绍的Zynq SoC PS/PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41 469

469

到现在为止,我们知道如何在基于Zynq SoC的系统中例化PicoBlaze 软核处理器。在这篇博客,我们将继续探索更多关于如何生成PicoBlaze 程序以及如何使用JTAG接口更新程序而不是重新编译整个设计。

2017-02-11 07:01:06 926

926 在以前发布的玩转MicroZed系列博客中,我们建立了一个基于Zynq的系统,通过使用双端口RAMS和BRAM(块RAM)控制器将两个PicoBlaze处理器核连接到Zynq的PS部分,现在我们将学习一下怎样实现更新存储在双端口RAM中的PicoBlaze处理器的程序。

2017-02-11 07:05:11 943

943

如何获得FreeRTOS演示并且在MicroZed上运行。FreeRTOS由Real Time Engineering公司开发,为小容量和极快运行速度的嵌入式系统提供帮助。

2017-02-11 10:03:12 1513

1513

在上一篇博客中成功地演示了FreeRTOS并在基于Zynq的MicroZed板上运行之后,显然我们想要能够编写我们自己的应用程序。因此,我们将首先举一个简单的例子。我们将配置Zynq SoC的XADC并且在串行链路上输出结果。

2017-02-11 10:03:13 1019

1019 Zynq SoC架构的主要优势之一就是能够通过在器件的可编程逻辑内构建外设来加快处理速度。 这是Adam Taylor 计划编写的Zynq-7000 All Programmable SoC实际操作

2018-01-12 03:50:33 824

824

经过这几年的市场磨砺,Zynq-7000 FPGA SoC器件平台在开发者中的认知度和接受度越来越高,这种“ARM处理器+可编程逻辑”的创新架构,可以帮助开发者在设计中找到高性能与灵活性的完美平衡,对此大家也心知肚明。 但是在实际的应用中,想要玩转Zynq这种“异构”平台,并非信手拈来这样简单。

2018-06-26 06:40:00 8504

8504 Adam Taylor讨论了使用Zynq®和Zynq UltraScale +™SoC开发图像处理应用程序时学到的一些技巧

2018-11-30 06:37:00 2023

2023

德赢Vwin官网

App

德赢Vwin官网

App

评论