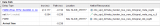

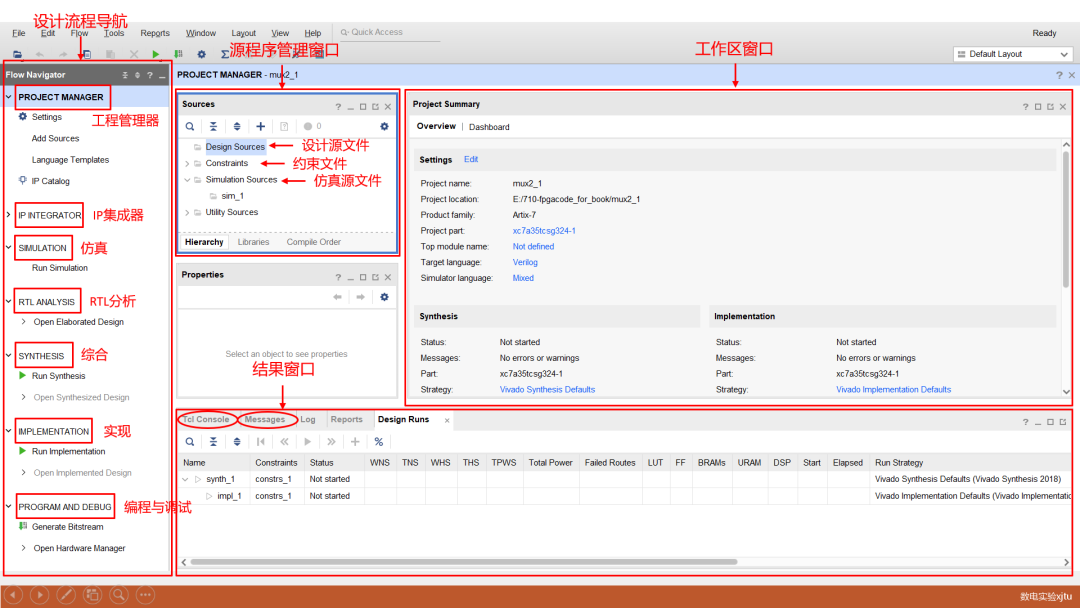

先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6408

6408 作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

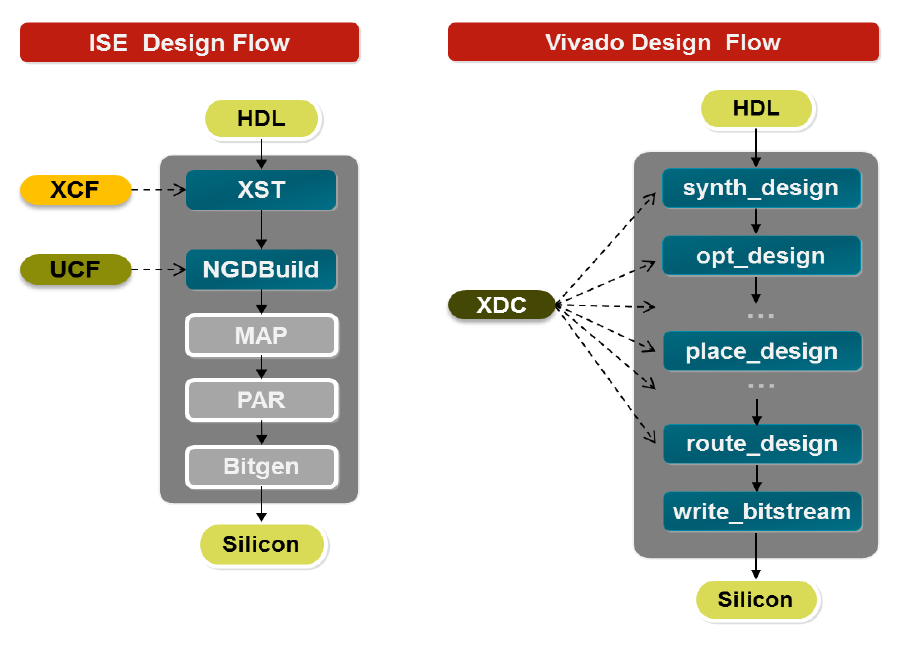

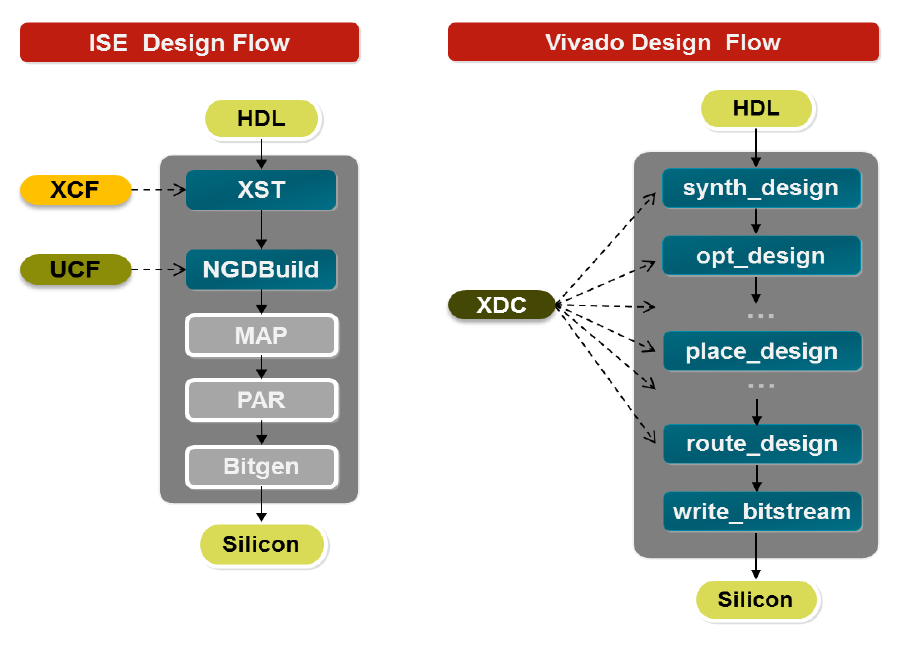

3153 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 1526

1526 FPGA 的设计流程简单来讲,就是从源代码到比特流文件的实现过程。大体上跟 IC 设计流程类似,可以分为前端设计和后端设计。

2023-04-23 09:08:49 1577

1577

/ 2327.2.2 网表对象及属性 / 2347.3 Tcl命令与网表视图的交互使用 / 2417.4 典型应用 / 2427.4.1 流程管理 / 2427.4.2 定制报告 / 2467.4.3 网表编辑 / 2497.5 其他应用 / 253参考文献 / 256

2020-10-21 18:24:48

/rtl/prims/rtl_prims.xml]信息:[Common 17-362]使用Tcl App repository from' C:/Xilinx/Vivado/2013.1/data

2018-11-27 14:30:08

嗨,我们刚刚将实施工具从Vivado 2013.1更新到2013.2。使用2013.2软件,我们无法运行实施流程。该工具在综合时崩溃,在安全IP的许可证检查中出现致命错误。请参阅随附的屏幕截图。通常

2018-11-30 11:12:34

嗨,在我的Vivado实现tcl脚本中,以下行导致错误:设置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

`Vivado 开发环境简介及设计流程`

2017-12-12 10:15:48

Vivado下显示指定路径时序报告的流程。 1.打开布局布线后的结果 2.指定到工具下的时序报告 3.选择路径的起点和终点 4.双击路径时序结果显示详细的时序情况

2021-01-15 16:57:55

分别用自己软件下的最新版本例化,时钟及管脚约束完全相同。开发流程:建立工程 -> 加入代码 -> 添加IP核 -> 初步综合 -> 添加约束 -> 综合实现1、建立工程

2021-01-08 17:07:20

AXI4 互联规范、IP-XACT IP封装元数据、工具命令语言(TCL)、Synopsys 系统约束(SDC) 以及其它有助于根据客户需求量身定制设计流程并符合业界标准的开放式环境。赛灵思构建

2019-07-18 15:40:33

AXI4 互联规范、IP-XACT IP封装元数据、工具命令语言(TCL)、Synopsys 系统约束(SDC) 以及其它有助于根据客户需求量身定制设计流程并符合业界标准的开放式环境。赛灵思构建

2023-09-06 17:55:44

嗨,我需要为Vivado 2016.3运行tcl来运行多个测试平台。如果我使用下一个:launch_simulationrun -allwait_on_run [current_run

2020-05-20 15:53:34

嗨,在网络实施期间,当我将用户ILA端口从3个端口扩展到11个端口时,会生成以下消息:[Vivado_Tcl 4-131] Power Optimization遇到异常:ERROR:[Common

2018-11-08 11:29:12

和源码,减少硬盘空间占用。 1.打开Vivado工程,在Tcl Console中输入reset_project命令(Type a Tcl command here处输入reset_project后回车

2020-08-17 08:41:25

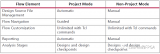

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2023-09-20 07:37:39

1.DocNav软件,里面包含了很多的设计文档,当我们画PCB了解结构的时候,可以点击这个,但是加载慢的多,可以采用迅雷下载。2.Vivado的设计流程图a) Design Checkpointi.

2016-11-09 16:08:16

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

地崩溃。完整的错误是:FATAL_ERROR:Vivado模拟器内核发现了一种无法恢复的异常情况。流程将终止。tcl脚本看起来像这样(Dinarray和Kinarray在这里缩写,但是长度为

2019-04-19 13:56:48

QuartusII 工程等内容。除了参考[3]中提到的两种“执行”TCL文件的方法,这里我提出一种相对“自动化”的方式,其实流程都是一样的只是加了“自动化”这个噱头而已。参考[3]提到一个工具,即QuartusII

2014-12-16 15:09:03

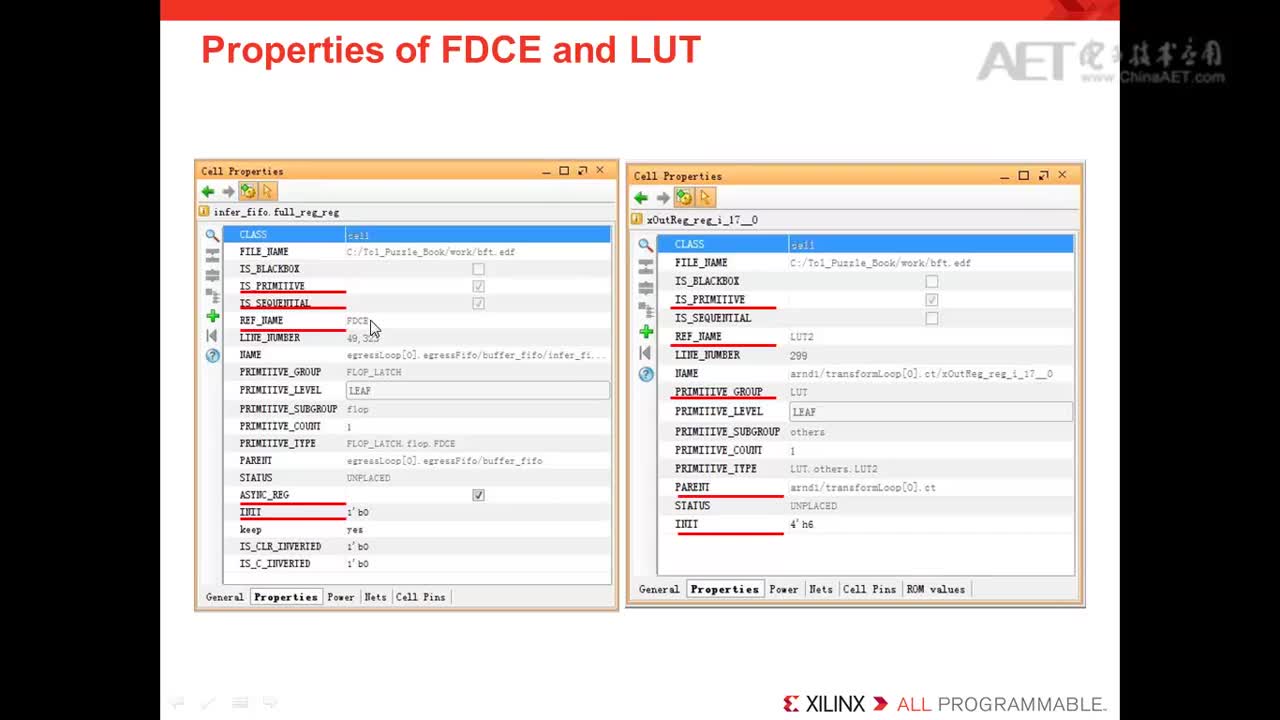

大家好,我是Vivado的新手。我想提取已实现设计的LUT名称,但我没有找到合适的tcl命令。以上来自于谷歌翻译以下为原文Hi every body,I am new with Vivado. I

2018-11-02 11:09:53

上海灵动微电子MCU开发定制流程

2021-01-05 07:18:25

STM32野火平衡小车之如何搭建之PID与MPU6050初始化

2021-10-13 06:04:02

` 今天继续与大家分享一下使用TcL脚本生成Vivado工程及编译的开发体验。创龙提供了丰富的入门教程与Demo程序,帮助我们快速熟悉FPGA开发流程。先来了解一下什么是Tcl呢?Tcl是“Tool

2020-06-07 13:59:52

我现在将vivado和modelsim做了联合仿真,用来仿真蜂鸟e203协处理器扩展实现的功能。现在的问题是:使用vivado的仿真器仿真时vivado的TCL console可以打印输出C程序中

2023-08-11 06:44:51

`例说FPGA连载33:PLL例化配置与LED之使用Tcl Console进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-17 17:50:15

`例说FPGA连载34:PLL例化配置与LED之使用TCL Scripts进行引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-23 09:34:42

在Xilinx的Vivado开发流程中,出于设计源代码保密的考虑,有时我们并不会交付源代码,而是以网表的形式进行交付。初见面,一切如故先看一个简单的example project,里面包含两个

2022-07-18 16:01:04

。Xilinx公司从ISE工具的后期开始,在工具中引入了对tcl语言的支持。在目前广泛使用的设计工具Vivado中,更是集成了tcl解释器,实现了对tcl很好的支持,同时也大大提高了编译及布局布线效率

2022-06-17 14:52:14

、书籍、源码、技术文档…(2023.07.09更新)

本篇掌握基于添加文件和IP的Vivado工程设计流程,掌握基于Tcl的Vivado工程设计流程,学习示波器的基本组成结构。获取本篇相关源

2023-08-17 19:31:54

、SW拨码开关以下是官网提供的资料链接:arty a7开发板资料Pmod DA4资料vivado安装说明board files添加基于microblaze的vivado开发流程以下是在vivado2017.4_MicroBlaze_ArtyA735t上的开发流程新建工程注:路径不要有中文名,电

2022-01-18 08:09:43

大家好,有谁知道如何更改Vivado TCL控制台窗口中的字体/字体大小?我有一个2016.1的安装,我将字体从Courier更改为Consolas并稍微缩小尺寸以增加线路上的信息密度,但我最近安装

2019-04-22 15:11:29

嗨,大家好,我是vivado工具的新手,我需要为MIG或QSFP导出.xlsx报告文件我可以使用Tcl命令自动保存报告文件吗?

2020-05-12 08:31:50

]这个tcl命令适用于Vivado 2014.4,但它在Vivado 2016.1上不起作用,有什么改变吗?或针对此问题的任何替代解决方案?谢谢。以上来自于谷歌翻译以下为原文Hello

2018-10-26 15:03:13

所有: 我正在尝试编写一个TCL脚本来重命名带有修订号的.bit文件。我需要一种方法让Vivado告诉我活动实现的名称。例如,如果我的活动实现是impl_5,我需要知道这一点,以便找到正确的.bit

2018-11-12 14:23:34

模组MAC地址定制流程是怎样的?

2021-12-29 06:01:35

玩转Vivado之Simulation特权同学,版权所有 1. 可用于Testbench分类管理的Simulation Sets关于Simulation的文件管理,ISE和Vivado的视窗大同小异

2016-01-13 12:04:16

玩转Vivado之Timing Constraints特权同学,版权所有最近在熟悉Xilinx已经推出好几年的Vivado,虽然特权同学之前已经着手玩过这个新开发工具,但只是简单的玩玩,没有深入

2016-01-11 16:55:48

在 Vivado 中定位目标。其实 Tcl 在 Vivado 中还有很多延展应用, 接下来我们就来讨论如何利用 Tcl 语言的灵活性和可扩展性,在 Vivado 中 实现定制化的 FPGA 设计流程

2023-06-28 19:34:58

我使用vivado 2014.4使用JTAG到AXI Master进行调试设计。当我运行实现时,系统有错误[Drc 23-20]规则违规(RPBF-2)IO端口驱动逻辑 - 设备端口clk驱动逻辑

2020-05-01 15:01:24

Vivado HLS设计流程是怎样的?

2021-06-17 10:33:59

一般的IC设计流程可以分为两大类:全定制和半定制,这里我换一种方式来说明。 1.1 从RTL到GDSⅡ的设计流程: 这个可以理解成半定制的设计流程,一般用来设计数字电路。 整个流程如下(左侧为流程

2017-10-20 11:38:20 25

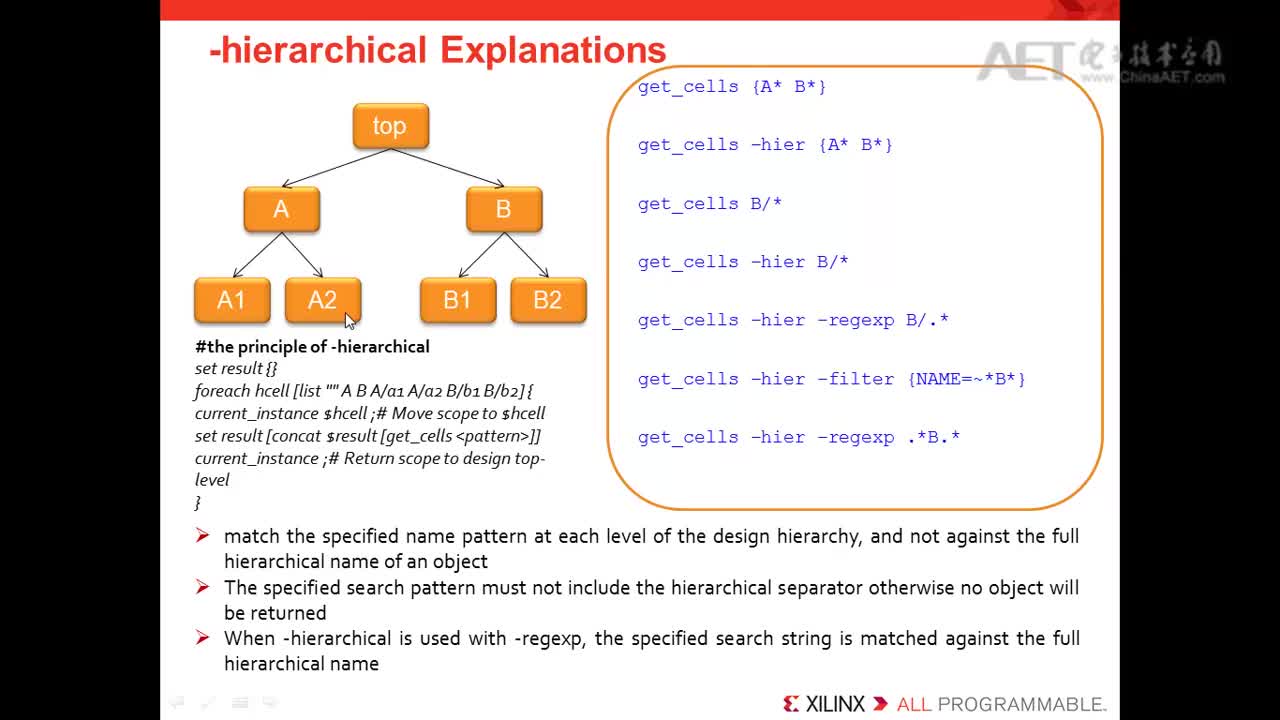

25 在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在Vivado下利用Tcl脚本对综合后的网表进行编辑。

2017-11-18 03:16:01 6899

6899

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 4675

4675

关于Tcl在Vivado中的应用文章从Tcl的基本语法和在Vivado中的应用展开,介绍了如何扩展甚至是定制FPGA设计实现流程后,引出了一个更细节的应用场景:如何利用Tcl在已完成布局布线

2017-11-18 18:26:46 4987

4987

TCL脚本语言 Tcl(Tool Command Language)是一种很通用的脚本语言,它几乎在所有的平台上都可以解释运行,而且VIVADO也提供了TCL命令行。最近发现TCL脚本貌似比GUI下操作VIVADO效率高一些,方便一些。

2018-04-11 12:09:00 9154

9154 Vivado HLS 是 Xilinx 提供的一个工具,是 Vivado Design Suite 的一部分,能把基于 C 的设计 (C、C++ 或 SystemC)转换成在 Xilinx 全可编程芯片上实现用的 RTL 设计文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 6326

6326

工具命令语言(TCL)是集成在VIVADO环境中的脚本语言。TCL是半导体工业中用于应用程序编程接口的标准语言,并由SyoSype®设计约束(SDC)使用。

2018-08-09 08:00:00 38

38 我们以8-bit 的LFSR(线性反馈移位寄存器)做一个流水灯为例,介绍Vivado的基本使用。

2018-09-25 16:16:36 14476

14476

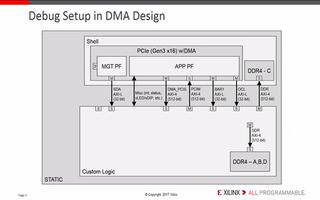

本视频将向您展示为定制逻辑设计添加调试内核的步骤。此外,它还包含一个演示,展示如何使用Vivado硬件管理器连接F1实例,如何调试在膝上型电脑/ Linux机器上运行的定制逻辑

设计。

2018-11-21 06:13:00 2932

2932

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:55:00 2340

2340 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2887

2887 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-29 06:32:00 3340

3340 了解新Vivado Lab Edition的功能和优点,并熟悉其安装和典型使用流程。

2018-11-30 06:40:00 17064

17064 物理优化是Vivado实现流程中更快时序收敛的重要组成部分。

了解如何在Vivado中应用此功能以交换运行时以获得更好的设计性能。

2018-11-23 06:06:00 3728

3728 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-30 19:24:00 4251

4251 一个完整的半定制设计流程应该是:RTL代码输入、功能仿真、逻辑综合、形式验证、时序/功耗/噪声分析,布局布线(物理综合)、版图验证。

2018-11-24 09:17:29 10793

10793 VIVADO是一个基于AMBA AXI4 互联规范、IP-XACT IP封装元数据、工具命令语言(TCL)、Synopsys 系统约束(SDC) 以及其它有助于根据客户需求量身定制设计流程并符合业界

2019-12-03 07:09:00 1896

1896 是一个基于AMBA AXI4 互联规范、IP-XACT IP封装元数据、工具命令语言(TCL)、Synopsys 系统约束(SDC) 以及其它有助于根据客户需求量身定制设计流程并符合业界标准的开放式环境。赛灵思构建的的Vivado 工具把各类可编程技术结合在一起,能够扩展多达1 亿个等效ASIC 门的设

2019-06-18 08:00:00 13

13 工程模式的关键优势在于可以通过在Vivado 中创建工程的方式管理整个设计流程,包括工程文件的位置、阶段性关键报告的生成、重要数据的输出和存储等。

2019-07-24 17:30:38 4204

4204

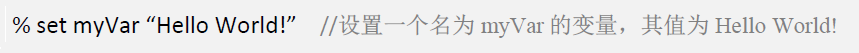

实际上Tcl的功能可以很强大,用其编写的程序也可以很复杂,但要在Vivado或大部分其它EDA工具中使用,则只需掌握其中最基本的几个部分

2019-07-24 16:52:00 3179

3179

从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。

2019-07-21 11:02:08 1367

1367 Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 2112

2112 核的使用。 BRAM是FPGA定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM

2020-12-29 15:59:39 9496

9496 Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助VivadoIDE或Tcl命令来运行。相比之下,VivadoIDE给project模式提供了更多的好处,而Tcl命令使得non-project模式运行起来更简单。

2020-10-21 10:58:07 3294

3294

带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。 1. 打开Vivado 界面 2. 打开

2020-10-26 09:45:23 3366

3366

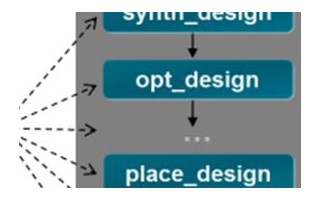

设置芯片型号,设置源文件位置,设置生成文件位置,添加设计源文件,流程命令,生成网表文件,设计分析,生成bitstream文件。其中,流程命令是指综合、优化、布局、物理优化和布线。

2020-11-20 10:56:50 1865

1865 这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。

2020-11-29 11:04:53 3879

3879

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2021-03-22 11:39:53 49

49 Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程

2021-03-25 14:39:13 28

28 【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 26

26 XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 2848

2848 在Vivado的设计流程各个阶段里,采用统一的数据模型:DCP(design checkpoint),在Vivado的设计流程里,无论是综合还是布局布线的各个阶段,工具都会生成DCP文件,每一步的执行设计输入均为上一阶段的DCP文件(综合阶段除外)。

2022-07-04 09:37:31 2787

2787 Vivado IPI (IP Integrator)提供了直观的模块化的设计方法。用户可以将Vivado IP Catalog中的IP、用户自己的RTL代码、或者用户已有的BD文件添加到IP Integrator中构成Block Design,设计更复杂的系统,如下图所示。

2022-07-15 11:39:12 1335

1335 一个完整的vivado工程往往需要占用较多的磁盘资源,少说几百M,多的甚至可能达到上G,为节省硬盘资源,可以使用Tcl命令对vivado工程进行备份,然后删除不必要的工程文件,需要时再恢复即可。

2022-08-02 15:01:06 3696

3696 vivado有project模式和non-project模式,project模式就是我们常用的方式,在vivado里面新建工程,通过GUI界面去操作;non-project模式就是纯粹通过tcl来指定vivado的流程、参数。

2022-10-17 10:09:29 1982

1982 系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,Vivado开发软件开发设计流程。话不多说,上货。

2023-02-21 09:16:44 2831

2831 Vivado是Xilinx推出的可编程逻辑设备(FPGA)软件开发工具套件,提供了许多TCL命令来简化流程和自动化开发。本文将介绍在Vivado中常用的TCL命令,并对其进行详细说明,并提供相应的操作示例。

2023-04-13 10:20:23 1551

1551 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 958

958 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

vivado的工程创建流程对于大部分初学者而言比较复杂,下面将通过这篇博客来讲解详细的vivado工程创建流程。帮助自己进行学习回顾,同时希望可以对有需要的初学者产生帮助。

2023-07-12 09:26:57 1101

1101

vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

2023-07-18 09:06:59 2137

2137

德赢Vwin官网

网站提供《Vivado设计套件Tcl命令参考指南.pdf》资料免费下载

2023-09-14 10:23:05 1

1 德赢Vwin官网

网站提供《Vivado设计套件用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-14 14:59:39 0

0 德赢Vwin官网

网站提供《Vivado Design Suite用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-13 15:26:43 0

0 德赢Vwin官网

网站提供《Vivado设计套件用户指南(设计流程概述).pdf》资料免费下载

2023-09-15 09:55:07 1

1 Vivado设计主界面,它的左边是设计流程导航窗口,是按照FPGA的设计流程设置的,只要按照导航窗口一项一项往下进行,就会完成从设计输入到最后下载到开发板上的整个设计流程。

2023-09-17 15:40:17 1494

1494

定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM。 本片

2023-12-05 15:05:02 317

317

德赢Vwin官网

App

德赢Vwin官网

App

评论