的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 2881

2881

卡,一个4.0代PCle交换机,由您选择的外部主机CPU管理。HL-205符合oCP OAM(开放式计算项目加速器模块)规范。Eachcard包含Gaudi HL-2000处理器,该处理器集成

2023-08-04 06:06:14

利用所有可能的数据通信方式-没有功能概述,也没有对用户代码进行优化转换-支持代码报告得太晚了-在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测

2021-07-10 08:00:00

不同类型的DMAHigh performance w/DMA几种DMA的总结ZYNQ中不同应用的DMA几个常用的 AXI 接口 IP 的功能(上面已经提到):AXI-DMA:实现从 PS 内存

2022-03-31 11:39:10

坛友们,谁用过Zynq7000的处理,交流一些问题!

2017-08-14 20:53:12

`本才鸟想求图像处理的范例,但求范例。`

2013-04-25 14:53:35

实验室进了台仪器,需要进行二次开发 主要是通过图像采集卡进行图像采集,然后用matlab 进行处理。目前在纠结于用labview还是C++ ,求大神给个指教,最好附一个理由

2012-05-14 11:27:40

图像采集完,之后是保存后再调用处理还是直接将摄像头连续采集的图像进行后续处理?包括ROI,灰度处理,二值法等。直接处理计算机好像处理不过来哈。处理后的图像显示花屏,求解。

2017-07-04 18:17:35

算法加速图像处理目标跟踪 产品规格芯片型号ZYNQ 7010+ADAPIVE DSP(16)ARM核CORTEX-A7 DUAL 800MHZDRAM1GBYTE(4GB MAX)EMMC1G外围

2017-06-08 10:33:07

轻松实现OpenCV C++视频处理设计到RTL代码的转换,输出硬件加速器或者直接在FPGA上实现实时视频处理功能。同时,Zynq All-programmable SOC是实现嵌入式计算机视觉

2021-07-08 08:30:00

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用加入赛灵思免费在线研讨会,了解如何在Zynq®-7000 All Programmable

2013-12-30 16:09:34

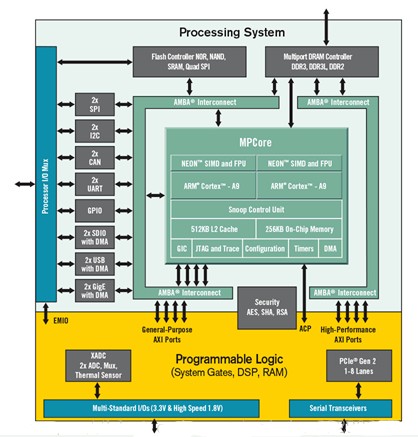

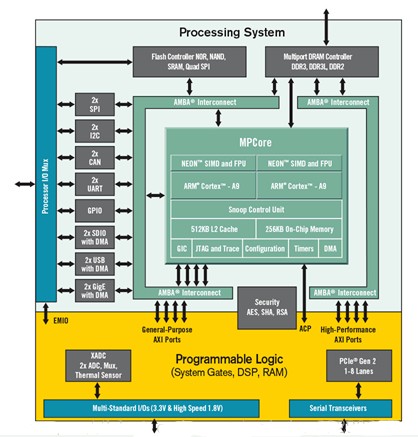

今天给大侠带来简谈Xilinx Zynq-7000嵌入式系统设计与实现,话不多说,上货。Xilinx的ZYNQ系列FPGA是二种看上去对立面的思想的融合,ARM处理器的串行执行+FPGA的并行执行

2021-11-09 06:43:27

谁会做基于labview的图像采集,灰度处理,二值化处理,还有识别的界面。求指教

2014-04-17 16:46:23

vivado可以正常使用,但是HLS总是出现图片中的错误。请问该如何解决?谢谢!

2020-08-12 01:36:19

利用所有可能的数据通信方式-没有功能概述,也没有对用户代码进行优化转换-支持代码报告得太晚了-在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测

2021-07-06 08:00:00

三、硬件加速之—使用PL加速FFT运算(Vivado)

前四期测评计划:

一、开箱报告,KV260通过网线共享PC网络

二、Zynq超强辅助-PYNQ配置,并使用XVC(Xilinx Virtual

2023-10-02 22:03:13

四、硬件加速之—使用PL加速矩阵乘法运算(Vitis HLS)

前四期测评计划:

一、开箱报告,KV260通过网线共享PC网络

二、Zynq超强辅助-PYNQ配置,并使用XVC(Xilinx

2023-10-13 20:11:51

项目名称:基于ZYNQ的图像算法加速试用计划:本人在FPGA设计有三年多的工作经验,对zynq,做过petalinux移植、非petalinux的Ubuntu移植、基于lwip的数据处理系统、ps

2019-09-18 14:17:42

Detection模块就设计的硬件加速模块,旨在利用FPGA的并行处理能力加速图像的处理效率。PL处理完的数据,将以同样的路径返回到PS部分,处理结束的消息可以通过中断方式进行告知PS部分,以同步PS与PL的工作。本系统的组成架构如下

2015-07-07 20:41:04

库函数,当中的HLS OpenCV library可应用于Zynq系列中ARM处理器的任务中。HLS OpenCV Library是可综合的图像处理库,本算法中的OpenCV功能函数被HLS OpenCV

2015-07-07 20:41:34

就是加速开发的周期。加速策略可以从两个方面考虑:(一)设计的重用和(二)抽象层次的提升。Xilinx Vivado开发套件中的IP集成功能可以实现设计的重用,而Vivado HLS工具则能够实现对高层次

2020-10-10 16:48:25

的“HLS视频库”中的函数,来进行基于HLS的视频图像处理。对于上面列出的各个库,我们同样会在后续章节中用到时候再进行介绍。

2020-10-10 16:44:42

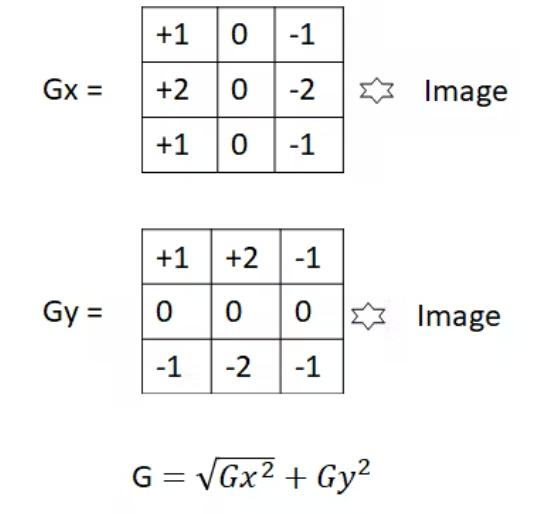

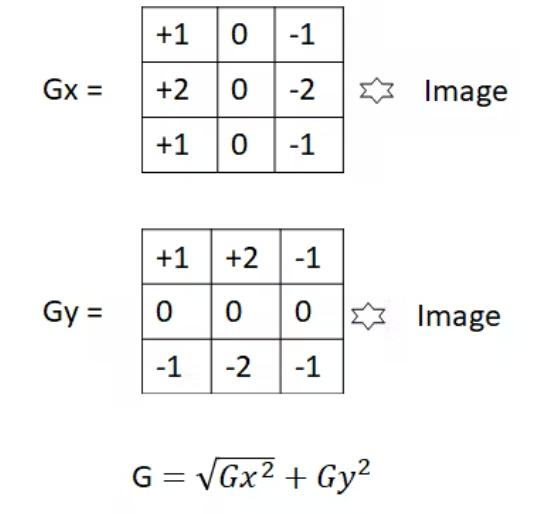

原子公众号,获取最新资料第七章OV5640摄像头Sobel边缘检测边缘检测是图像处理和计算机视觉中的基本问题,边缘检测的目的是标识数字图像中亮度变化明显的点。在本章我们将通过OV5640摄像头Sobel

2020-10-13 17:05:04

“Start of frame”是帧传输开始信号。它在一帧图像像素传输开始的时候拉高一个时钟周期。5.2实验任务本节的实验任务是使用Vivado HLS设计彩条显示的IP核,并在Vivado中

2020-10-13 16:56:47

、医学成像等方面应用越来越广。本章节我们将使用Vivado HLS生成一个图像彩条叠加的IP核,来进行基于OV5640的视频图像叠加实验。本章包括以下几个部分:88.1简介8.2实验任务8.3HLS

2020-10-13 17:06:26

实现的图像处理模块已经被综合成FPGA中的硬件模块,可以实时地处理FPGA中的视频流。Vivado HLS所综合出来的视频处理模块同样可以部署在ZYNQ器件的PL端,其常用的架构如下图所示:图

2020-10-13 16:58:56

是灰度图做了自适应二值化算法处理后的图像,可以发现图像经过自适应二值化计算出来的阈值比手动指定阈值二值化的效果更好。11.2实验任务本节的实验任务是使用Vivado HLS设计OTSU自适应二值化

2020-10-14 16:04:34

简介13.2实验任务13.3HLS设计13.4IP验证13.5下载验证13.1简介空间滤波是图像处理领域应用非常广泛的工具之一,它可以改善图像质量,包括去除高频噪声与干扰、图像平滑等。我们常见的空间滤波

2020-10-16 16:22:38

和抗干扰性,是直线检测中效果最好的算法之一。霍夫变换也可用来检测任意几何形状(比如圆),在图像处理和模式识别领域得到了广泛的应用。本章我们将在HLS中实现基于霍夫变换的直线检测。本章包括以下几个部分

2020-10-14 16:06:47

。由于直方图统计在软件中计算简单,有助于商用硬件实现,因此已经成为一种流行的实时图像处理工具。本章我们将在HLS中实现图像的直方图均衡算法。本章包括以下几个部分:1010.1简介10.2实验任务

2020-10-14 16:02:01

渐灭,并且PS可以通过AXI接口来控制呼吸灯的开关和呼吸的频率。4.3HLS设计我们在电脑中的“F:\ZYNQ\High_Level_Synthesis”目录下新建一个名为breath_led的文件夹

2020-10-10 17:01:29

手把手教你设计人工智能芯片及系统(全阶设计教程+AI芯片FPGA实现+开发板)详情链接:http://url.elecfans.com/u/c422a4bd15项目名称:基于zynq的监控视频图像

2019-10-30 17:03:31

大家好,我要做一个基于labview的图像处理的一个毕业设计,需要实现图像求反、二值化、灰度处理等功能。输入图像的功能要怎么实现呢。我现在对于整体的设计没有大概的思路。请求大神帮忙提供下思路。谢谢了。

2017-02-04 15:25:50

` ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM处理器和FPGA。ZYNQ与传统的嵌入式CPU相比,具有强大的并行处理能力。开发人员利用FPGA强大的并行处理能力,不仅

2021-01-15 17:09:15

Vivado项目中使用以下IP块。Xilinx I2S接收器 - 设置16位数据Xilinx I2S发送器 - 设置16位数据Zynq处理系统HLS IP核 - 一旦我们有初始音频链传递数据,这将

2019-07-31 05:30:00

,一路用于边缘检测处理(Sobel算法),另一路直接回显。利用Video Mixer IP核将图像叠加,通过HDMI输出原始图像或者算法处理后的图像。本案例支持CameraLink Base/Full

2020-09-17 09:48:13

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

嗨,大家好,我是新手SDK用户。我使用vivado hls来合成一个简单的图像处理算法,并构建了我现在使用sdk的硬件平台,我想使用sdk在独立模式下使用opencv应用程序在zynq fpga上

2020-05-04 17:09:19

利用labview处理图像的后面板设计,比如图像的取反,二值化等

2015-03-31 09:45:36

你好我有Zynq 7z020板,我想访问它的GPIO,但我找不到Zynq处理器文档,所以我知道如何访问Zynq GPIO?问候

2019-09-11 10:48:04

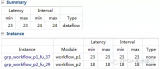

Vivado HLS 2017.4 、Xilinx SDK 2017.4。

测试板卡是基于创龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC

2023-08-24 14:44:10

Vivado HLS 2017.4 、Xilinx SDK 2017.4。测试板卡是基于创龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业

2023-01-01 23:51:35

是基于创龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。HLS 案例位于产品资料“4-软件资料\Demo

2023-08-24 14:40:42

龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。HLS 案例位于产品资料“4-软件资料\Demo\FPGA-HLS

2023-01-01 23:52:54

Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。4 matrix_demo 案例案例功能: 实现 32*32 浮点矩阵乘法运算功能

2023-01-01 23:50:04

龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。

4 matrix_demo 案例案例功能: 实现 32*32 浮点矩阵乘法

2023-08-24 14:52:17

opencv_image_filter()处理结果图 80 原始图像5.3 IP 核测试请参考本文档 HLS 开发流程说明章节,完成 IP 核测试前的准备工作。HLS 工程生成的 IP 核为

2023-01-01 23:46:20

_image_filter()处理结果图 79 opencv_image_filter()处理结果图 80 原始图像

5.3 IP 核测试请参考本文档 HLS 开发流程说明章节,完成 IP 核测试前的准备工作。HLS 工程生成

2023-08-24 14:54:01

对Xilinx可编程逻辑器件进行开发,可加速算法开发的进程,缩短产品上市时间。本次案例用到的是创龙科技的TLZ7x-EasyEVM-S开发板,它是一款基于Xilinx Zynq-7000系列XC7Z010

2021-11-11 09:38:32

。图 75 hls_image_filter()处理结果图 76 opencv_image_filter()处理结果图 77 原始图像IP核测试请参考本文档HLS开发流程说明章节,完成IP核测试前

2021-11-11 16:02:09

我在做数字图像处理的时候,二值化是边缘是断开的,我怎么帮边缘链接成封闭的。。。。。

2014-08-26 14:08:30

是video in to AXI4-Stream,接到DMA,而HLS生成的算法IP是AXI4-Stream in and out。我想把AXI-Stream信号输出接到HLS输出的IP,IP经过图像处理后

2017-01-16 09:22:25

谁有 LabVIEW Vision图像处理开发宝典。二手的卖给我。

2017-06-06 19:13:18

谁可以给个图像二值化处理的程序,通过阈值分割来实现二值化的???

2013-01-15 09:22:05

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

的请求,并驱动液晶显示器显示视频图像。本实例除了前面提到对原始图像做DDR3缓存和显示,还会在原始图像缓存到DDR3之前,另外做图像的多行缓存和平滑处理运算,获得新的平滑后的图像流,这个图像流通

2019-12-12 16:47:28

、提取和跟踪• 图像分割与拟合• 摄像头校准、立体化和3D处理• 机器学习:检测、识别 图3 OpenCV算法库开发的运动检测应用实例用HLS加速OPENCV函数 一旦完成了嵌入式视觉系统架构的分区

2014-04-21 15:49:33

对Xilinx可编程逻辑器件进行开发,可加速算法开发的进程,缩短产品上市时间。本次案例用到的是创龙科技的TLZ7x-EasyEVM-S开发板,它是一款基于Xilinx Zynq-7000系列XC7Z010

2021-11-11 15:54:48

为性能加速的空间图像处理开发FPGA协处理器快速、精确的图像数据的板上分类是现代卫星图像处理的关键部分。对于地球科学和其它应用而言,空间智能有效载荷利用智能机器

2010-04-27 08:30:31 15

15 高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

IP那节用过)。这些模块是连接到HP0的AXI4从端口,使得zynq7处理系统的数据通过AXI DMA IP核。硬件加速模块是免费的运行,并不需要驱动,只要数据被CPU推送(通常简称为处理系统或PS)。

2017-02-07 18:13:35 3135

3135 继续HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的区别 如下所示的图像处理过程,数据处理由2个滤波器构成: 默认情况下,HLS会遵循c逻辑中的先后顺序,依次

2017-02-08 03:20:41 622

622

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口

2017-02-08 03:29:11 544

544

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 1961

1961

源码是官方的2014.4 TRD工程里的,整个工程是基于zc702板子的,但手里只有块小zybo >_ 里面的硬件设计很有参考价值,最近想用FPGA加速surf算法,先在这分析下TRD工程

2017-02-08 10:12:11 458

458 大,我是否能够利用Vivado HLS完成这项要求较高的运算呢? 我开始从软件方面考虑这个转换,我开始关注软件界面。毕竟,HLS创建专用于处理硬件接口的硬件。幸好Vivado HLS支持创建AXI slave的想法,同时工作量较少。 我发现Vivado HLS编码限制相当合理。它支持大多数C + +语言

2017-02-09 02:15:11 310

310 为期 1 天的加速器开发流程介绍主要讲解如何测量系统性能、确定什么软件功能应该移至硬件,如何使用 Vivado® HLS 工具装配一款定制加速器,如何将该定制加速器添加至 Zynq SoC 设计,以及如何测量加速性能。 了解更多 »

2017-02-09 06:23:11 286

286 Missing Link Electronics 基于德国弗朗霍夫海因里希赫兹研究所 (HHI) 的加速技术提供 2015.02a 修订版 Zynq SoC 评估参考设计。支持

2017-02-09 08:17:06 212

212 在特定图像处理硬件设计中成功运用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 数年之后, Qualcomm 认识到了 HLS

2017-09-11 11:37:38 9

9 的FPGA架构使得Xilinx Zynq-7000更加强悍,应用领域更加广泛。下面将从以下方面介绍Zynq-7000的应用领域:汽车、通信系统、机器人、控制和仪器 、图像和视频处理 、医药、工业控制和许多其他领域。

2018-05-18 07:07:00 2584

2584 IP那节用过)。这些模块是连接到HP0的AXI4从端口,使得zynq7处理系统的数据通过AXI DMA IP核。硬件加速模块是免费的运行,并不需要驱动,只要数据被CPU推送(通常简称为处理系统或PS

2018-10-02 07:25:11 394

394 OPENCV(Open Source Computer Vision)被广泛的使用在计算机视觉开发上。使用Vivado HLS视频库在zynq-7000全可编程soc上加速OPENCV 应用的开发,将大大提升我们的计算机视觉开发。

2018-11-10 10:47:49 1323

1323 了解协处理的价值,Zynq-7000加速器一致性端口,使用协处理器加速器的方法以及协处理器设计实例的概述。

2018-11-30 06:15:00 3960

3960 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3026

3026 Adam Taylor讨论了使用Zynq®和Zynq UltraScale +™SoC开发图像处理应用程序时学到的一些技巧

2018-11-30 06:37:00 2023

2023 行业抓取式演示视频重点介绍了Zynq UltraScale + MPSoC装有专用处理引擎,面向图像处理,实时处理和功能安全性。

2018-11-23 06:59:00 2723

2723 RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构。Xilinx官方文档表示利用HLS进行设计可以大大加速设计进度:

2019-07-31 09:45:17 6232

6232

ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM处理器和FPGA。ZYNQ与传统的嵌入式CPU相比,具有强大的并行处理能力。开发人员利用FPGA强大的并行处理能力,不仅

2019-10-27 10:43:12 3225

3225

ThunderImage 是深维科技(DeePoly)的旗舰级产品,基于赛灵思 Alveo 加速器卡进行图像处理加速。随着目前高清图片内容越来越多,大家需要对图片的尺寸/压缩率做进一步提升,这其中比较流行的一种格式是 Google从VP8 编码提取出来的一套标准 WebP。

2020-04-30 15:58:42 2917

2917 近日,元脑生态伙伴深维科技与浪潮联合发布业内首个基于FPGA的HEIF图像处理加速方案。

2020-10-23 11:16:53 2201

2201

的是VivadoIP,用于支持Vivado IP 设计流程。后者用于Vitis应用加速流程,此时,Vitis HLS会自动推断接口,无需在代码里通过Pragma或Directive的方式定义Interface,最终会输出.xo文件。 User Control Settings还有其他的一些变化,如下表

2020-11-05 17:43:16 37066

37066 基于嵌入式Linux系统的Qt-Embedded图像处理界面开发总结(嵌入式开发培训网)-文档为基于嵌入式Linux系统的Qt-Embedded图像处理界面开发总结文档,是一份不错的参考资料,感兴趣的可以下载看看,,,,,,,,,,,,,

2021-08-04 15:23:20 7

7 Vitis Vision库是OpenCV和Vision功能的加速库,可在Vitis环境中使用,这些库的L1目录是示例设计。为了适应各种用户环境,从2020.1版本开始,Xilinx不再

2022-02-16 16:21:38 2016

2016

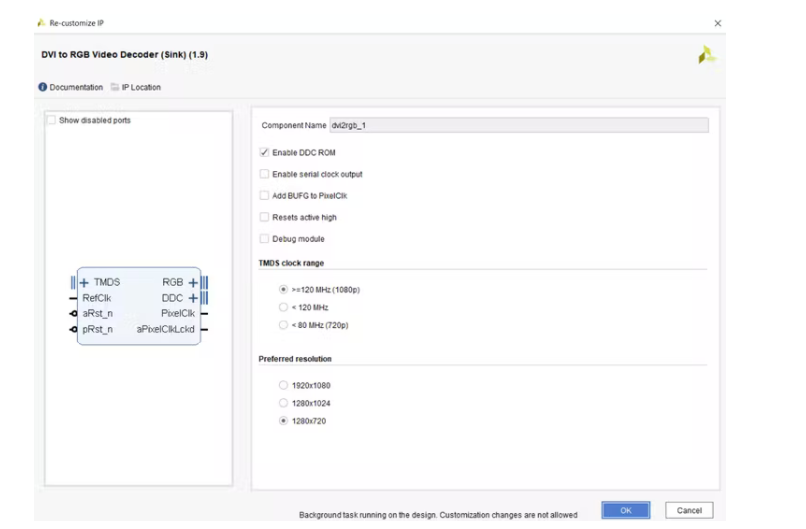

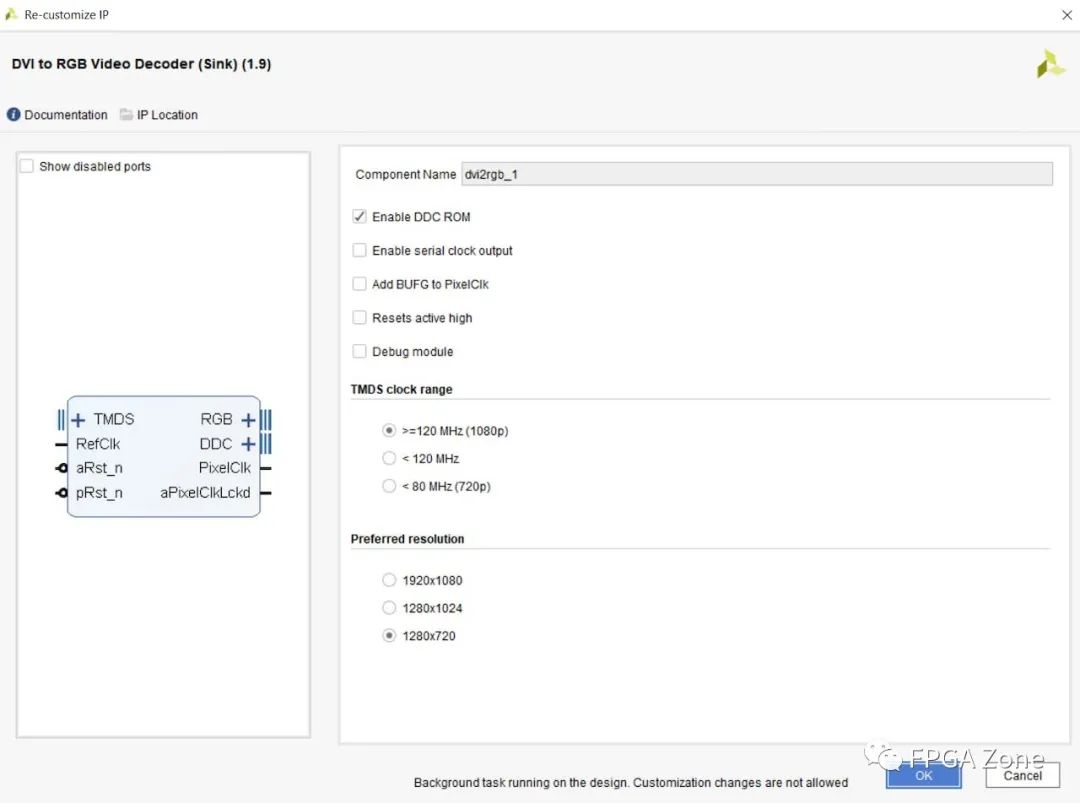

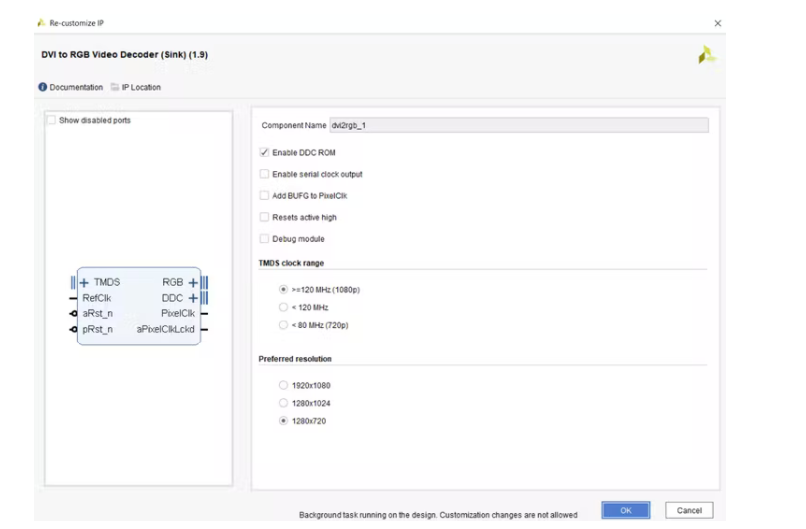

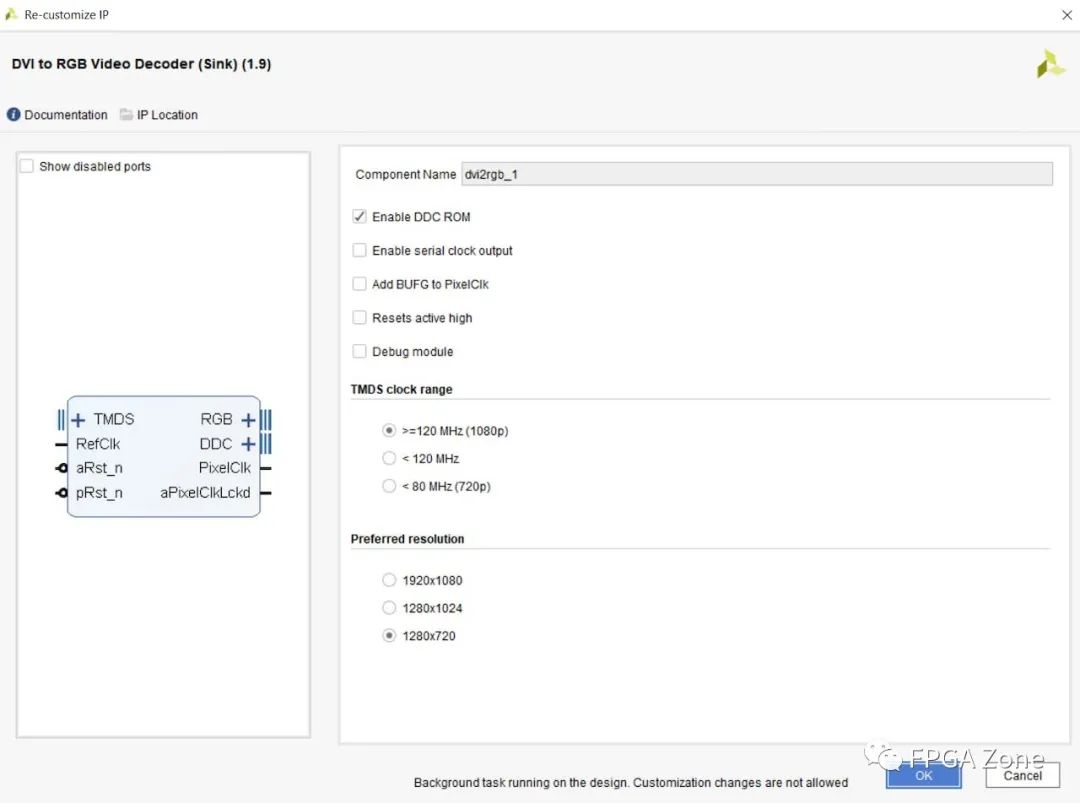

本文将介绍如何创建一个支持HDMI输入到输出的图像处理平台。这可以用作基于HLS的图像处理演示的基础。

2022-03-31 10:22:46 2400

2400

本方案利用 HLS 功能创建图像处理解决方案,在可编程逻辑中实现边缘检测 (Sobel)。

2022-05-13 17:47:17 2597

2597

Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2857

2857 这里向大家介绍使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

2022-10-11 14:21:50 1517

1517 德赢Vwin官网

网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 德赢Vwin官网

网站提供《带有PYNQ和Vitis HLS的SHA256加密加速器.zip》资料免费下载

2023-02-09 10:32:49 2

2 德赢Vwin官网

网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 1

1 最近有人问我图像处理怎么研究,怎么入门,怎么应用,我竟一时语塞。仔细想想,自己也搞了两年图像方面的研究,做个两个创新项目,发过两篇论文,也算是有点心得,于是总结总结和大家分享,希望能对大家有所帮助

2023-06-16 10:00:29 617

617 本文介绍如何搭建一个通用的图像处理平台,采用HDMI接口进行输入、输出,可用于测试基于HLS的FPGA图像处理项目。

2023-09-04 18:20:19 1050

1050

德赢Vwin官网

网站提供《CTAccel图像处理(CIP)加速器.pdf》资料免费下载

2023-09-15 14:21:36 0

0 Zynq器件将arm和FPGA结合,利用了两者各自的优势,arm可以实现灵活的控制,而FPGA部分可以实现算法加速,这大大扩展了zynq的应用。比如深度学习加速,图像处理等等。PL侧表示FPGA的逻辑部分,PS侧为arm端以及一些AXI接口控制部分,二者实际上通过AXI接口实现通信和互联。

2023-11-09 11:28:04 1460

1460

德赢Vwin官网

App

德赢Vwin官网

App

评论