对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

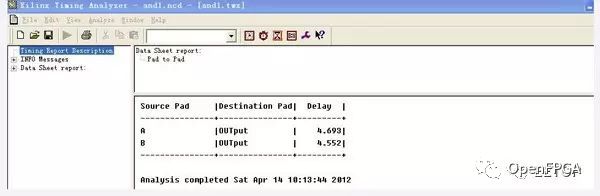

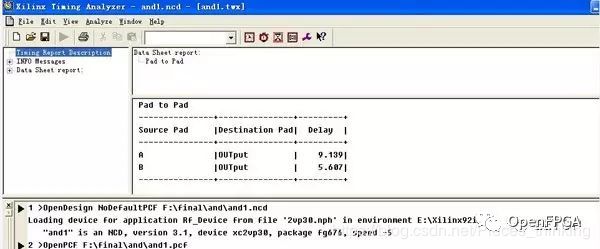

8153 信号在FPGA器件中通过逻辑单元连线时,一定存在延时。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作电压、温度等有关。

2020-03-29 10:27:00 3276

3276 影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

在数字电路中,常规介绍和解释:

什么是竞争与冒险现象:

在组合电路中

2023-11-02 17:22:20

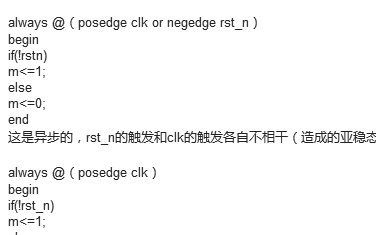

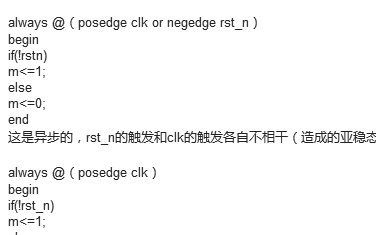

的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。03 亚稳态危害由于产生亚稳态后,寄存器 Q 端输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值。在信号传输中产生亚稳态

2020-10-22 11:42:16

冒险往往会影响到逻辑电路的稳定性。时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。如何处理毛刺

2018-08-01 09:53:36

竞争冒险:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象,称为竞争冒险。那么 FPGA 产生竞争冒险的原因是什么呢? 信号在 FPGA 器件内部通过

2024-02-21 16:26:56

用FPGA做DDS,请教这种由于输出信号的各位跳变时间有差异导致的毛刺怎么解决?

2017-05-17 09:57:54

有先有后,这种时差引起的现象称为竞争(Race)。竞争的结果将很可能导致冒险(Hazard)发生(例如产生毛刺),造成错误的后果,并影响系统的工作。组合逻辑电路的冒险仅在信号状态改变的时刻出现毛刺,这种冒险

2014-06-30 15:45:20

,我们称之为“毛刺”。如果一个组合逻辑电路中有毛刺出现,就说明该电路存在“冒险”。(特权同学,版权所有)下面我们可以列举一个简单例子来看看毛刺现象是如何产生和消除的。如图5.14所示,这里在图5.10

2015-07-08 10:38:02

电路输出发生瞬时错误的现象叫做冒险。(也就是由于竞争产生的毛刺叫做冒险)

判断方法:

1)代数法:如果布尔式中有相反的信号则很有可能产生竞争和冒险现象;

2)图形法:有两个相切的卡诺圈并且相切处没有被

2023-11-03 10:39:27

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

FPGA 20 位总线输入经过164245转换后,高低电平变化时有时有毛刺,能达到4.6V。不知会不会烧坏FPGA。也没找到技术支持电话。哪位大哥哥帮帮我。谢谢了

2013-07-15 15:01:45

FPGA的IO口输出20M频率方波信号,上升沿和下降沿有毛刺怎么办?串联磁珠或者匹配电阻有效吗?同事想的办法是在后面加个高频的运放组成的射极跟随器。我认为毛刺会通过射极跟随器走到下一级电路。不知道怎么解决好?

2019-01-21 06:35:23

在FPGA的设计中,毛刺现象是长期困扰电子设计工程师的设计问题之一,是影响工程师设计效率和数字系统设计有效性和可靠性的主要因素。由于信号在FPGA的内部走线和通过逻辑单元时造成的延迟,在多路信号变化

2012-09-06 14:37:54

,提高电路的稳定性,而且其先进的开发工具使整个系统的设计调试周期大大缩短。而在FPGA设计中也存在一些难点问题,本文将主要分析、讨论毛刺信号的产生原因及消除毛刺的方法。通过综合运用这些方法,可以最大

2009-04-21 16:47:58

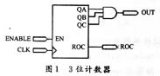

摘 要:以现场可编程门阵列(以下简称FPGA)在设计中由于其内部构成,容易引起竞争问题。以我们在实验教学中的应用与实践为主线,详细介绍了消除竞争冒险的各种方法。关键词:现场可编程

2009-04-21 16:44:44

下面对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用

2021-06-30 07:00:00

FPGA连续信号给到AD9736,但是总会有周期毛刺出现,如图

逻辑分析仪检查FPGA的输出信号,没有该毛刺出现

2023-12-18 06:16:33

FPGA连续信号给到AD9736,但是总会有周期毛刺出现,如图逻辑分析仪检查FPGA的输出信号,没有该毛刺出现

2018-09-10 11:13:52

数字逻辑电路中的两个基本门电路,A、B经过不同的传输途径达到,那么在设计时往往难于准确知道A、B到达次序的先后,以及它们在上升时间和下降时间上的细微差异。因此,我们只能说只要存在竞争现象,输出就有可能

2023-02-21 15:35:38

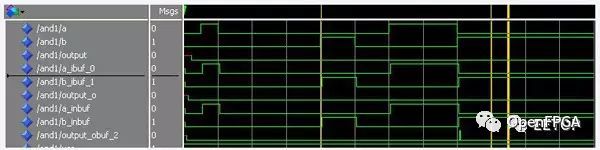

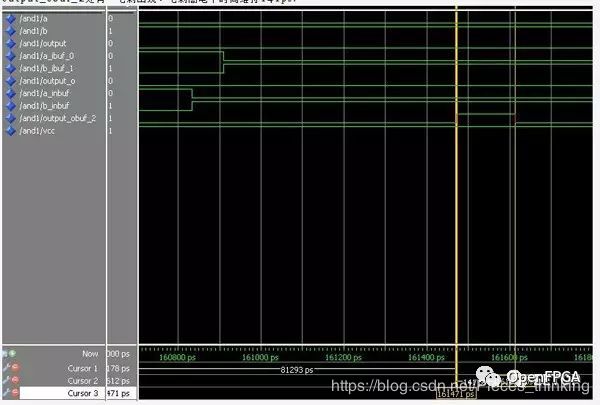

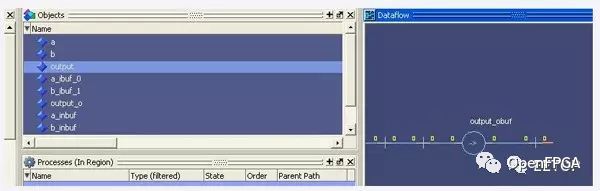

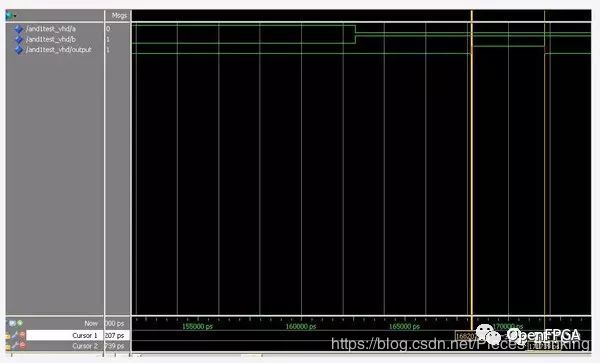

,因此毛刺现象在PLD、FPGA设计中尤为突出) 图2给出了一个逻辑冒险的例子,从图3的仿真波形可以看出,"A、B、C、D"四个输入信号经过布线延时以后,高低电平变换不是同时发生

2012-02-10 09:50:36

fpga的gnd)。现在能正常控制电机。但是只要电机驱动一通电,用逻辑分析仪看fpga输出的自定义调试信号时 发现有大量高频毛刺。为此在fpga和电机驱动模块之间加了56v二极管。现在电机驱动通电但是电机不

2017-09-15 17:46:04

我用FPGA控制ad7865采集数据时,采集到的正弦波数据波形出现一些毛刺现象,请问该怎么解决,谢谢帮忙!

2014-06-07 00:00:30

错位现象得到明显好转。示波器探头测量信号时相当于并联上一个pF级的电容,也能够一定程度上起到滤波的效果,因此可以断定同步信号的毛刺影响了数据的采集。其中一个同步信号如图1,两个有效高脉冲之间有很多毛刺

2019-06-04 05:00:17

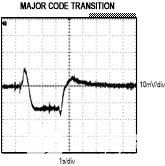

下图是从AD5764芯片手册中截取的。

下图除了0 - 2.0us 是毛刺,其余部分都是稳定在了-6mV 。

我的问题是:我用示波器测量我的波形的时候,到处都是大约20mV的毛刺。没有像这么稳定的 -6mV 。请问这是什么原因?

另外我想知道下图您是用示波器侧的吗,您的电路是什么样的呢?

2023-12-12 07:16:26

我使用AD5781的评估板,输出10Hz 100mV的正弦波,我读入AD7768-1的数据再通过AD5781输出,我AD7768-1采集的数据中没有毛刺,但我AD5781输出的数据经过运放

2023-12-07 06:04:30

最近使用AD768的过程中发现,在数据转换过程中伴随时钟信号的下降沿有一个4mV左右的毛刺,同时注意到fpga到da的数据线上也有这个现象,两者之间是通过74alvc164245完成电平转换的,现在想办法去掉这个毛刺,请问有些什么好的建议!

2018-12-07 09:41:12

最近使用AD768的过程中发现,在数据转换过程中伴随时钟信号的下降沿有一个4mV左右的毛刺,同时注意到fpga到da的数据线上也有这个现象,两者之间是通过74alvc164245完成电平转换的,现在想办法去掉这个毛刺,请问有些什么好的建议!

2023-12-22 06:59:24

在测试AD9117时,用FPGA给DAC一个正弦波的数字信号,在输出端发现有脉冲毛刺出现,在示波器上有毛刺的余晖。在频谱上会有底噪抖动,我认为是毛刺造成,请问是否知道关于这个毛刺生成的有关原因

2023-12-13 06:19:05

在测试AD9117时,用FPGA给DAC一个正弦波的数字信号,在输出端发现有脉冲毛刺出现,在示波器上有毛刺的余晖。在频谱上会有底噪抖动,我认为是毛刺造成,请问是否知道关于这个毛刺生成的有关原因

2019-01-17 08:19:07

前端电路输入标准的正弦波,AD9681采集到的数据通过串行LVDS发送的到FPGA,这是FPGA采集到的波形:上边沿下边沿出现了规则的毛刺。前期排查:1、将拜伦变压器后端的差分模拟信号飞线到另一

2019-01-18 16:33:32

前端电路输入标准的正弦波,AD9681采集到的数据通过串行LVDS发送的到FPGA,这是FPGA采集到的波形:上边沿下边沿出现了规则的毛刺。

前期排查:

1、将拜伦变压器后端的差分模拟信号飞

2023-12-12 06:00:44

我们目前在做一个超宽带的项目,信号带宽528MHz发端送给射频的信号采样率为2.112Gbps,由于是I Q两路送入射频,所以我们的硬件板上有两片AD9739,在FPGA内部我们的数据速率

2018-12-11 11:33:51

黄色为Vtune电压,蓝色为MUXOUT锁定指示。如图所示,黄色尖状毛刺出现时,未锁定。请问是,ADF4153A器件原因造成的随机性不锁定现象嘛?并且会在不锁定的时刻出现毛刺。

2018-08-03 07:53:20

各位大神: 我在使用ADIS16209进行静态测试的时候,输出的双轴加速度计输出会出现毛刺,具体现象如图所示,请各位大神帮忙分析原因。

2018-12-19 09:27:03

用LSM6DSM芯片,采集三轴加速度信号,出现如下的毛刺现象电路原理图如下请问大家遇到过类此问题嘛,怎么解决的!谢谢!!

2019-04-02 19:39:40

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。 如果布尔式中有相反的信号则可能产生竞争和冒险现象。 解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

2019-08-02 11:57:35

,但是将程序下载到电路板上发现输出端的信号为:

这个图是通过示波器直接测芯片DAC0输出端的波形,而且该输出端未接任何东西,2.5v电压正常,但是会出现周期性的毛刺,毛刺大致值为180mV左右

2024-01-12 07:44:18

控制fpga进行,该阶跃信号连接到fpga的某个引脚。发现在PCI-6733输出的波形在时钟的边沿有毛刺。请问毛刺是什么原因呀?是时钟的质量不够好吗?还是接地有什么问题?

2020-05-17 09:24:09

如何解决电路中短时脉冲波形失真的所谓“毛刺”现象?并提出相应的解决办法。

2021-04-08 06:25:08

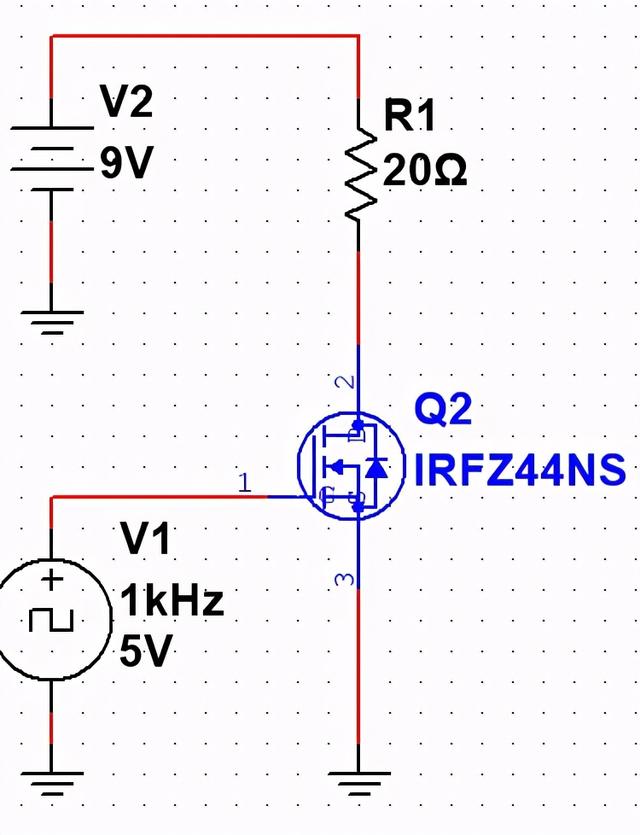

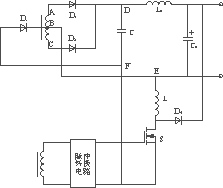

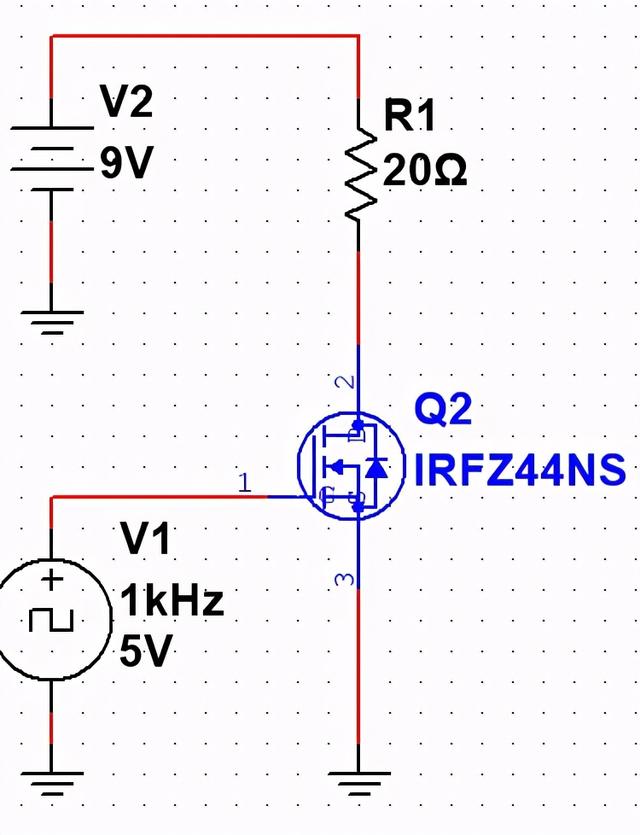

毛刺现象是我们每一个电子爱好者避之唯恐不及的,今天我们来学习一个毛刺现象以及如何规避它,进而掌握电感升压的原理。简单场管开关电路让我们从一个简单的电路开始,该电路使用一个 N 沟道场效应管控制 20

2021-12-30 07:09:17

用FPGA做数字频率计 捕捉上升沿低频部分的方波是靠比较器产生的 LM339KHz级别还好Hz级的信号 频率越低 示波器拉开看 产生的信号上升沿里面全是毛刺低频部分 使用LM339的探测范围要求

2016-06-28 18:31:31

小弟今日碰到如下难题,请教站内高手帮忙解析一下,跪谢200mv(可能本身就有毛刺)的工频信号经过下图电路积分移相后,输出的波形有很多毛刺,不能达到测试要求,试过好多方法对积分移

2010-02-09 16:42:25

小弟今日碰到如下难题,请教站内高手帮忙解析一下,跪谢200mv(可能本身就有毛刺)的工频信号经过下图电路积分移相后,输出的波形有很多毛刺,不能达到测试要求,试过好多方法对积分移

2010-02-09 16:44:09

小弟今日碰到如下难题,请教站内高手帮忙解析一下,跪谢200mv(可能本身就有毛刺)的工频信号经过下图电路积分移相后,输出的波形有很多毛刺,不能达到测试要求,试过好多方法对积分移

2010-02-09 16:39:56

,就说明该电路存在“冒险”。(与分立元件不同,由于 PLD 内部不存在寄生电容电感,这些毛刺将被完整的保留并向下一级传递,因此毛刺现象在 PLD、FPGA 设计中尤为突出)。毛刺的累加,将会影响整个

2023-05-30 17:15:28

的看到毛刺现象(图3-数字处理过程中已减去直流偏置),数字量采样时 采样了4次,去掉最大和最小值,在进行平均的;如果仅采样一次,那毛刺更大。一开始怀疑是3.3V电压源的问题(产生直流偏置,和对AD口进行

2018-10-08 17:02:49

想测频10-300kHz,信号跳变的时候毛刺很多,硬件定型了,只能用fpga滤波,谁有比较好的解决方法,能有现成代码最好了,谢谢啦

2013-11-29 23:08:31

)。17.FPGA 设计中如何实现同步时序电路的延时?首先说说异步电路的延时实现:异步电路一半是通过加 buffer、两级与非门等(我还没用过所以也不是很清楚),但这是不适合同步电路实现延时的。在同步电路中,对于

2019-08-16 08:30:00

最新的化学去毛刺工艺

一提到去毛刺,很多人马上联想到的是洗磨。洗磨是现在运用最为普遍的一种去毛

2009-03-20 13:39:22 1055

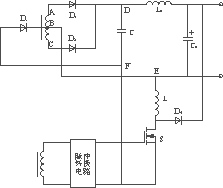

1055 高频整流电路中的新型电压毛刺无损吸收电路

0 引言

电压毛刺是高频变换器研制和生产过程中的棘手问题,处理得不好会带来许多的

2009-07-06 08:27:55 1134

1134

电路的谐振现象分析

谐振现象是交流电路中产生的一种特殊现象,对谐振现象的研究有着重要的意义。在实

2009-07-27 08:11:02 10045

10045

组合逻辑中的竞争与冒险及毛刺的处理方法 在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的(冗余)消去项,但是不

2011-01-24 18:12:53 0

0 本文从FPGA的原理结构的角度探讨了产生毛刺的原因及产生的条件,在此基础上,总结了多种不同的消除方法,在最后结合具体的应用对解决方案进行深入的分析。

2011-08-03 11:48:15 1931

1931

和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

2017-02-11 03:59:38 1626

1626

的滤波电路。 SDA 或 SCL 线路上的毛刺会导致信号线路的瞬间错误触发。 SDA 上的毛刺会导致错误 START 条件或错误 STOP 条件的识别,从而破坏总线协议。 SCL 上的毛刺会导致错误的数据传输,也会破坏总线协议。

2018-06-29 14:00:00 17133

17133 毛刺现象在FPGA设计中非常普遍, 而毛刺的出现往往导致系统结果的错误。本文从FPGA的原理结构的角度深入探讨了毛刺产生的原因及产生的条件,总结了多种不同的解决方法,并结合具体的应用对解决方案进行

2017-11-22 14:24:54 8414

8414 铸铁去毛刺,切冒口,切焊口。铝件去毛刺,发动机壳去毛刺

2017-11-24 14:40:53 3

3 数字电路设计人员经常面临的挑战之一是要消除所设计电路的毛刺信号。为此,通常需要确保数据锁存期间具有足够的建立时间以及保持时间。 毛刺是不能在整个时钟周期内都保持有效的信号。带毛刺的信号如果馈送

2018-03-27 18:46:00 1

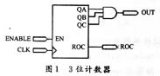

1 通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

2018-06-23 08:49:00 1613

1613

大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA学习中,亚稳态现象。 说起亚稳态,首先我们先来了解一下什么叫做亚稳态。亚稳态现象:信号在无关信号或者异步时钟域之间传输时导致数字器件失效的一种

2018-06-22 14:49:49 3222

3222

高压包的高压卡簧与高压线连接焊点有毛刺,毛刺尖端会产生放电现象,若放电,会将高压帽橡胶烧老化。所以说如果家里或下雨季节,家里比较潮湿,电视机高压卡簧与高压线连接焊点的毛刺会发电,导致电视高压包损坏。

2019-01-22 17:04:46 31358

31358 毛刺的英文名是veining,一般金属件表面出现余屑和表面极细小的显微金属颗粒,这些被称为毛刺。毛刺越多,其质量标准越低。所以企业生产产品的时候都会想办法尽量减少出现的毛刺。

2019-04-29 16:03:57 11433

11433 去毛刺,就是去除在零件面与面相交处所形成的刺状物或飞边。毛刺的危害性尤为明显, 逐渐引起人们的普遍重视, 并开始对毛刺的生成机理及去除方法进行研究。

2019-05-22 11:24:14 8338

8338 毛刺其实是一种金属铸造、铣切、电镀术语。毛刺的英文名是veining,一般金属件表面出现余屑和表面极细小的显微金属颗粒,这些被称为毛刺。毛刺越多,其质量标准越低。所以企业生产产品的时候都会想办法尽量减少出现的毛刺。

2019-05-22 14:24:56 8647

8647 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 323

323 决这个问题,爱奇艺深度学习平台团队经过多个阶段的优化实践,最后对 TF Serving 和 TensorFlow 的源码进行深入优化,将模型热更新时的毛刺现象解决,本文将分享 TensorFlow

2020-12-17 16:48:47 3930

3930 LTC6994-1LTC1541演示电路-带毛刺抑制器的高精度、功耗、过压检测器

2021-06-03 08:18:16 9

9 毛刺现象是我们每一个电子爱好者避之唯恐不及的,今天我们来学习一个毛刺现象以及如何规避它,进而掌握电感升压的原理。简单场管开关电路让我们从一个简单的电路开始,该电路使用一个 N 沟道场效应管控制 20

2022-01-10 10:53:27 4

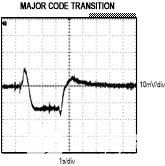

4 当DAC输出模拟值发生变化时,在DAC输出端观察到动态现象,表现为毛刺,如图1所示。该毛刺能量定义为电压曲线下的面积与示波器上捕获的时间图的关系。该毛刺能量的单位是nV × s。

2022-12-15 11:53:04 1858

1858

在电源电压超过±5V的R-2R DAC设计中,DAC的主要进位转换期间可能会出现较大的电压毛刺(高达1.5V)。这些毛刺会传播到输出缓冲放大器,并出现在输出端。控制顶部 (VREF+) 和底部 (VREF-) 单刀双掷开关(S0 至 SN)的电平转换器的回转会导致毛刺(图 1)。

2023-02-24 17:10:06 1767

1767

示波器波形毛刺通常是由信号本身带来的噪声或者示波器本身的问题造成的。下面是一些减少示波器波形毛刺的方法

2023-05-02 09:55:00 15997

15997 在金属制品加工中不可避免的出现各种毛刺,这些毛刺对工件质量产生严重的影响,因此去毛刺成为后续加工中一个必不可少的工序。以前大多企业通过人工去毛刺,但现在机械手装配速科德Kasite浮动去毛刺主轴,将去毛刺工艺提高到一个新的水平。

2022-06-14 16:52:29 551

551

毛刺危害大,目前去毛刺有机器人去毛刺、人工去毛刺、化学去毛刺、高温去毛刺、滚磨去毛刺、研磨去毛刺、冲模去毛刺等多种方法。其中机器人浮动去毛刺能力稳定,生产效率高,易于实现自动化数控,对于精度要求高或造型复杂的零件毛刺也能轻松去除。

2022-11-29 10:20:59 417

417

当锡膏焊接完成后,我们可能会发现,锡膏的边缘并不平整,表面有毛刺或玷污,遇到这样的问题该怎么办?下面锡膏厂家来为大家讲解一下:首先我们来分析下造成这种现象的根源:一、PCB板焊后成型模糊:锡膏边缘

2023-05-29 09:35:30 464

464

毛刺现象是我们每一个电子爱好者避之唯恐不及的,今天我们来学习一个毛刺现象以及如何规避它,进而掌握电感升压的原理。

2023-08-15 14:53:20 2103

2103

浮动主轴压铸铝去毛刺技术是一种高效、精准的去毛刺方法,通过旋转切割工具和主轴相对运动来去除压铸铝制品表面的毛刺。该技术具有减少加工时间和成本、提高加工精度、适用于不同形状和材料的工件等优点。浮动主轴

2023-09-18 14:46:32 366

366

机械臂去毛刺主轴是一种高效的自动化去毛刺技术,广泛应用于金属加工和汽车零部件加工等领域。通过高速旋转的主轴和精确控制的机械臂,实现高精度、高效率、高质量的自动化去毛刺作业,提高生产效率和产品质量,降低人工操作风险,提高作业安全性。

2023-11-28 13:41:19 179

179

什么是毛刺?毛刺的大小和方向 如何测量毛刺的尺寸?如何检查已去除的毛刺? 毛刺是指由于加工工艺或其他原因产生的金属表面上的不平整区域或小尖刺。毛刺通常形成于金属的切削或冲压过程中,可能会影响产品

2023-12-07 14:24:36 1284

1284 如何最小化毛刺尺寸?如何控制毛刺方向? 为了得到高质量的产品或工艺品,我们通常需要把毛刺的尺寸最小化,并控制其方向。毛刺会影响制品的外观质量、功能性能以及使用寿命。本文将介绍毛刺的形成原因、影响因素

2023-12-07 14:24:39 213

213 PCB钻孔毛刺产生的原因及毛刺的危害 PCB(Printed Circuit Board)是一种非常重要的电子组件,被广泛应用于各种电子设备中。在PCB的生产过程中,钻孔是一个非常关键的步骤,用于

2023-12-07 14:24:41 1345

1345 什么是紧固件毛刺呢?紧固件毛刺是怎么样形成的呢?要如何很好的去除这种毛刺呢? 紧固件毛刺是指在紧固件(如螺钉、螺帽、螺栓等)的表面形成的一层或多层细小的突起。这些毛刺通常是由于制造过程中的不完

2023-12-07 14:24:44 287

287 冲裁加工时总是会产生毛刺,很难消除掉,因此,经常在加工后进行压毛刺来消除毛刺。鉴于分型面的问题,最近使用去毛刺的方式有增加的趋势.

2023-12-12 14:17:08 240

240

信号毛刺是指信号中出现的突然幅度变化,通常表现为信号波形上的尖峰或震荡。这种现象可能会导致电子设备的不稳定性,甚至影响设备的正常运行。为了准确观察信号毛刺并找出其原因,使用示波器是一种常见的方法。本文将介绍如何使用示波器观察信号毛刺,并给出一些常见的处理方法。

2023-12-26 15:04:48 330

330

德赢Vwin官网

App

德赢Vwin官网

App

评论