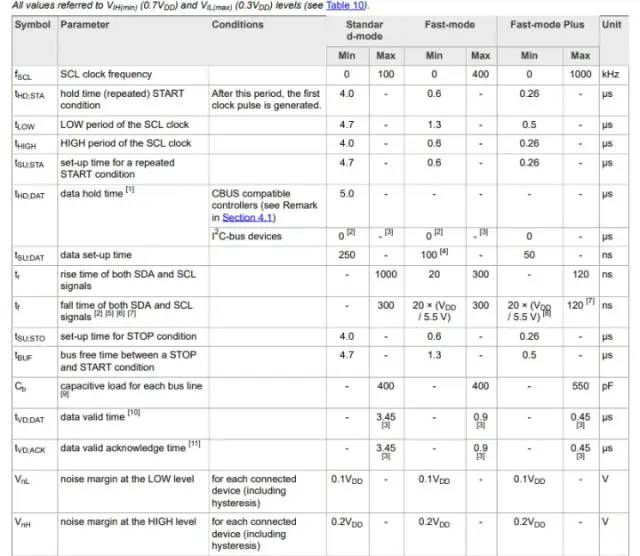

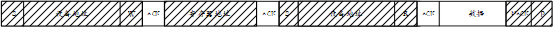

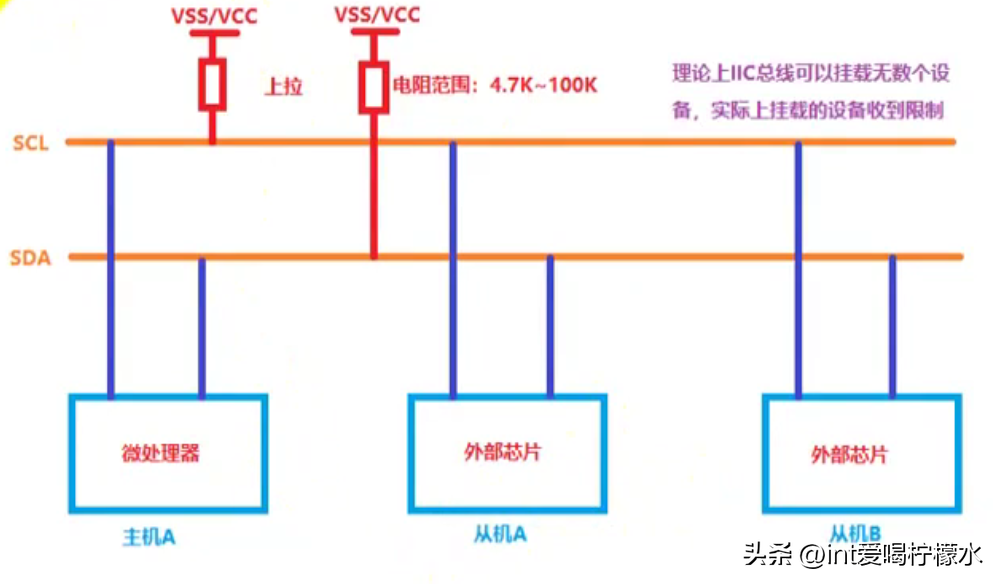

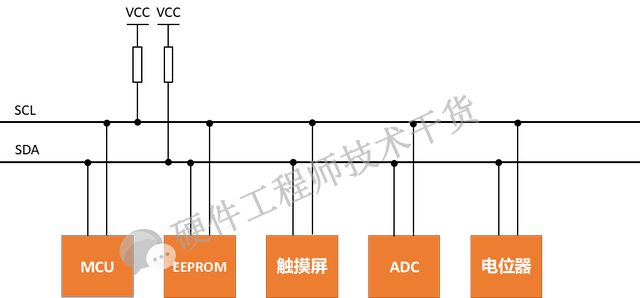

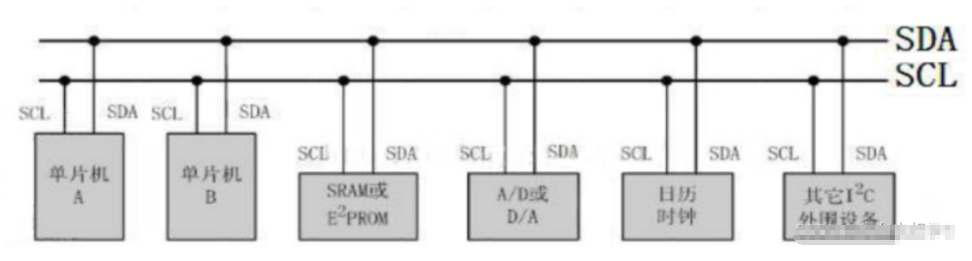

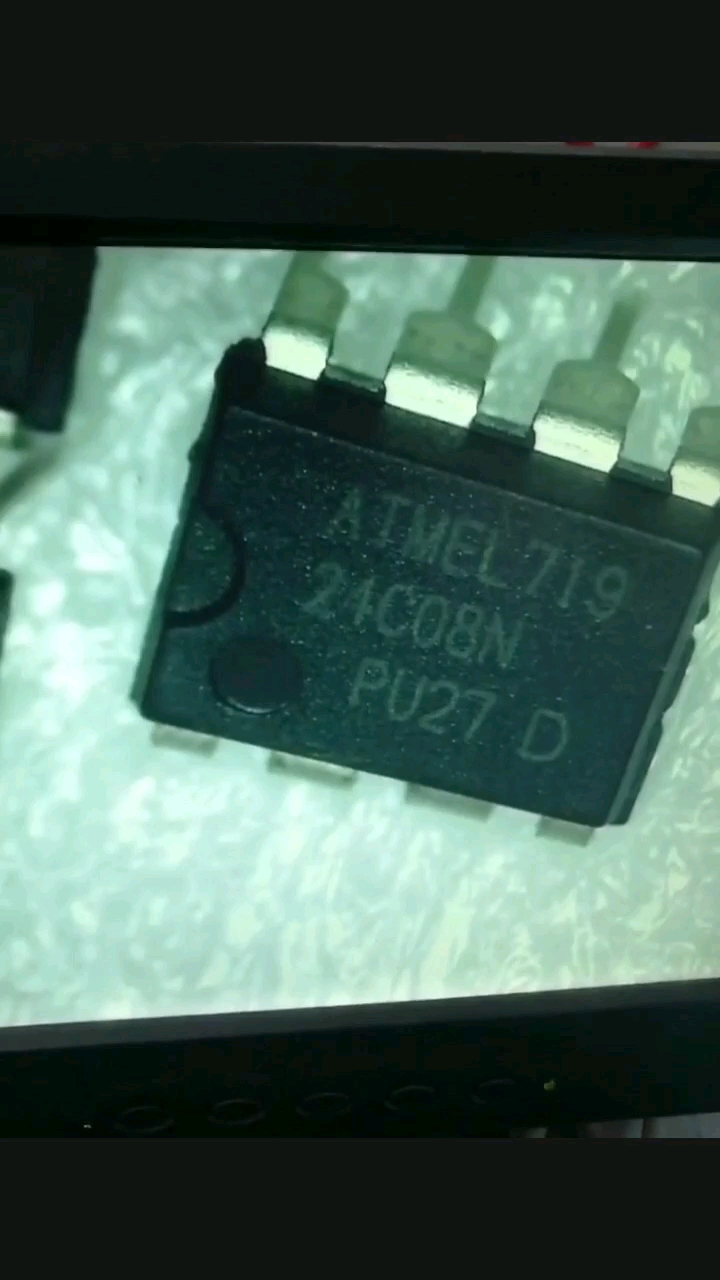

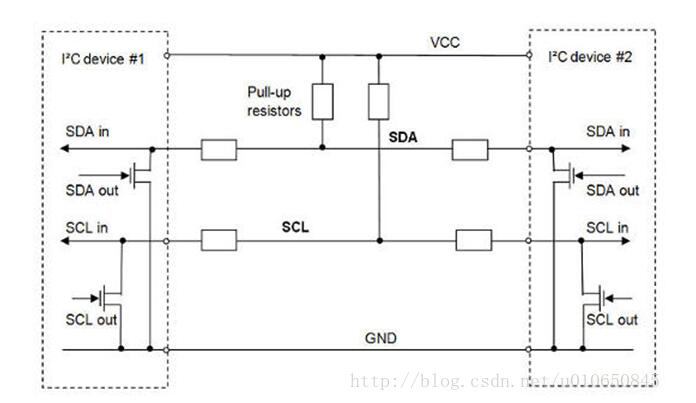

IIC是飞利浦提出的一种通信总线结构,其硬件架构比较简单,仅包含SCL和SDA两条线。根据最新的IIC总线标准,IIC总线包含Standard-mode(100kbit/s)、Fast-mode(400kbit/s)、Fast-mode Plus(1Mbit/s)、High-speed mode(3.4Mbit/s)以及Ultra-Fast-mode(5Mbit/s)5种不同速率的模式,图一给出了前三种模式的相关参数。

图1 IIC总线几种模式的相关参数

根据图1,可以提出以下几个问题:

1、几种不同模式的硬件架构有何区别?

2、不同模式所定义的速率上限是怎么来的?大于规定速率的话会怎样?

3、总线电容400pf的要求是怎么确定的,为什么Fast-mode Plus速率更快,

总线电容却可以更大?

4、为什么会有上升、下降时间的限制?Fast-mode和Fast-mode Plus的下降

时间为什么还有最小值的限制?

5、建立、保持时间为什么需要限制?

另外,关于IIC总线,还有一些问题需要记录:

- IIC总线的通信协议?

- 什么是时钟延展?

- IIC总线的是怎么仲裁的?

本文将针对以上问题进行讨论。

几种不同模式的硬件架构有何区别?

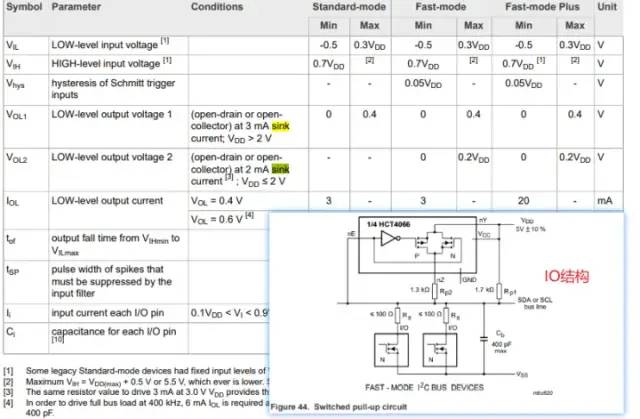

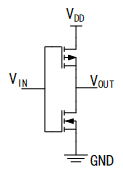

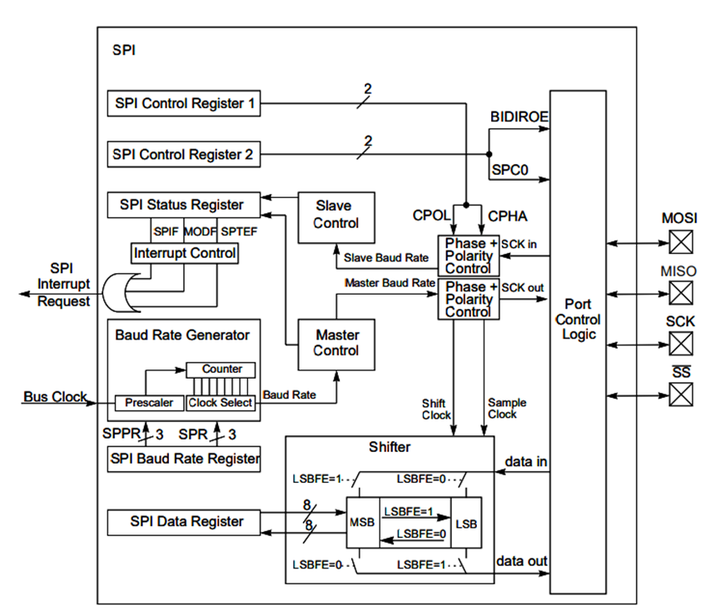

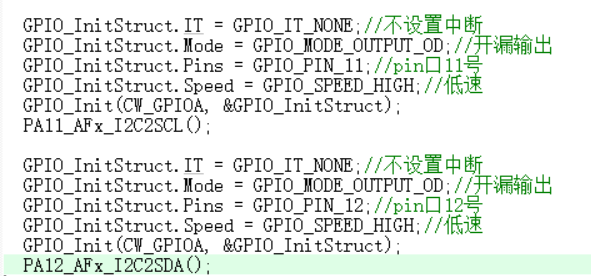

IIC支持五种不同的模式,速率从100k到5M不等,其硬件结构必然有优化,才能支持更高的速率,这一点在IIC的标准中也可窥见一二。Standard-mode下,SCL和SDA是普通的OC门,其高电平的输出依赖于外部上拉,这一架构能使多个IIC设备挂在同一条IIC总线上,但是这也限制了IIC总线的上升时间,从而限制了其通信速率。Fast-mode下,IIC的输入结构中增加了施密特触发器,使得输入的边沿可以变得更快,从而获取更高的通信速率。相应在输出结构中,虽然上升沿的速率依旧取决于外部上拉电阻和总线电容的大小,但在下降沿增加的斜率控制可以减小下降时间,通过对IO结构的改造,Fast-mode获得了比Standard-mode更高的速率。图2 给出了Fast-mode下IIC的IO结构及电平特性,Fast-mode Plus在IO结构上和Fast-mode并无二致,但从图2可以看出,其驱动电流最大为20mA(Fast-mode下为3mA),这意味着Fast-mode Plus下可以有更快的下降沿和更小的上拉电阻(上升沿也可以更快),从而获得更高的速率。需要注意的是,从IO结构上看,MOS管是有串接电阻的(标准里说该电阻可选),为的是抑制总线的尖峰和串扰,但是这个电阻的存在会让低电平不为0,在Fast-mode Plus下,由于驱动电流更大,输出的低电平的值也就更高,部分IIC电平转换芯片输出低电平可达到0.6V左右,此时需要注意输出低电平是否超门限。相比于Fast-mode Plus,在Hs-mode下,主机设备具有一个用于SDAH信号的开漏输出缓冲器(从机设备也有),并在SCLH输出端集成了开漏下拉和电流源上拉电路,并且在传输期间不执行仲裁或时钟同步,从而提高了数据传输速率。Ultra Fast-mode则采用了推挽的输出结构,因此Ultra Fast-mode和其他模式不兼容,也不支持线与(由于推挽输出结构,多设备并联时,如果有不同设备同时输出高电平和低电平,则会发生短路),但是推挽的结构进一步提升了通信速率。

图2 Fast-mode下IIC的IO结构及电平特性

不同模式所定义的速率上限是怎么来的?大于规定速率的话会怎样?

IIC的不同模式之间速率差异极大,且每种模式的速率提升都伴有硬件架构上的改进和升级。那么,各种模式所规定的速率上限是严谨计算而来的吗?假设在Standard-mode下,VCC为3.3V(电压越高,通信速率理论上限应该更低,因为在其他条件一定时,越高的电压等级意味着越长的上升时间),灌电流为3mA,最大输出电压为0.4V,那么上拉电阻的最小值为:

在总线电容400pf的情况下,电压从0上升到0.3VCC所需要的时间为:

电压从0上升到0.7VCC所需要的时间为:

故上升时间为:

假设上升沿是线性的,那么,电平从0到Vcc所需的时间为:

IIC的下降时间远小于上升时间,这里假设两者相等,则上升下降时间总和为:

假设上升下降时间占整个周期的20%,则Standard-mode下,IIC的最大频率为:

可见,即使在各项都放大的情况下,算出来的最大频率都要比Standard-mode所规定的频率最大值要大。所以,各种模式下所规定的的速率是否为硬性要求就值得考虑了。

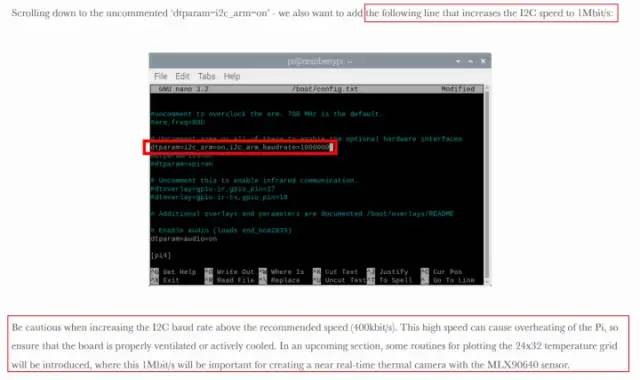

图3 IIC超推荐频率使用实例

图3给出了一个IIC超推荐频率使用的实例,在《 High Resolution Thermal Camera with Raspberry Pi and MLX90640》 中,作者将IIC的速率提高到1Mbit/s(推荐为400kbit/s),而需要担心的仅仅是散热,当然,再高的速率可能导致误码。所以,IIC各种模式规定的速率只是一个推荐值,但超规格使用一般是不建议的。

总线电容400pf的要求是怎么确定的,为什么Fast-mode Plus速率更快,总线电容却可以更大?

IIC的设备地址是7位,所以理论上IIC总线上可以挂127个设备(地址0x0不使用),但是IIC总线有400pf的限制,所以一般而言,IIC总线上的设备数是达不到127的。那么,400pf这个限制是怎么来的呢?要讨论这个问题,首先要明确总线电容会影响什么参数。首先,电容的的大小会影响总线电压的充放电速度,从而影响上升/下降沿的斜率,这对通信速率形成了限制;其次,总线电容和电阻形成了一个滤波器,当频率高时,信号会产生衰减,当信号衰减幅度超过电平判决门限时,就会导致误码,因此其对通信频率也是一个限制。这两点在我的 《串口通信》 一文中已经展开讨论过,在正常情况下,这两点所确认的总线电容上限都比400pf要大得多,而且充放电速度的大小不仅取决于总线电容的大小,对IIC总线而言,还和上拉电阻的大小以及驱动电流的上限相关。根据IIC的标准,Fast-mode Plus的总线电容上限为550pf,相较于Fast-mode,其拥有更高的通信速率但却可以容忍更大的总线电容,其原因就是因为Fast-mode plus的灌电流能力能达到20mA(实际看部分芯片的数据手册,30mA的也有),所以无论是总线电容400pf的限制还是灌电流能力,这些我个人都倾向于认为是标准给出的一个建议值,而各半导体厂商在设计芯片时,首先会满足标准的要求,保证各厂家芯片对接的通用性,这是标准存在的意义。当然,在满足标准的前提下,如果成本上满足要求或基于产品竞争力的考虑,厂家也可以将芯片设计得更强大(例如30mA的灌电流能力),这就是芯片手册的参数和标准不尽一致的原因。

为什么会有上升、下降时间的限制?Fast-mode和Fast-mode Plus的下降

时间为什么还有最小值的限制?

图1给出了几种模式下上升、下降时间的要求,根据相关参数可以看出,上升/下降时间最大值占整个周期时间的12%左右,即使将标准放宽一倍,其时间占比也不足整个周期的50%。那么,缓慢的上升/下降时间到底会带来什么不好的影响呢?

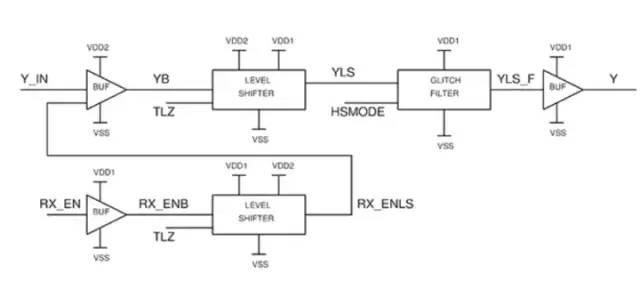

上升/下降时间所规定的都属输入端的要求,所以要讨论这个问题,首先要弄清楚IIC输入结构是什么样子, 《Designing I/O Drivers for Integrated Circuit IIC Modules》 一文中给出了IIC模块输入结构的框图,如图3所示。

图4 IIC的输入结构框图

由图4可以看到,IIC输入经过buffer缓冲,在移位寄存器处实现电平转换,过滤毛刺后再输出给后级的处理逻辑。缓冲器的结构示意图如图4所示,可以看做是两个反相器的串联,而反相器的则是由CMOS电路组成的,即IIC信号输入首先到达的是一个CMOS反相器。

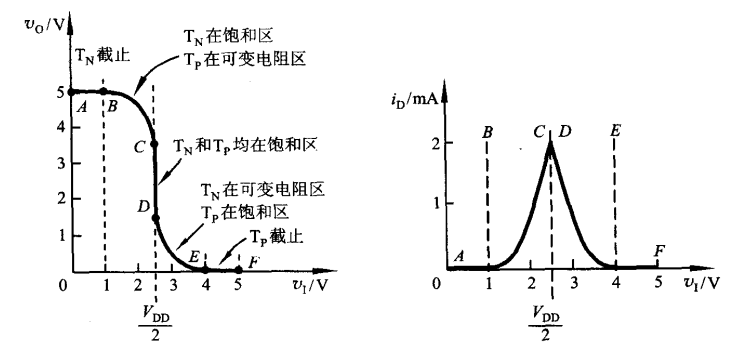

图5 CMOS反相器

CMOS反相器由一个NMOS和一个PMOS组成,其电路结构如图5所示。其原理也比较简单,在输入为高时,NMOS导通,输出为0;输入为低时,PMOS导通,输出为1。在华科的 《电子技术基础——数字部分》 一书中,还给出了其电压、电流传输特性如图5所示。从其电压、电流的传输特性可以看出,CMOS电路的两个MOS管可能存在直通的现象,虽然书中理想化地将该电压标注为VDD/2,但从MOS管的工作原理上看,两个MOS同时导通必然对应的是一个电压范围。也就是说,过长的上升/下降时间会使CMOS电路直通的时间变长,从而增加电路损耗甚至可能导致器件损坏。

图6 CMOS电压电流传输特性

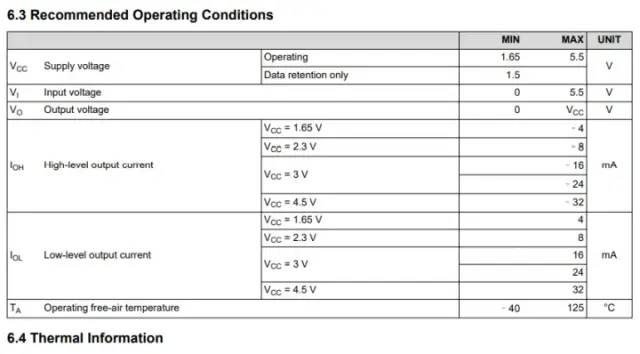

但在图1中,上升/下降时间不仅有最大值的限制,在Fast-mode和Fast-mode plus下,下降时间的最小值也存在限制。前述,相较于Standard-mode,Fast-mode的硬件结构在输入端增加了施密特触发器和尖峰抑制,输出端增加了斜率控制电路,但是,查看施密特触发器的datasheet(以SN74LVC1G17为参考),上升时间并没有相关的规格要求。

图7 SN74LVC1G17的参数要求

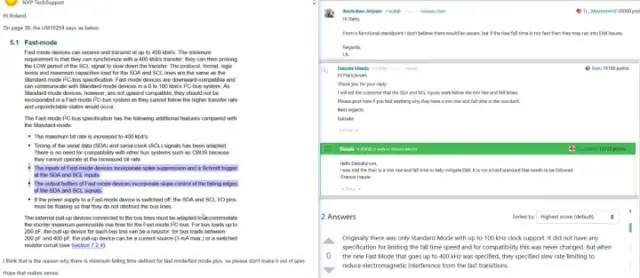

在NXP和TI的社区中,关于这个问题的解释见图8,NXP的解释是可能和Fast-mode的输入输出结构相关,但并未给出具体的原因;TI给出的回答是在Fast-mode以及更高速率的模式下,上升/下降时间太快可能带来EMI问题,但这一规定并不是强制要求的(根据经验,下降时间一般都小于20ns,且我本人尚未碰到过应用问题)。

图8 NXP和TI社区中关于上升时间最低值限制的问题

建立、保持时间的要求从何而来?

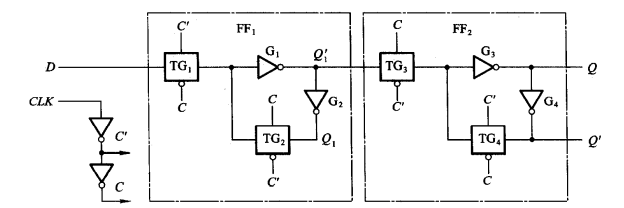

由图3可知,从机接收到输入信号后,会将其保存到寄存器中,在输入到后级进行处理。寄存器由触发器构成,以D触发器为例,其结构如图8所示。

图9 D触发器的电路结构

根据图9可以看出,D触发器实际是由两个锁存器串联而成,当CLK为低电平时,传输门TG1、TG4打开,TG2、TG3关闭,触发器的输入信号经过G1输出到Q1’,并经过Q1输出到TG2的输入端,当CLK变高瞬间,TG1、TG4关闭,TG2、TG3打开,主锁存器的输出通过TG3输出,在这个过程中,需要确保TG2有关闭到打开时,传输门两边的电平一致,这样Q1’才能输出稳定的信号,建立时间指的便是TG1、G1、G2的延时,即:

保持时间要求的来源也类似,为保证输出Q稳定,则在CLK变高时,Q1’的电平要保持稳定,而TG1的关闭需要时间,所以保持时间为:

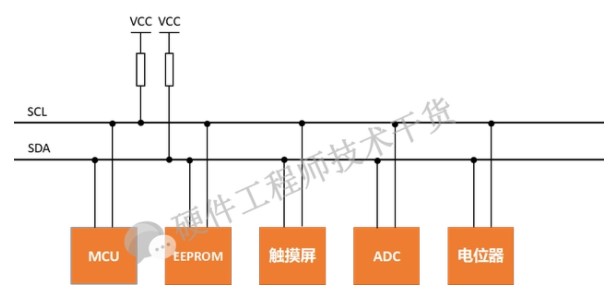

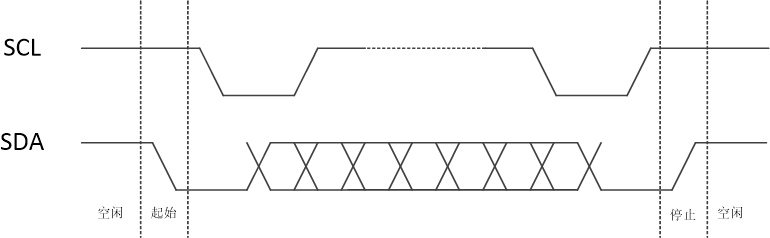

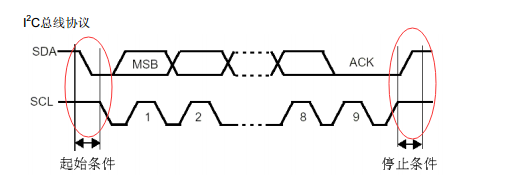

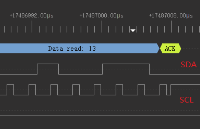

IIC总线的通信协议

IIC的一帧数据包含9个bit,主要包括起始位、停止位、读写标志位、应答位、设备地址、寄存器地址以及数据几项内容。其中, SCL为高时,SDA拉低为起始标志位;SCL为高时,SDA拉高为停止标志位;读写标志位只有一位,0表示写,1表示读;应答位低有效,应答位为高表示非应答。另外,IIC的读写帧格式不太一样,下面分别描述。

- 写操作

IIC写操作时的帧格式如图10所示,阴影部分为主机发出,空白部分则为从机发出。首先由主机发出起始位,由于IIC可能有多个设备,所以在起始位发出后,第一帧数据会发送设备地址对从机进行寻址(设备地址一般为7bit),第8位数据则是读写标志位,在写操作时,该bit为0,第9位则为从机发出的应答位。完成寻址后,需要指定要写入寄存器的地址,随后写入数据。完成以上步骤,主机发出停止位,即完成了一次读操作。

图10 IIC写操作的帧格式

读操作

读操作稍微比较复杂,有读当前地址数据和随机读两种不同场景。读当前地址数据的帧格式如图11 所示。在主机选择相应的从机设备后,从机会将数据发送给主机,数据传输完成后,主机发出NACK后发出停止位即完成一次数据传输。

图11 IIC读当前地址的帧格式

随机读模式较为复杂,其帧格式如图12所示。由于要指定特定寄存器地址,所以IIC首先要进行一次写操作(无需写入数据,只是为了定位到需要读取的寄存器地址),随后再按读当前地址的帧格式操作即可完成随机地址寄存器信息的读取。

图12 IIC读随机地址的帧格式

关于IIC的帧格式这一块,网上的资料众多,相关芯片的数据手册里对此也有很多描述,IIC的读写操作还有单次读写和页读写的操作,其帧格式在此不再赘述。

关于时钟延展

时钟延展在IIC标准的High-speed mode的章节中有所提及,这一功能是为了解决系统中存在使用不同速率的IIC总线设备的通信问题,它允许从机在来不及处理数据的时候拉低SCL,从而有更多的时间处理接收到的数据。这一功能让IIC变得更加灵活,因为从机可以控制SCL意味着给了从机设备发出中断的能力,那么在通信或者其他功能的控制上就可以更加方便。这一功能在实际的应用中也比较常见。

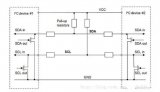

关于仲裁

IIC总线允许在同一条主线上有多个主机和多个从机,那么在多个主机同时发起通信的时候,就会产生冲突,而解决这个冲突的过程就是仲裁。IIC的仲裁机制由其OC/OD门输出结构实现,多个设备挂在同一条IIC总线上时时线与的关系,那么其时钟速率必然由速率最低的主机决定(假设占空比为50%,由于线与的特性,SCL的波形决定于低电平最长的主机的SCL)。但是,SCL和SDA是同时发出的,且SCL和SDA互相感知不到对方是否正常,在多主机冲突的时候,即使SCL的波形已经由频率最低的主机决定了,其他主机的SDA也依然在继续发送数据。所以,在SCL为高时,每个主机会探测SDA上的数据是否与自己发送的数据一致,不一致则退出总线控制权的竞争,在这个过程当中,IIC数据不会丢失,且最后剩下的主机即使有超过一个,那么对应从机收到的数据也是正确的。通过以上描述可以知道,IIC总线控制权的竞争仅取决于SDA,多个主机无法排优先级。

德赢Vwin官网

App

德赢Vwin官网

App

评论