基于TMS320C6455的高速SRIO接口设计

引 言

数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域。随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如ADI(美国vwin 器件)公司的TigerSHARC系列和TI(德州仪器)公司的C6000系列,但是,要实现对运算量和实时性要求越来越高的DSP 算法,如对基于分数阶傅立叶变换的Chirp信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片 DSP 仍然显得力不从心。这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源。采用多DSP、多FPGA系统,将是提高运算能力的一个有效途径。二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移。对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多DSP之间、DSP与高速AD采集系统、DSP与FPGA间的高速数据传输,是影响信号处理流程的主要瓶颈之一。TI公司最新推出的高性能 TMS320C6455(下文称C6455)处理器,具有高速运算能力的同时集成了高速串行接口SRIO,方便多DSP以及DSP与FPGA之间的数据传输,在一定程度上满足了高速实时处理和传输的要求。本文在多DSP+FPGA通用信号处理平台的基础上,深入研究了多DSP间,DSP与FPGA间的SRIO的数据通信和加载技术的软硬件设计与实现。这些技术包括了目前SRIO接口的各种应用方式,可作为SRIO接口及C6455开发提供参考[1-3]。

1 C6455特性及SRIO标准介绍

C6455是目前单片处理能力最强的新型高性能定点DSP,它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品。最高主频为1.2GHz,16位定点处理能力为9600MMAC/s。C6455建立在增强型C64x+ DSP内核基础之上,代码尺寸平均缩短了20%至30%,周期效率提高了20%。C6455不仅是内核的增强和运算速度的提升,相比以前的芯片,集成了丰富的外围接口,如千兆以太网控制器,66 MHz PCI总线接口,最重要的是增加了新的外设接口SRIO,全双工工作时,四个端口峰值速率每秒高达25 Gbits,解决了DSP高速数据传输的瓶颈,降低了开发多处理器系统的难度[4-5]。

RapidIO是新一代高速互连技术,已于2004年被国际标准化组织(ISO)和国际电工协会(IEC)批准为ISO/IEC DIS 18372标准。RapidIO互连定义包括两类技术:面向高性能微处理器及系统互连的Parallel RapidIO接口;面向串行背板、DSP和相关串行控制平面应用的Serial RapidIO接口。SRIO支持编程模型包括基本存储器映射IO事务、基于端口的消息传递和基于硬件一致性的全局共享分布式处理器。

SRIO互连架构是一个开放的标准,满足了嵌入式基础实施在应用方面的广泛需要。可行的应用包括多处理器、存储器、网络设备中的存储器映射I/O器件、存储子系统和通用计算平台。这一互连技术主要作为系统内部互连,支持芯片到芯片和板到板的通信,可以实现从1Gbps到60Gbps的性能水平,在高速互连方面将会有广阔的发展前景[6]。

2 C6455间的SRIO通信

2.1 C6455间的接口互连

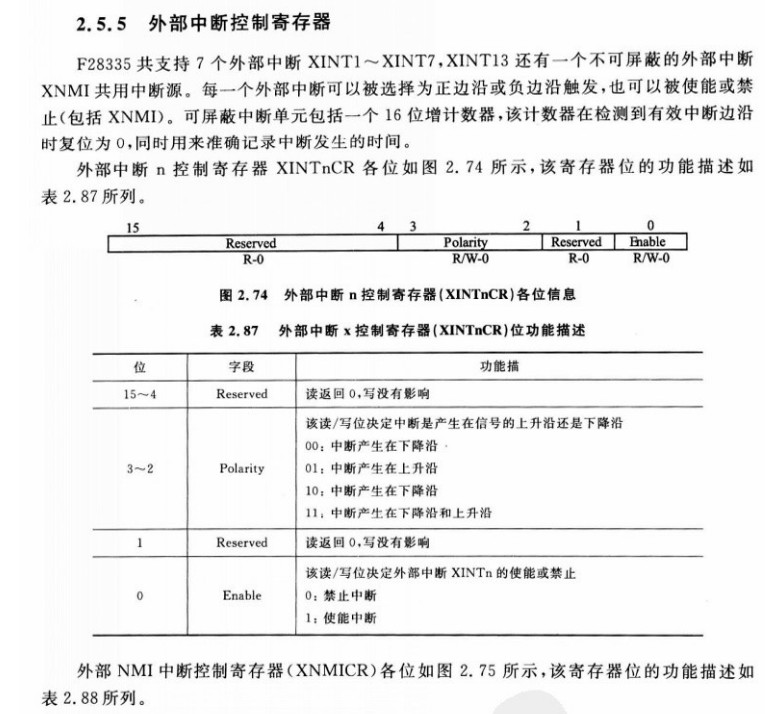

C6455内嵌了SRIO模块,拥有4个全双工的port(端口),支持SRIO 1x/4x串行协议。每个port支持1.25Gbps、2.5Gbps、3.125Gbps的波特率,每个port可以单独构成1x模式,也可以四个 port共同构成4x模式。SRIO采用的是CML(电流型逻辑)电平,布线时必须遵循布线约束。为了最小化来自接收方100欧终端电阻的反射,差分对应该具有50欧的阻抗,并且差分走线必须等长。在接收端串接耦合电容,隔离直流偏置。图1是两片C6455之间SRIO接口设计。

2.2 包格式

SRIO的传输操作是基于请求和响应机制,包(packet)是系统中端点器件的通信单元。图2是一次传输操作的流程图。首先由发起者产生一个传输请求,请求包被传输到相邻的交换器件,从而进入交换结构,通过交换机构这个完整的请求包被转发到目标器件。目标器件根据请求完成相应操作后,发送相应的响应包,经过交换机构传回到发起者。此时一个完整的传输过程完成。

SRIO有三个层的协议共同组成,每层协议在包中都有体现。图3给出典型的请求包和响应包的包格式示意图。

请求包以物理层字段开始。S位指示这是一个包还是一个控制符号,AckID表明交换结构器件将使用控制符号来确认哪一个包,Prio字段指示用于流量控制的包优先级,TT为目标地址和源地址字段指示传输地址的机制类型、报应被递送到的器件的地址和产生包的器件的地址,Ftype表示正被请求的事务,长度字段等于编码后事务的长度,SRIO事务数据的有效载荷长度从1到256字节不等,源事务ID指示发送器件的事务ID,SRIO器件在两个端点器件间最多允许256个未完成的事务。对于存储器映射事务,跟随在源事务ID后面的是器件偏移地址字段,用于指示数据的存放地址,CRC为校验码。

响应包与请求包类似,状态字段指示是否成功完成了事务,目标事务ID字段的值与请求包中断事务ID字段的值相等。

2.3 SRIO基本读写和门铃操作

根据包的格式的不同,将事务划分成很多类型,其中最重要的类型有三种:NREAD(基本读操作)、NWRITE(基本写操作)、DOORBELL(门铃操作)。 通过这三种类型的组合就可以完成所有的存储器读写操作。在介绍读写操作之前,先介绍一下与SRIO有关的DMA操作。

在C6455上,SRIO数据传输和DMA传输是结合的。此DMA与EDMA方式是独立的,当进行SRIO传输时,DMA以自动方式启动。对与发送方来说,DMA将数据从L2 SRAM搬移到SRIO端口,对于接收方来说,DMA将数据从SRIO端口搬移到L2 SRAM内存。因此,在进行传输时,读写地址是直接显示在包里的,而且此地址就是被读写的DSP的地址。换句话说,DSP可以对另一片DSP的L2 SRAM直接进行读写操作。图4就是自动DMA的传输操作。

读写操作和门铃操作主要由图5中的7个寄存器进行控制,这些寄存器里的值会自动加入到包中。在SRIO总线上,每个SRIO设备都有一个相应的设备地址,设备地址好比一个SRIO设备的ID,用于区别不同的SRIO设备。当SRIO总线上的一个SRIO设备进行读写访问时,它发送的包就含有设备地址,只有自身设备地址与包的设备地址符合的SRIO设备才会对此次传输做出响应。SRIO Address MSB和SRIO Address LSB共同构成64-bit寻址,指示的是被访问SRIO设备的地址。开发板上只用到32-bit寻址,因此,SRIO Address MSB为0,SRIO Address LSB指示的是被访问的DSP的地址。DSP address指示的是本地DSP的地址。Byte_count这一项给出的是传输字节数,一次读写操作(可以是很多包)最多可以传送4Kbytes的数据。DestID是目标设备的ID号,用来区分SRIO总线上的设备。Drbll Info用于门铃事件,通过此位段的设置,从而向目标DSP产生中断。Packet Type用来指示此次传输的类型,例如NREAD、NWRITE和DOORBELL等。

图6是SRIO模块的NREAD、NWRITE和DOORBELL程序编写流程图。首先初始化SRIO端口,此过程主要需要配置和使能PLL模块,使能并配置接收模块,使能并配置发送模块,使能并配置中断模块。配置这些模块特别要注意的是使主DSP和从DSP的时钟模块工作在相同的波特率。初始化完成后,查询SRIO链路是否成功建立,如果SRIO链路没有建立,则重新初始化SRIO端口,直到SRIO链路建立为止。链路建立后就可以进行读写操作和门铃操作,两片DSP之间可以进行高速的数据传输。实际测试表明,DSP间的数据传输可工作于1x和4x模式,每种模式可以正常工作于每通道3.125Gbps 的传输速率。

3 C6455间的SRIO加载

3.1 C6455引导模式

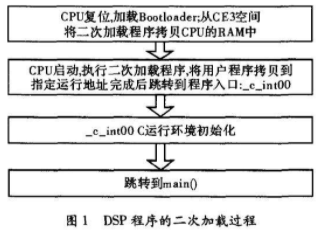

在C6455的地址空间0x00100000到0x00107FFF集成了32K的内部ROM。此ROM中固化了一段 “boot loader”的引导代码,它主要作用是在DSP上电时,对DSP进行必要的配置,以便辅助HPI/PCI/SRIO等接口进行加载;另外,它还可以将代码从外部存储器读到内部L2 SRAM,以完成代码加载。

C6455复位和上电时的引导模式主要有:NO BOOT模式,主机引导模式,FLASH引导模式,主I2C引导模式,从I2C引导模式,SRIO引导模式。C6455的EMIFA端口引脚EMIFA [0:19]和ABA[1:0]被复用作配置引脚,和专用引脚PCI_EN一起构成C6455的硬件配置引脚。采用哪种引导模式,由复位或上电时采样管脚 BOOTMOOD[3:0]来决定[7-9]。表1是引导模式选择方式。

对被加载的从DSP来说,设置BOOTMOOD[3:0]=1x00,此时为SRIO引导模式,SRIO被配置成四个1x端口,由port0对从DSP进行加载。另外,差分晶振选择125M的时钟源。上电后,固化在从DSP内部ROM的“boot loader”对从DSP进行一些必要的初始化配置:

使能全局中断,SRIO的中断管脚被使能,使从 DSP可以接收来自主DSP的中断;

boot loader配置PLL1模块为15倍频,也就是使内核工作在750MHz;

boot loader初始化从 DSP的SRIO端口,使SRIO的时钟模块配置成1.25G。

主DSP对SRIO端口进行初始化配置,并将时钟模块配置成1.25G。此时主DSP与从DSP之间互相发送同步信息,直到链路建立。链路成功建立以后,主DSP执行NWRITE操作,将待加载程序装载到L2 SRAM内存中。代码装载完成后,执行门铃操作,向从DSP发送中断,从DSP收到中断后脱离“挂起”状态,从地址0x800000处运行程序,加载过程结束。图7便是SRIO引导过程。实测表明,主DSP通过FLASH加载完成后,可通过SRIO接口对从DSP完成加载。

4 C6455与FPGA等构建SRIO网络

SRIO与微处理器总线类似,它在硬件中完成存储器和器件寻址以及分组处理,降低了用于I/O处理的开销,减小了延迟。一个运行于3.125 Gbps的4通道SRIO链路能在完全保持数据完整性的前提下提供25 Gbps的流量,保障了海量数据传输的实时性。

SRIO网络建立在两个“基本模块”基础之上:端点设备(Endpoint)和交换设备(Switch)。有两种连接方式,一种是简单的端点到端点互联,一种是端点到交换设备的互联,端点设备负责收发数据包,交换设备负责在端口之间传递数据包,但不负责数据包的解释。通过Switch交换,可以构建一个 CPU,DSP以及FPGA不同平台互联互通的数据传输网,进行共享式或分布式处理。图8给出了SRIO网络的构建模块。

C6455具有很强的处理能力,但对于并行算法,采用FPGA可以达到更高的效率。本文以SRIO为桥接,设计了一个C6455和Xilinx Virtex-4 FPGA两者相结合的处理平台,C6455和Virtex-4都有丰富的接口,该平台不但实现了C6455与Virtex-4之间的数据传输,还实现了 PCI、网络MAC、USB等不同协议域之间建立数据流。结构如图9所示。

SRIO系统由一块主C6455管理,可加载另外2片C6455,也可建立SRIO到SRIO,PCI到SRIO,MAC到SRIO等数据流。 Xilinx公司根据最新的RapidIO v1.3规范设计了其端点IP解决方案,同时集成了PCIe,以太网MACs等IP核,PCIe的32/64位地址空间(基地址)可自动映射至34/66 位SRIO地址空间(基地址)。PCIe应用程序通过内存或I/O读写与C6455通信。这些事务均可通过流写入、原语和确认读/写事务 (SWRITEs, ATOMIC, NREADs, NWRITE/NWRITE_Rs)等I/O操作映射至SRIO空间。以实现从PCIe到SRIO或从SRIO向PCIe的转换,从而在各个协议域之间建立数据流。

5 结 论

在C6455等高端DSP中,SRIO已逐渐成为主流数据互连方式之一。SRIO具有引脚少、I/O处理开销低、可达3.125Gbps高速率等优势, C6455间的SRIO通信设计和基于SRIO的加载技术提高了系统设计的灵活性,而基于DSP和FPGA的SRIO网络设计降低了多处理器集成的难度,可方便进行共享式或分布式处理,构成具备共享带宽和强大处理能力的通用处理平台,从而更好地解决“强大计算能力”和“快速数据传输”两大挑战。

德赢Vwin官网

App

德赢Vwin官网

App

评论