晶振是个大家族,除了简单封装时钟振荡器(SPXO) 外,更有压控晶体振荡器(VCXO)、温补晶体振荡器(TCXO)、恒温晶体振荡器(OCXO),以及数字补偿晶体振荡器(MCXO或DTCXO),每种类型都有独特的性能,例如相位噪声和抖动(jitter)这两个指标。

2022-06-21 08:48:10 6936

6936

本文介时钟频率概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2012-03-10 09:55:23 4544

4544

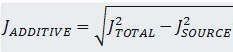

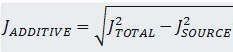

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的 SRN,然后将其与实际

2012-05-07 11:37:30 2668

2668

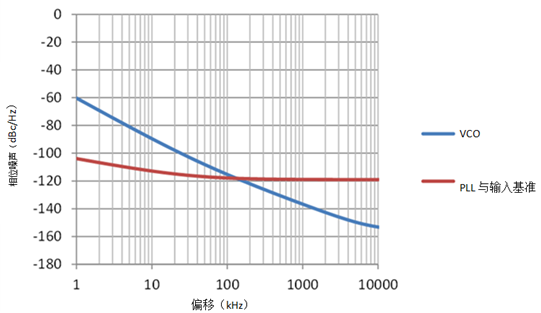

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 14342

14342

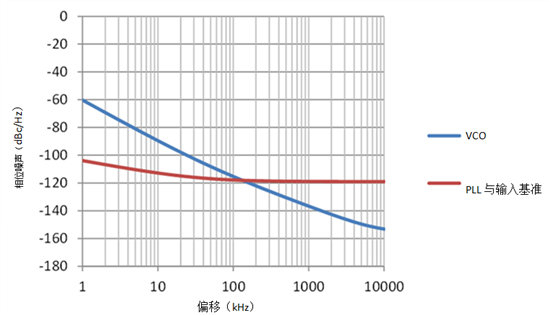

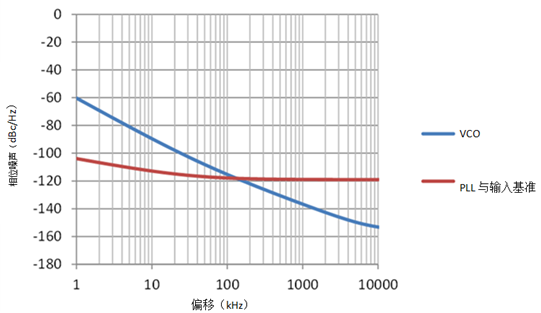

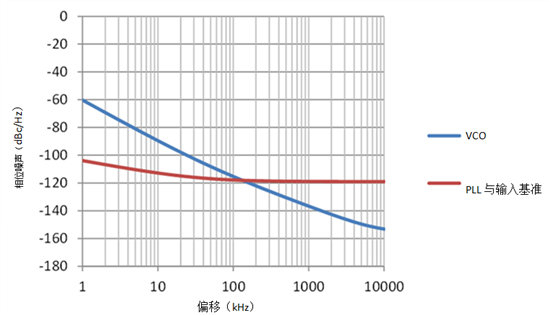

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

2016-07-18 14:24:04 10326

10326

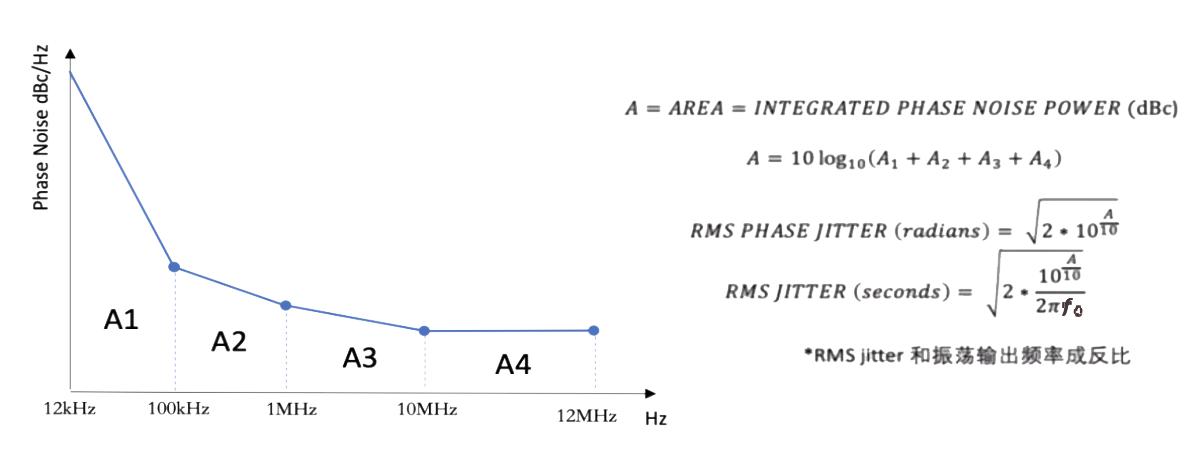

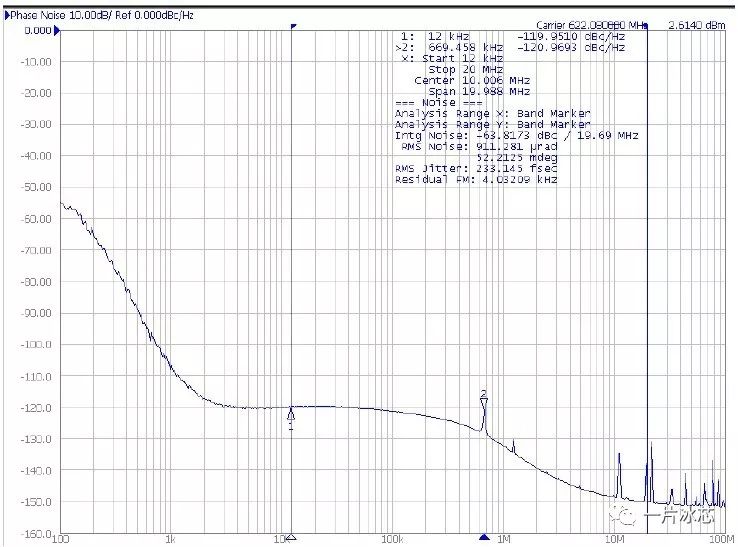

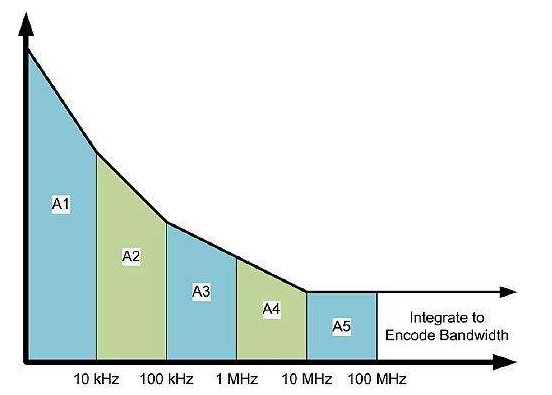

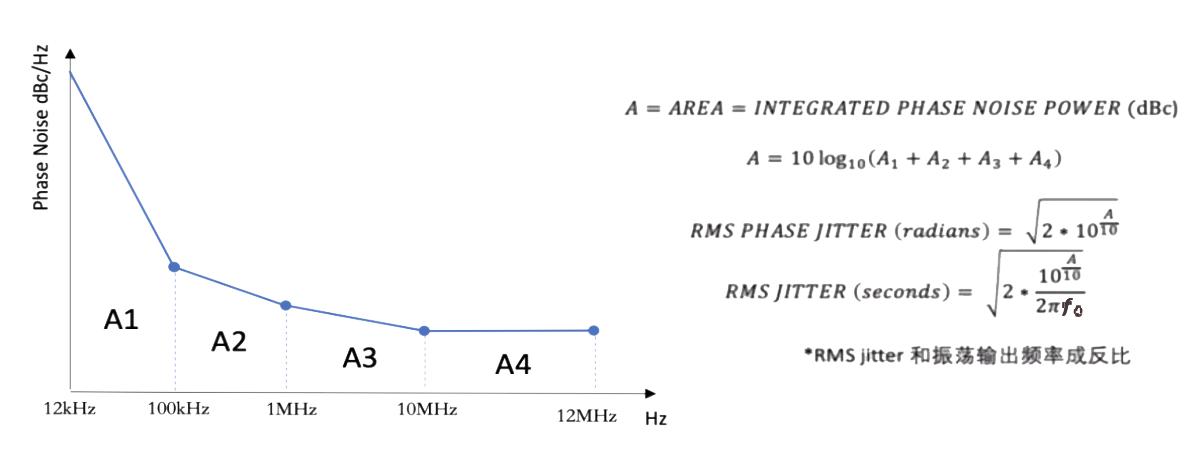

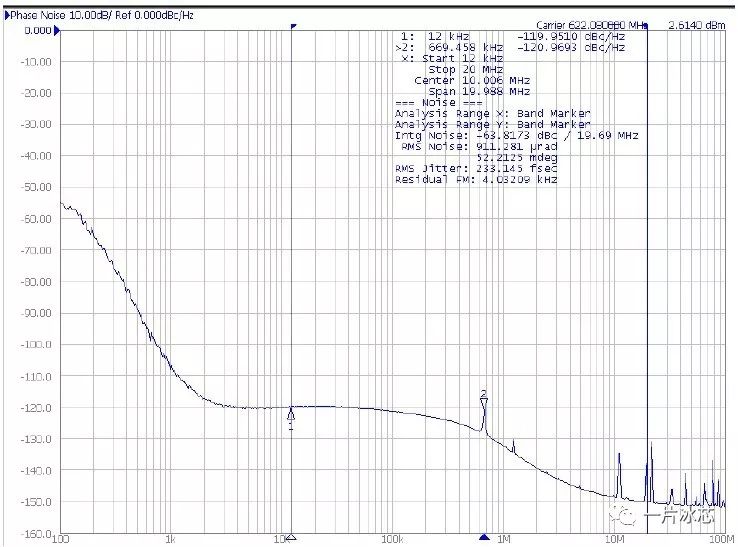

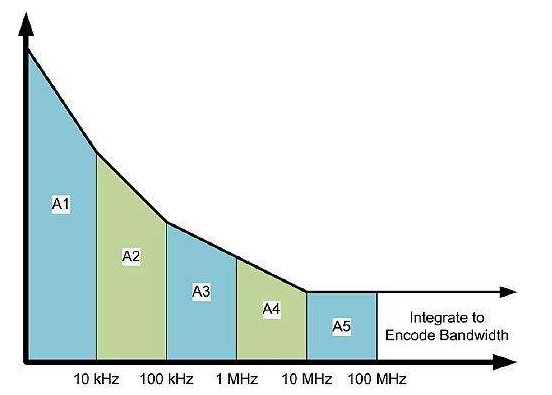

相位噪声转换到抖动的基本思想就是对相位噪声曲线进行积分。

2023-10-30 16:06:01 1025

1025

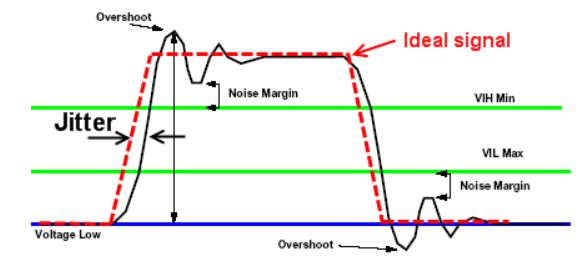

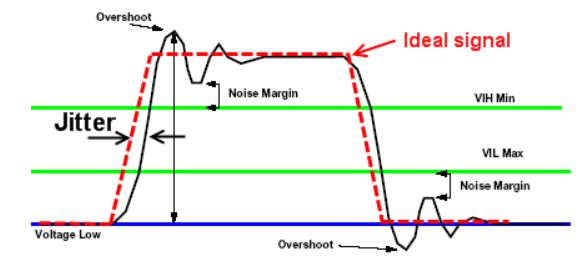

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

John Johnson 德州仪器 在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t

2018-09-19 11:47:50

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

的 BER。 系统总抖动(以及链路预算)可使用方程式 4 计算得到: 方程式4例如,10-14 的 BER 时,总抖动为: 方程式 5 表1Q 因数和误码率本文讨论了构成总抖动预算的一些参数。下一次,我们将探讨时钟,并研究随机抖动和相位噪声之间的关系。

2018-09-19 14:23:47

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2022-11-21 07:26:27

作者:Richard Zarr很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14

2018-09-13 14:18:06

我正在使用E5052B信号源分析仪来获取相位噪声数据,载波频率为20.460802MHz,频率范围为1Hz至5MHz。我试图将导出为.csv文件的相位噪声数据转换为RMS抖动(弧度),但是我在整个

2018-10-10 17:50:29

各位专家,我使用altera的cyclone5的DDR3硬核控制器,输入时钟是国产的125兆50PPM有源晶振,现在调试时发现对DDR3的读写偶尔出错。我们测试DDR3接口的差分时钟,发现左右抖动

2018-05-11 06:50:41

嗨,在ML605设计中,信号“PCIE_250M_MGT1_P / N”从器件“ICS874001”驱动到PCIe MGT参考时钟。根据以下链接中给出的相位噪声值,http

2020-06-08 15:30:33

大家好,我正在使用GTP进行项目。 GTP的时钟在GTP SMA端口(2V5 LVPECL)。但是,MUX 4的输出时钟有一个影响GTP PLL锁定状态的抖动。有人帮我吗?我做错了什么?提前致谢!罗马

2019-10-14 07:39:30

输出信号波形稳定性的指标之一。英语的“Jitter”有神经过敏、紧张不安或激动的意思。在表现高频石英振荡器的稳定度时,指传送数字信号时波形中产生的时间偏差和晃动。本次说明有关抖动和相位噪音的基础知识

2018-04-12 16:02:30

&;ID = 2492 &;摆脱= 88149基于DDS的Verilog代码。我的双相的DDS的作品在一定程度上(演示项目附后),但显示偶尔的相位翻转在一定条件下180度,描述如下。我

2019-08-09 09:05:22

应用中的疑问:1、传输线为2~5米,产生的附加抖动易引起锁相环失锁吗?锁相环对输入信号的抖动范围有要求吗?为保证输出的200MHz时钟稳定,锁相环对输入的时钟信号有什么具体的要求?2、在锁定的状态下,若

2018-09-18 11:14:35

。抖动对系统稳定度的影响低噪声KOAN晶振在精密电子仪器,无线电定位,高速目标跟踪和宇航通信等领域十分重要,下面一组图将说明抖动对系统稳定度的影响。假设有一个微处理器系统,其中处理器的时钟上升前需要

2020-06-10 17:38:08

关于有源晶振的相位抖动和相位噪音

在通信网络、无线传输、ATM和SONET等高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至

2023-12-14 09:19:08

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2019-06-05 07:13:30

于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。 性能指标最优带宽备注抖动BWJIT最优值一般为BWJIT。在低集成限制更高的一些情况下,有时较窄的环路带宽实际上效果更好。锁定时间无限VCO锁定时间随着环路带宽的增加而提高,但有时会受到VCO校准时间…

2022-11-16 07:56:45

什么是抖动和相位噪声?如何区分抖动和相位噪声?

2021-03-11 07:03:13

假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放弃?等一下!你是否试过伽马优化参数?

2019-07-31 07:26:15

高信噪比=低ADC孔径抖动吗?在设计中,为了避免降低ADC的性能,工程师一般会采用抖动极低的采样时钟。然而,用于产生采样时钟的振荡器常常用相位噪声而非时间抖动来描述特性。那么,有木有方法将振荡器相位噪声转换为时间抖动呢?

2019-08-13 06:27:54

随着通信系统中的时钟速度迈入GHz级,相位噪声和抖动这两个在模拟设计中十分关键的因素,也开始在数字芯片和电路板的性能中占据日益重要的位置。在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O

2009-10-13 17:23:19

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

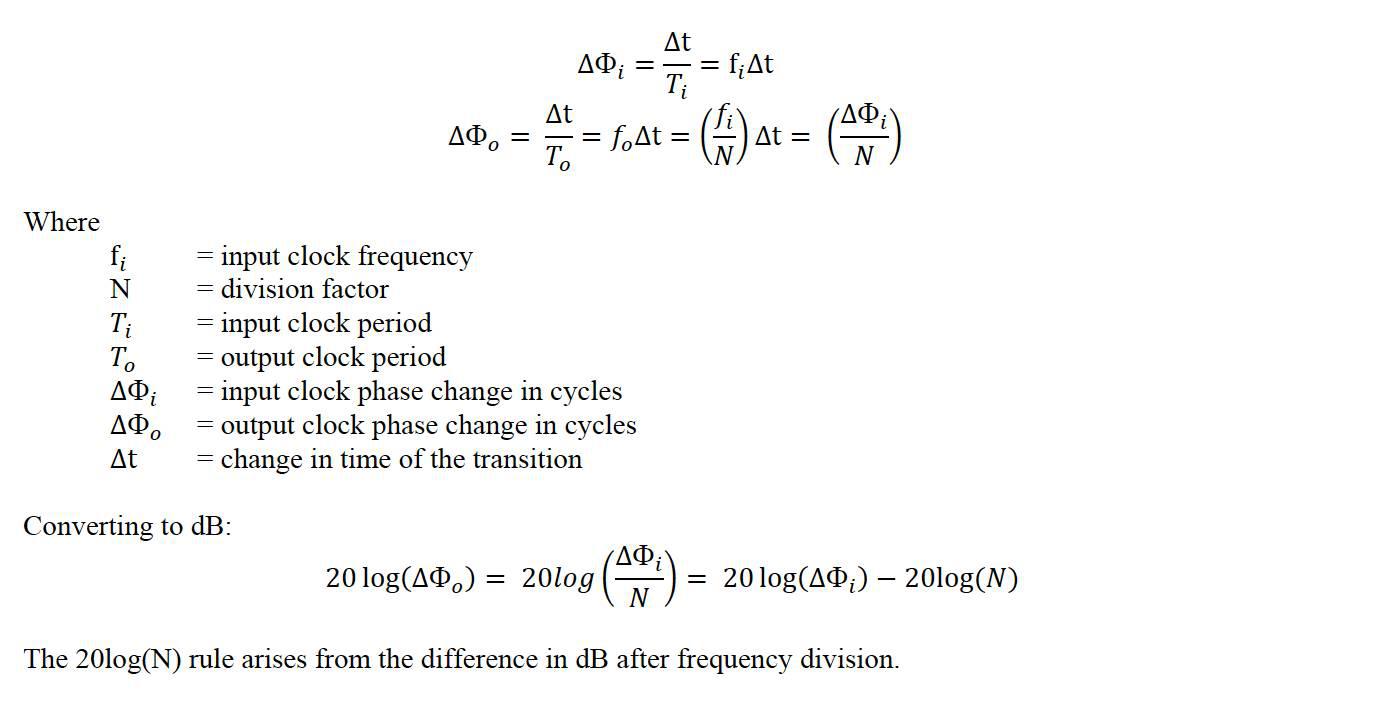

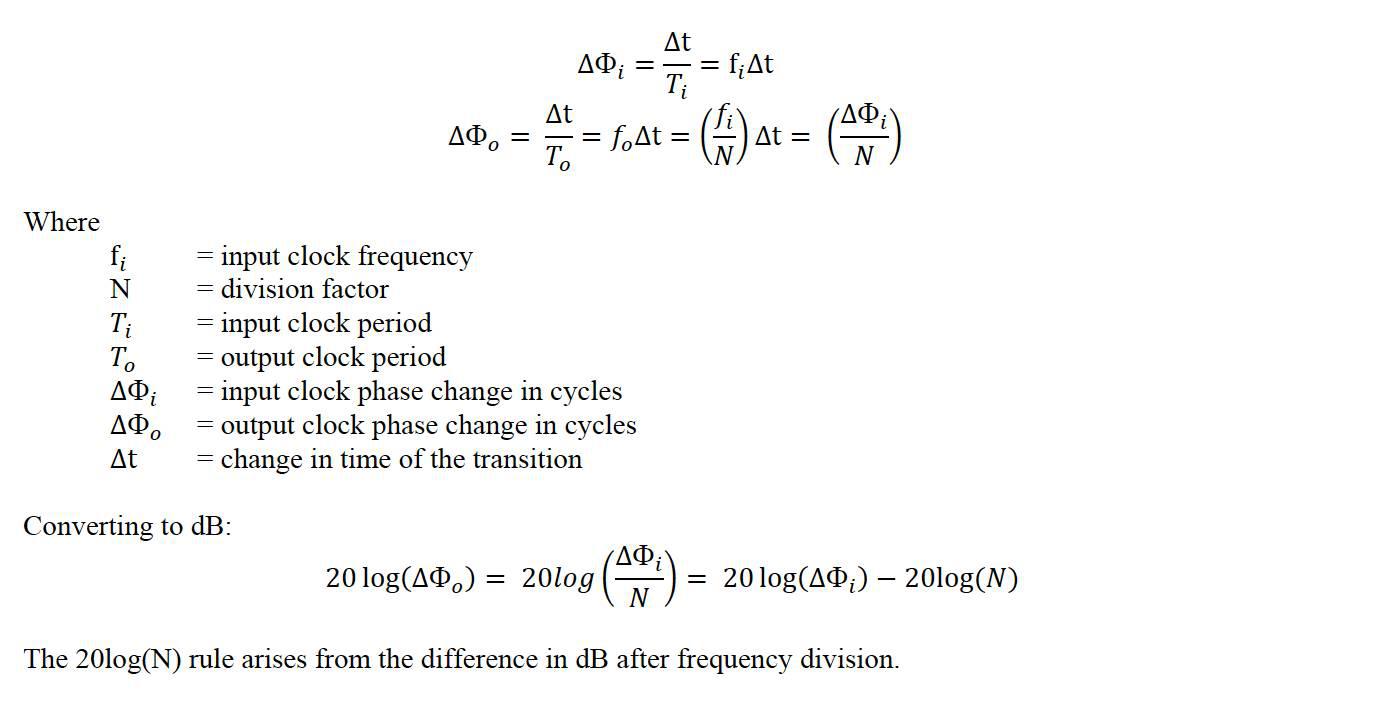

本期我将讨论在测量较低时钟频率的相位噪声和相位抖动时出现的一个非常常见的问题。在所有条件相同的情况下,我们通常期望分频的低频时钟产生比高频时钟更低的相位噪声。在数量上,你可能会记得这是20log(N

2021-06-24 07:30:00

电动助力转向系统EPS(electricpowersteering)是一种直接依靠电机提供辅助扭矩的动力转向系统,与传统的液压助力转向系统HPS(hydraulicpowersteering)相比

2019-10-16 06:16:06

设计采样系统时,关于时钟抖动性能如何考虑?抖动对时钟采样系统有何影响?

2021-04-06 06:07:38

时钟抖动或结束时钟抖动的最佳方法是什么?

2021-03-17 07:04:07

最近调试有两个问题需要您释疑: 1.9548有频率锁定和相位锁定。两者之间有关系吗?锁定有无先后顺序的要求? 2.在9548频率和相位都锁定之后,9548还是在不停的校准,为什么还会时不时的失去锁定,这是什么原因?配置问题吗?谢谢!

2018-09-05 11:45:27

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要

2018-08-29 16:02:55

本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 数位电视广播系统(DVB-T)射频调谐器之设计本计划以台积电0.35μm SiGe 制程设计一应用于数位电视广播系统之射频调谐器。其特色是先升频至1 GHz 以上之第一中频然后才降至36 MHz 之

2010-03-19 12:37:03 1

1 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 相位差的准确度直接关系着干涉仪测向的准确性,并影响整个测向系统的测向精度。在介绍干扰仪测向原理的基础上,着重分析了莱斯因子和采样速度对相位差抖动的影响,阐述了

2010-08-06 22:55:02 10

10 随着支持直接IF采样的更高分辨率数据转换器的上市,系统设计师在选择低抖动时钟电路时,需要在性能/成本之间做出权衡取舍。许多用于标定时钟抖动的传统方法都不适用于数

2010-11-27 17:12:46 32

32

双调谐回路中频放大电路

2008-12-15 17:38:29 992

992

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 3736

3736

正反馈回路和非最小相位系统根轨迹

2009-07-27 14:22:56 3430

3430 AD9547 具有高出66%的抖动性能、100倍的更窄回路滤波器带宽的时钟器件

AD9552能够替代包括OCXO(恒温

2009-09-01 17:28:35 851

851 相位噪声和抖动的概念及其估算方法

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影

2009-12-27 13:30:21 2173

2173

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 1608

1608

模数和数模转换器采样时钟内的抖动会对可实现的最大信噪比造成限制(参见参考文献部分van de Plassche著《集成模数和数模转换器》)。本应用笔记阐述了相位噪声和抖动的定义,绘制

2011-11-24 14:31:55 75

75 时钟抖动时域分析(下):

2012-05-08 15:26:25 29

29 如果明智地选择时钟,一份简单的抖动规范几乎是不够的。而重要的是,你要知道时钟噪声的带宽和频谱形状,才能在采样过程中适当地将它们考虑进去。很多系统设计师对数据转换器

2012-05-08 15:29:00 47

47 双相时钟脉电路.ms8

2012-07-16 23:10:28 47

47 业内大多数FPGA 均提供数字时钟管理( 赛灵思公司的全部FPGA 均具有这种特性)。赛灵思公司推出最先进的FPGA 提供数字时钟管理和相位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够降低抖动,并实现过滤功能。

2017-02-11 17:01:11 1625

1625

介绍 此应用笔记侧重于不同类型的时钟抖动。时钟抖动是从它的时钟边沿偏差理想的位置。了解时钟抖动非常重要在应用中,因为它起着关键作用,在时间预算一个系统。 随着系统数据速率的增加,定时抖动成为关键

2017-04-01 16:13:18 6

6 很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2017-04-08 04:51:23 1266

1266

采样时钟抖动可对高性能ADCs信噪比性能的灾难。虽然信噪比和抖动之间的关系是众所周知的,但是大多数振荡器都是根据相位噪声来指定的。

2017-08-03 10:57:33 13

13 时钟抖动时域分析,第 2 部分

2017-10-26 16:10:42 6

6 时钟抖动时域分析 第 3 部分

2017-10-26 16:13:28 4

4 时钟接口阈值区间附近的抖动会破坏ADC的时序。例如,抖动会导致确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。查看时钟信号噪声通常有三种途径:时域、频域、相位域。

2018-03-12 13:39:33 21583

21583 仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。

2018-05-14 08:51:40 3

3 该应用报告提出了在TI仪器上的CDCE72010抖动清理器和同步器PLL器件上获取的相位噪声数据。CDCE72010的相位噪声性能取决于基准时钟、VCXO时钟和CDCE72010本身的相位噪声。该应用报告显示了几个最流行的CDMA频率的相位噪声性能。此数据有助于用户为特定应用选择正确的时钟解决方案。

2018-05-15 10:58:53 7

7 本文介绍了一种通过单边带来估计时钟源的相位噪声的通用公式。载波比(SSCR),振荡周期的周期抖动。该链接允许无缝聚合。

外部时钟源相位噪声,通常以dBC/Hz给出,与片上时钟同步电路的相位稳定

2018-05-16 17:56:54 5

5 凌力尔特公司 (Linear Technology Corporation) 推出低相位噪声整数 N 合成器内核 LTC6950,该产品具超低抖动时钟分配输出电路。LTC6950 非常适用于产生

2018-09-07 16:04:00 808

808 如果一个时钟的载波频率下降了N倍,那么我们预计相位噪声会减少20log(N)。例如,每个除以因子2的除法应该导致相位噪声减少20log(2)或大约6dB。这里的主要假设是无噪声的传统数字分频器。

2018-09-28 08:14:00 10038

10038

时钟设计人员通常会提供一个相位噪声,但不提供抖动规格。相位噪声规格可以转换为抖动,首先确定时钟噪声,然后通过小角度计算将噪声与主时钟噪声成分进行比较。相位噪声功率通过计算图9中的灰色区域积分得出。

2019-08-20 11:06:53 7787

7787

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

2019-09-14 11:24:00 7712

7712

德赢Vwin官网

网为你提供测量较低时钟频率的相位噪声和相位抖动资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-27 08:40:37 10

10 德赢Vwin官网

网为你提供相位噪声处理:时钟抖动或结束时钟抖动的最佳方法是什么?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:49:06 26

26 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 LTC6950:1.4 GHz低相位噪声、低抖动锁相环,带时钟分布数据表

2021-04-19 12:13:04 3

3 作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要

2022-01-11 16:00:28 2150

2150 作者: Richard Zarr

如果您在通信行业工作,那么您可能很熟悉抖动对系统性能的影响。抖动不仅会降低数据转换器的性能,而且还可在高速数字系统中产生误码。凭直觉判断,给时钟增加噪声会增大系统

2021-11-23 17:45:07 1769

1769

发现抖动、相位噪声、锁定时间或杂散问题?请检查锁相环的环路滤波器带宽

2022-11-02 08:16:24 15

15 时钟采样系统最大限度减少抖动

2022-11-04 09:52:12 0

0 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 1

1 在设计中使用超快速数据转换器的高速应用通常需要非常干净的时钟信号,以确保外部时钟源不会对系统的整体动态性能产生不需要的噪声。因此,选择合适的系统组件至关重要,这有助于产生低相位抖动时钟。以下应用笔记可作为选择合适的元件的宝贵指南,以设计适用于超快速数据转换器的基于PLL的低相位噪声时钟发生器。

2023-02-25 10:50:48 2307

2307

采用PLL的时钟发生器广泛用于网络设备中,用于生成高精度和低抖动参考时钟或保持同步网络操作。大多数时钟振荡器使用理想、干净的电源给出其抖动或相位噪声规格。然而,在实际的系统环境中,电源可能会因板载开关电源或嘈杂的数字ASIC而受到干扰。为了在系统设计中实现最佳性能,了解这种干扰的影响非常重要。

2023-03-08 15:33:00 897

897

抖动和相位噪声是晶振的非常重要指标,本文主要从抖动和相位噪声定义及原理出发,阐述其在不同场景下对数字系统、高速串行接口、数据转换器和射频系统的影响。 1. 抖动和相位噪声 1.1. 抖动

2023-03-10 14:54:32 657

657

抖动和相位噪声是晶振的非常重要指标,本文主要从抖动和相位噪声定义及原理出发,阐述其在不同场景下对数字系统、高速串行接口、数据转换器和射频系统的影响。

2023-03-26 09:09:11 693

693

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1637

1637 作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

2023-04-12 10:32:17 1950

1950

理想值附近的一个范围内,从而造成相邻的时钟边沿存在偏差。在时序分析时,时钟抖动是一个重要的因素。多种因素会导致时钟抖动,包括PLL回路噪声、电源纹波、热噪声以及信号之间的串扰等。

2023-06-09 09:40:50 1128

1128

这是为数不多的跨越围栏是有利的情况之一。目前市面上的许多时钟产品都指定器件的相位噪声,而不指定抖动。让我们来看看如何从相位噪声变为抖动。然后,我们将能够预测具有一定抖动的ADC的SNR。一个例子将不得不等待,因为我在这里只有这么多空间。现在让我们专注于数学。下图显示了我们如何根据时钟源的相位噪声计算抖动。

2023-06-30 16:58:01 566

566

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 960

960

相噪是与哪种类型的抖动相对应?如何理解相位噪声与时间抖动的关系? 相位噪声与时间抖动是两个在信号处理领域中经常涉及的概念。在讨论相位噪声时,我们常常听到相位噪声和时间抖动的联系。因此,本文将探讨相位

2023-10-20 15:08:11 561

561 相位噪声和抖动是对时钟频谱纯度的两种表述形式,一个是频域一个是时域,从原理上来说,它们是等效的。

2023-10-30 16:02:46 687

687

,包括时钟抖动、噪声抖动、跳变抖动和漂移抖动。 时钟抖动是指时钟信号在频率和相位上的变化。时钟信号是大多数电子系统中用于同步和定时的关键信号,其稳定性对系统的性能有着重要影响。时钟抖动会导致测量结果的不确定性

2024-01-19 15:01:31 254

254 会导致晶振的输出频率出现一定的不稳定性,从而影响到系统的时钟同步和信号处理。相位抖动常常以皮克-到-皮克的相位偏移量来衡量,通常以ps级别或fs级别来表示。相位抖动在通信系统、时钟系统和高精度测量设备中都是非常重要

2024-01-25 13:51:07 127

127 抖动是相位抖动的主要原因之一。在通信系统中,时钟扮演着非常重要的角色,它确定了信号的采样时间和传输速率。然而,由于各种原因,包括晶体振荡器的温度变化、电力供应的不稳定、电磁干扰等,时钟信号会产生偏移和抖动,导

2024-01-25 15:29:28 171

171 ,包括电路稳定性不良、时钟补偿误差、温度变化、电磁干扰等。相位噪声对信号有着广泛的影响,包括降低信号的频谱纯度、引起功率泄露、产生频率副瓣、导致系统误码率的提高等。 抖动是指信号的周期性变化,通常表现为时间轴上信号

2024-01-29 13:54:34 230

230 相位噪声与时间抖动有何关系?如何测试时间抖动? 相位噪声和时间抖动在信号处理中是两个非常重要的概念。它们都是衡量信号或系统的稳定性和准确性的指标。虽然它们在一些方面是相关的,但它们也有一些不同之处

2024-01-31 09:29:00 138

138

德赢Vwin官网

App

德赢Vwin官网

App

评论