业界领先的全新 1.8V 版 VersaClock® 3S 可编程

时钟发生器,为消耗品和计算系统创造具有竞争力的性能、能耗和灵活性。

2017-09-28 10:15:46

8178

8178

德州仪器(

TI)日前宣布

推出一款具有业界最佳

抖动性能的高度集成的

时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的

时钟频率

2011-10-10 09:19:30

1112

1112

讯 - 全球半导体解决方案供应商瑞萨电子(TSE:6723)今日宣布,

推出新款

时钟发生器VersaClock® 7。此款具有内部集成晶体版本可选的可编程

时钟发生器产品家族,适用于高端运算系统、有线

基础设施和数据中心

设备中的PCIe®和网络应用。VersaClock 7拥有无可比拟的灵活性,使设计人员能够配置不同

2022-11-30 15:08:03

1351

1351

Wong表示:“未来通信

基础设施的

时钟要求,会远远超出当前石英晶体谐振

器的

设备性能。通过将

TIBAW谐振

器直接集成到

时钟

设备中,我们可以实现

超低

抖动性能和弹性,满足在通信转型的过程中对数据管道在抗震

2019-03-05 06:45:06

概述:AD9577是一款既提供一个多路输出

时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络

时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低

抖动频率合成器产品系列,确保实现最高的网

2021-04-06 06:49:57

的高性能

时钟分配和

时钟

发生产品系统,使系统设计师可以实现数据转换

器的最佳性能。HMC1032LP6GE和HMC1034LP6GE为SMT封装

时钟发生器,是多种高性能蜂窝/4G

基础设施、光纤和网络应用的理想

2018-10-18 11:29:03

系统设计师通常侧重于为应用选择最合适的数据转换

器,在向数据转换

器提供输入的

时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑

时钟发生器的相位噪声和

抖动性能,数据转换

器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

噪声抑制和出色的电源抑制比 (PSRR) 来帮助改进无错数据传输。图2显示的是使用LMK03328时对PSRR和TX眼图性能的改进,其原因就在于LMK03328集成了一个LDO。图2:SAW示波器和

TILMK03328

时钟发生器的PSRR请在下方给我们留言,告诉我们你在正在研究的、最能从

超低

抖动中受益的应用。

2018-09-05 16:07:30

25千兆以太网 (25GbE) 正在快速发展,并且很多分析人士预计它将在未来4年中呈现指数

性的迅速增长。想象一下设计有线网络

设备来支持过多标准,以及用最小数据包损失和延迟来快速

提升数据速率时的复杂

2022-11-18 07:31:24

输出

时钟分配功能,具有亚皮秒级

抖动性能,并且片内集成锁相环(PLL)和电压控制振荡

器(VCO)。 产品名称:

时钟发生器AD9520-3BCPZ特征低相位噪声、锁相环(PLL)片内VCO的调谐频率范围为

2019-07-09 11:50:41

多路输出

时钟发生器功能,内置专用PLL内核,针对以太网线路卡应用进行了优化。 产品名称:

时钟发生器AD9571ACPZPEC特征 全集成VCO/PLL内核 156.25 MHz时,

抖动值:0.17

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140A可编程多

时钟发生器评估板。评估

抖动性能和功能很容易

2020-07-27 15:01:46

CDCM61002 1:2

超低

抖动晶体

时钟发生器

2023-03-28 18:26:06

概述:MAX3625B是MAXIM公司生产的一款提供三路输出的低

抖动,高精度

时钟发生器。该MAX3625B是为网络应用而优化的低

抖动,高精度

时钟发生器。该器件集成一个晶体振荡

器和锁相环(PLL)

时钟

2021-05-18 07:39:05

专业销售、维修、回收 高频 二手仪器。 产品型号: CG635美国斯坦福

时钟发生器信息描述:

时钟可调频由0.001Hz到2.05GHz少于1PS的RMS

抖动

可支持CMOS。PECL,ECL,LVDS

2020-08-18 09:08:58

SI5340-EVB,评估板用于评估Si5340低

抖动任意频率

时钟发生器。 Si5340采用获得专利的Multisynth技术,

可产生多达10个独立

时钟频率,每个频率具有0 ppm的合成误差

2019-02-26 09:28:56

SI5341-EVB,评估板用于评估Si5341低

抖动任意频率

时钟发生器。 Si5341采用获得专利的Multisynth技术,

可产生多达10个独立

时钟频率,每个频率具有0 ppm的合成误差

2019-02-25 07:03:01

在我们的设计中,其中一个模块从外部可配置

时钟发生器芯片接收其

时钟信号。现在在我们的ML507上使用这个

时钟发生器芯片IDT5V9885就在那里任何跳线设置?我们问这个是因为在我们的申请中软件我们

2019-09-02 08:12:30

。因此,硬件

可靠性设计在保证元器件

可靠性的基础上,既要考虑单一控制单元的

可靠性设计,更要考虑整个控制系统的

可靠性设计。

2021-01-25 07:13:16

找不到联系方式,请在浏览

器上搜索一下,旺贸通仪器仪 产品型号: CG635美国斯坦福

时钟发生器信息描述:

时钟可调频由0.001Hz到2.05GHz少于1PS的RMS

抖动

可支持CMOS。PECL,ECL

2019-06-16 12:07:43

随着数字化或物联网的出现,传感

器正成为工业

基础设施应用的核心。在这种情况下,应用依赖 MEMS 进行状态监控和结构健康监测,与这些新应用相伴而来的是关于性能和

可靠性的非常具体的标准。智能

基础设施利用

2018-10-30 15:00:04

专业销售、维修、回收 高频 二手仪器。 产品型号: CG635美国斯坦福

时钟发生器信息描述:

时钟可调频由0.001Hz到2.05GHz少于1PS的RMS

抖动

可支持CMOS。PECL,ECL,LVDS

2020-12-03 08:39:05

AD9525 / PCBZ-VCO,用于评估安装了2950MHz VCO的AD9525的所有功能的评估板。 AD9525是一款低

抖动

时钟发生器,具有正确的LVPECL输出,旨在支持长期演进(LTE)和多载波GSM基站设计的转换

器

时钟要求

2019-02-26 09:38:38

AD9525 / PCBZ,用于AD9525

时钟发生器的评估板。 AD9525旨在支持长期演进(LTE)和多载波GSM基站设计的转换

器

时钟要求。 AD9525提供低功耗,多输出,

时钟分配功能和低

抖动

2019-02-25 08:38:34

AD9576 / PCBZ,AD9576评估板提供多输出

时钟发生器功能,包括两个专用锁相环(PLL)内核,具有灵活的频率转换功能,经过优化,可作为整个系统的强大异步

时钟源,提供扩展功能通过监控和冗余

2019-02-25 09:40:01

双环路

时钟发生器

可清除

抖动并提供多个高频输出

2021-04-06 07:20:32

?疑问3:是不是使用PLL类型的

时钟发生器芯片带来的

抖动误差会比较大?针对14位的ADC输入差分

时钟有此类型的参考吗? 模拟输入部分:疑问1:参考文档中使用AD8138差分驱动芯片,计划采用5v单电源模式

2018-11-07 09:35:54

AC1571

时钟发生器一款基于PLL的、适用于5G基站应用的

时钟发生器。采用数字锁相环技术,以实现最佳的高频低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技术,管脚兼容843N571,可以

2022-08-11 16:26:33

采用网络同步和 BAW 技术的

超低

抖动

时钟发生器Function Clock network synchronizer, Ultra-low jitter clock generator

2022-12-02 13:47:14

2:8

超低功耗、低

抖动

时钟发生器,引脚模式型号 V2G Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:16

具有单个 PLL 的

超低

抖动

时钟发生器系列 Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:16

具有两个独立 PLL 的

超低

抖动

时钟发生器系列 Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:17

2:8

超低功耗、低

抖动

时钟发生器,引脚模式型号 F Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:18

2:8

超低功耗、低

抖动

时钟发生器Function Ultra-low jitter clock generator Number of outputs 8 Output

2022-12-02 13:47:19

具有 14 路输出的

超低

抖动

时钟发生器Function Ultra-low jitter clock generator Number of outputs 14

2022-12-02 13:47:20

具有集成双路 VCO 的 4 路输出

时钟发生器/

抖动消除

器Function Clock generator Number of outputs 2 Output

2022-12-02 13:47:24

全集成式宽范围低

抖动晶振

时钟发生器Function Clock generator Number of outputs 1 Output frequency (Max

2022-12-02 13:47:28

1:1

超低

抖动晶振

时钟发生器Function Clock generator Number of outputs 1 Output frequency (Max

2022-12-02 13:47:30

1:2

超低

抖动晶振

时钟发生器Function Clock generator Number of outputs 2 Output frequency (Max

2022-12-02 13:47:30

1:4

超低

抖动晶振

时钟发生器Function Clock generator Number of outputs 4 Output frequency (Max

2022-12-02 13:47:30

具有集成双路 VCO 的 5/10 路输出

时钟发生器/

抖动消除

器Function Clock generator Number of outputs 5 Output

2022-12-02 13:47:31

MAX3625B是一款低

抖动、精密

时钟发生器,优化用于网络

设备。器件内置晶体振荡器和锁相环(PLL)

时钟倍频器,以产生高频

时钟输出,用于以太网、10G光纤通道及其它网络

设备。Ma

2010-03-01 08:54:52

126

126

;以太网线卡,交换机和路由

器· SCSI,SATA,and PCI-express· 低

抖动,低相噪

时钟发生器

2023-12-12 14:25:17

时钟发生器芯片厂家

时钟芯片是一种基于PLL的

时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,

可实现小于0.3ps RMS的相位

抖动性能

2023-12-29 09:29:50

时钟发生器芯片厂家

时钟芯片是一种基于PLL的

时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,

可实现小于0.3ps RMS的相位

抖动性能

2024-02-04 11:41:14

服务范围横向科研技术⽀持和服务、轨道交通、核电、装备领域板卡失效分析、

可靠性寿命试验方案及

可靠性

提升方案开发与执行。检测项目基于寿命特征分析的板卡寿命及剩余寿命研究:l 板卡X-ray

2024-03-15 17:27:02

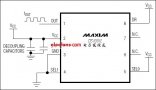

MAX9489/MAX9471多输出

时钟发生器构建集成

时钟源 摘要:与典型的“本地”

时钟方案相比,集成的多输出

时钟发生器有许多优势。本文探讨了集中

时钟发生器(如

2008-10-04 20:43:25

922

922

精密

时钟发生器电路图

2009-03-25 09:35:22

1054

1054

振荡器

时钟发生器电路图

2009-04-13 08:54:22

720

720

摘要:与典型的“本地”

时钟方案相比,集成的多输出

时钟发生器有许多优势。本文探讨了集中

时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-04-22 10:11:53

407

407

摘要:与典型的“本地”

时钟方案相比,集成的多输出

时钟发生器有许多优势。本文探讨了集中

时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-05-03 11:07:05

653

653

MAX3625A 低

抖动、精密

时钟发生器,提供三路输出

2009-08-13 13:01:27

828

828

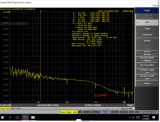

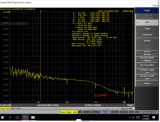

评估低

抖动PLL

时钟发生器的电源噪声抑制性能 本文介绍了电源噪声对基于PLL的

时钟发生器的干扰,并讨论了几种用于评估确定性

抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32

1461

1461

MAX3624 低

抖动、精密

时钟发生器,提供四路输出 概述 MAX3624是一款低

抖动精密

2009-09-18 08:56:41

682

682

Maxim

推出高性能、三路输出

时钟发生器MAX3625B Maxim近日

推出高性能、三路输出

时钟发生器MAX3625B,适用于以太网和光纤通道网络

设备。器件采用低噪声VCO和PLL架构,能够

2009-12-14 17:25:04

1041

1041

MAX3625B

抖动仅为0.36ps的PLL

时钟发生器概述 MAX3625B是一款低

抖动、精密

时钟发生器,优化用于网络

设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18

1345

1345

MAX3679A高性能四路输出

时钟发生器(Maxim) Maxim

推出用于以太网

设备的高性能、四路输出

时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49

778

778

-- AD9553

时钟发生器提供引脚编程模式和可定制的 SPI 编程模式,有利于 GPON、OC-48光纤网络和无线通信

基础设施设备的设计。-- ADCLK944高速

时钟扇出缓冲器可降低 SON

2010-05-25 10:50:32

523

523

在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS

时钟发生器(GPS同步

时钟)对维持系统正常运转有至关重要的意义。 那如何利用GPS OEM来进行二次开发,产生高精度

时钟

发生

2010-09-17 22:02:44

1273

1273

DS1091L是一款低成本的

时钟发生器,输出频率由工厂预置到130kHz至66.6MHz,标称精度为±0.25%。器件可产生中心

抖动或降频

抖动扩频输出,具有引脚可选的

抖动幅度和

抖动速率。

2011-03-16 10:57:41

1037

1037

德州仪器(

TI)(纽约证券交易所代码:TXN)今天宣布

推出一款具有业界最佳

抖动性能的高度集成的

时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的

时钟频率,从而

2011-10-08 11:36:42

812

812

MAX3636是一个高度灵活,高精度锁相环(PLL)

时钟发生器为下一代网络

设备的要求低

抖动

时钟发生器和强大的高速数据传输的分布进行了优化。

2011-10-11 11:15:22

1329

1329

DS1086 EconOscillator™是可编程的

时钟发生器,它可以在260kHz至133MHz的频率范围内产生扩展频谱(

抖动)方波输出。

2012-03-22 15:43:01

1175

1175

Pericom

推出一项全新的HiFlex

时钟发生器产品系列,该系列产品可提供多频率输出,同时具有

超低噪声(

抖动)、高集成度及高灵活性的特点,完美地适用于网络、云计算和其他需要多频率及输出的高性能平台。

2013-01-29 09:14:04

1045

1045

双环路

时钟发生器可清除

抖动并提供多个高频输出

2016-01-04 17:41:13

0

0

10GHz扩频

时钟发生器的设计_胡帅帅

2017-01-07 21:28:58

1

1

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的

时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑

时钟发生器、相位噪声和

抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。

2017-11-17 02:00:58

752

752

Microchip基于MEMS的

时钟发生器

2018-06-07 13:46:00

4534

4534

Microchip基于MEMS的

时钟发生器

2018-07-08 01:23:00

3933

3933

据麦姆斯咨询报道,Microchip

推出了业界尺寸最小的MEMS

时钟发生器DSC613。这款新器件可在电路板上最多替换掉三个晶振和振荡器,从而减少高达80%的

时钟元件布板空间。

2018-11-15 16:38:26

3910

3910

AD9523:14路LVPECL/LVDS/HSTL输出 或29路LVCMOS输出 低

抖动

时钟发生器

2019-07-04 06:18:00

3604

3604

TI

推出超低

抖动

时钟发生器,以实现更

可靠的

电信

基础设施设备,设计人员可以优化系统性能,简化

设备配置并减少设计周期时间。

2019-08-09 15:10:28

1653

1653

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的

时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑

时钟发生器的相位噪声和

抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34:38

2666

2666

具 PLL 的 5 输

出超低

抖动

时钟分配器提供独特的多芯片输出同步方法

2021-03-19 10:54:50

10

10

AD9523-1:低

抖动

时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册

2021-03-21 14:28:08

1

1

AD9525: 8路LVPECL输出低

抖动

时钟发生器

2021-03-21 15:00:20

0

0

AD9540:655 MHz低

抖动

时钟发生器数据表

2021-03-22 19:57:57

0

0

AD9571:以太网

时钟发生器,10个

时钟输出

2021-04-16 10:21:56

3

3

AD9530:4 CML输出、低

抖动

时钟发生器,集成5.4 GHz压控振荡器数据表

2021-04-24 12:02:38

0

0

AD9551:多业务

时钟发生器数据表

2021-04-28 10:30:52

0

0

AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515

时钟分配IC的高性能ADC的低

抖动采样

时钟发生器

2021-04-30 09:48:42

13

13

AD9575:网络

时钟发生器,双输出数据表

2021-05-09 11:06:44

1

1

超低

抖动

时钟发生器和分配器最大限度地提高数据转换器的信噪比

2021-05-18 20:57:30

0

0

时钟发生器AD9516-0技术手册

2022-01-25 15:59:42

7

7

Cypress

时钟发生器应用在车辆、工业生产、消费品和网络服务的EMI降低和非EMI降低

时钟发生器。 Cypress具有广泛的

时钟发生器组合,兼容700MHz的频率和不超过0.7PS的RMS相位

抖动

2022-04-22 09:02:09

806

806

超低

抖动

时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15

0

0

新品速递 全球半导体解决方案供应商瑞萨电子(TSE:6723)宣布,

推出新款

时钟发生器VersaClock 7。此款具有内部集成晶体版本可选的可编程

时钟发生器产品家族,适用于高端运算系统、有线

2022-12-01 18:55:06

611

611

采用PLL的

时钟发生器广泛用于网络

设备中,用于生成高精度和低

抖动参考

时钟或保持同步网络操作。大多数

时钟振荡器使用理想、干净的电源给出其

抖动或相位噪声规格。然而,在实际的系统环境中,电源可能会因板载开关电源或嘈杂的数字ASIC而受到干扰。为了在系统设计中实现最佳性能,了解这种干扰的影响非常重要。

2023-03-08 15:33:00

897

897

本文讨论电源噪声干扰对基于PLL的

时钟发生器的影响,并介绍几种用于评估由此产生的确定性

抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序

抖动行为。实验室台架测试结果用于比较测量技术,并演示如何

可靠地评估参考

时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39

811

811

极景微发布超小封装PCIe5.0

时钟发生器日前,极景微(UltraSilicon)宣布,

推出两款支持PCIe5.0接口标准的1输出及2输出

时钟发生器,分别为US6D101和US6D102。该芯片具有

2023-02-02 15:25:54

999

999

时钟合成器和

时钟发生器是两种用于产生

时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56

298

298

的

时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多

时钟发生器。然而,如果不慎重考虑

时钟发生器、相位噪声和

抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57

0

0

德赢Vwin官网 网站提供《FemtoClock2

抖动衰减器和

时钟发生器RC325008A数据手册.pdf》资料免费下载

2024-01-14 10:55:06

0

0

“核芯互联CLG440是一颗专为高性能服务器、计算中心应用

推出的支持PCIe 6.0、符合CK440Q标准的高性能

时钟发生器。

2024-01-16 15:57:40

279

279

德赢Vwin官网 网站提供《毫微微

时钟网络同步器、

抖动衰减器和

时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17

0

0

德赢Vwin官网 网站提供《CDCE6214

超低功率

时钟发生器数据表.pdf》资料免费下载

2024-02-28 15:38:40

0

0

德赢Vwin官网 App

德赢Vwin官网 App

评论