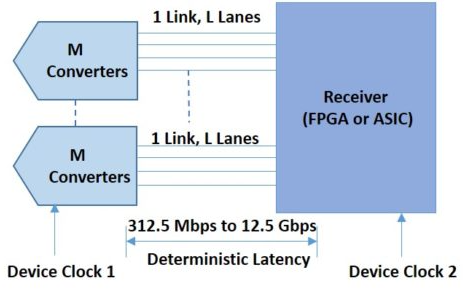

JESD204B标准提供一种将一个或多个数据转换器与数字信号处理器件接口的方法(通常是ADC或DAC与FPGA接口),相比于通常的并行数据传输,这是一种更高速度的串行接口。

2024-03-20 11:33:34 34

34

转换误差率(CER)的时域应用。AD9213具有16通道JESD204B接口,以支持最大带宽能力。AD9213实现了动态范围和线性度性能,同时功耗小于4.6 W(

2024-03-07 15:54:36

描述LTC®2122 是一款两通道、同时采样 170Msps、14 位 A/D 转换器,其具有串行 JESD204B 输出。该器件专为对高频、宽动态范围信号进行数字化处理而设计。它非常适合于要求苛刻

2024-03-01 10:48:57

AD6673BCPZ-250 特性JESD204B Subclass 0或Subclass 1编码串行数字输出信噪比(SNR):71.9 dBFS(185 MHz AIN,250

2024-02-28 19:55:42

AD9083BBCZ AD9083BBCZ 特性1.0 V 和 1.8 V 电源供电125 MHz 可用模拟输入频宽采样率高达 2 GSPS100 MHz 带宽中的噪声频谱密度= −145 dBFS/Hz,2.0 GSPS 编码SNR = 66 dBFS(100 MHz 带宽),2.0 GSPS 编码SNR = 82 dBFS(15.6

2024-02-27 19:15:07

AD9689BBPZ-2600 是一款双通道、14位、2.0 GSPS/2.6 GSPS模数转换器(ADC)。该器件内置片内缓冲器和采样保持电路,专门针对低功耗、小尺寸和易用性而设计。该产品设计支持通信应用,能够实现高达5 GHz的宽带宽模拟信号直接采样。ADC输入的−3 dB带宽为9 GHz。AD9689针对宽输入带宽、高采样速率、出色的线性度和

2024-02-27 19:13:27

国芯思辰SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。SYSREF

2024-02-19 09:41:40

信号的应用。该套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 数据接收器 (JRx) 端口、片内时钟乘法器和数

2024-02-16 17:16:40

数进行权衡。支持 8b/10b 和 64b/66b 数据编码方案。64b/66b 编码支持前向纠错 (FEC),可改进误码率。此接口向后兼容 JESD204B 接收器。

无噪声孔径延迟调节

2024-01-31 15:22:55

的应用。该套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 数据接收器 (JRx) 端口、片内时钟乘法器和数字

2024-01-04 20:01:43

的任务。

问:JESD204B中的确定延迟到底是什么?它是否就是转换器的总延迟?

答:ADC的总延迟表示其输入一个模拟样本、处理、并从器件输出数字信号所需的时间。类似地,DAC的总延迟表示从数字

2024-01-03 06:35:04

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-23 09:24:37

芯片上JESD204B协议对应的引脚(SYSREF、SYNCINB和SERDOUT)与ZYNQ7015芯片中的JESD204 IP核的端口对应相连。

2023-12-15 07:14:52

大家好,JESD204B协议已让单板多片AD采样同步变得更容易了,想请教下,如何做到多板间的AD采样同步啊,有没有什么好的思路啊。

还有AD6688的采样时钟频率范围为2.5G~3.1G,芯片支持

2023-12-12 08:27:58

8位数用 lane0 传输,采样点的低8位数用 lane1传输,如附件所示。但我在JESD204B的协议中并没有找到这种映射方式。

请问您那里有没有数据映射相关的详细资料?我需要知道数据在串行通路上的确切映射信息,因为我需要写接收端的程序。

2023-12-12 08:22:45

使用AD9680时遇到一个问题,AD9680采样率为1Gsps,JESD204B IP核的GTX参考时钟为250MHz,参数L=4,F=2,K=32,线速率为10Gbps,使用的为SYSREF

2023-12-12 08:03:49

我使用的是KC705板卡,调用了里面JESD204B的IP核,使用模式为interpolation值为4,4条链路,DAC频率为2.5GHZ,通道速度为6.25GHZ,出现的问题是:

帧同步过程

2023-12-12 07:28:25

用单片AD9690采集数据给FPGA,不要求确定延迟,因此想要把AD9690配置在JESD204B sublcass 0 模式下。但是这种模式下,对于AD9690的SYSREF±的输入管脚怎么处理?以及AD9690工作在subclass 0 模式下还有没有其他要注意的地方?

2023-12-12 06:16:08

模数转换器AD9625的评估板AD-FMCADC3-EBZ能不能和赛灵思的Virtex7系列FPGA开发板连接,我看到他们都具备JESD204B接口,物理接口上能直接连吗?还是说需要在使用转换接口来连接?

2023-12-08 08:25:12

最近在使用AD9144芯片,调试JESD204B接口出现了一些问题,暂时没有头绪,期盼能得到各位的指点。

AD9144的主要配置如下:8条JESD204B链路,subclass1,速率为

2023-12-08 06:00:25

老是显示错误如下:

root@analog:~# [15.459970] axi-jesd204-rx 84aa0000.axi-jesd204-rx: Lane 0 desynced

2023-12-07 07:09:20

你好,因为项目需要,要做一块数据采集和发生板,接口支持JESD204B,时钟我选用了AD9523-1,电路我参考FMC-DAQ2开发板,舍弃了PLL1,直接在OSC_IN接入125M时钟作参考,输出

2023-12-06 07:48:32

的AD9162-FMX-EBZ板子,看到的现象是SYSREF信号一直为高,CGS测试信号不完全拉高,每次重新配置时拉高的lane通道数还不一样。其界面设置如下图所示。FPGA的使用是条用的xilinx的JESD204 IP核。

FPGA抓到的SYNC信号与SYSREF信号如下图所示:

2023-12-05 08:23:30

使用内部PLL,输入参考频率为100MHz。在采样率时钟设置为1GHz时,DAC的JESD204B链路能建立,但是当频率改为1.5GHz时,SYNC一直为低。其他相关寄存器都已经修改,serdes

2023-12-05 08:17:30

9680测试评估中遇到问题:

按照数据手册中的配置步骤,关断链路,通过0x570和0X56E寄存器快速配置JESD204B,链路上电后,电路锁相环无法锁定,204B无法正常输出数据。

2023-12-05 08:04:26

Jesd 无法连接到的问题已经配置了 AD9173 。模式为 8, 主要的内插是 x12, 通道内插是 x1. DAC PLL 锁定在 12GHz, 双链接, L=4. 。 Reg0X281 中

2023-12-05 08:04:04

请问AD9625的寄存器需要如何设置才能打开时间戳的功能?

按照数据手册我将寄存器0x072设置为0x8B,将0x08A设置为0x22.数据经过Xilinx FPGA的JESD204B IP核,但

2023-12-05 07:33:36

, 0x00; / SYSREF 窗口)

SendCmdToAD9689(ADCSCel, 0x0571, 0x15); // JESD204B 连接下方电源

SendCmdToAD9689(ADCSCel

2023-12-05 07:30:47

近期在使用AD9162时,配置的模式不成功,测试时钟CLK发现,CLK±单端信号共模电压接近0V,手册上是0.6V,但测试9162-FMC-EZB参考板上的CLK也是共模电压为0V,请问这个会有什么影响吗?

我们现在测试配置JESD204B接口模式不正确,不确定是否CLK的影响?

2023-12-05 06:14:24

我在使用AD9163的时候遇到JESD204B的SYNC信号周期性拉低。通过读寄存器值如图,发现REG470和REG471都为0xFF,而REG472始终为0.不知有谁知道是什么原因?该如何解

2023-12-04 07:30:17

AD9164 JESD204B接口的传输层是如何对I/Q数据进行映射的

2023-12-04 07:27:34

大佬好,小弟最近在调试AD9136芯片,遇到一个问题,如下:

1.我使用的是9136模式11,单链路模式,使用一个JESD204+一个JESD204 PHY,我将JESD204的tx_charisk

2023-12-04 07:14:58

直接输出4G给DAC的clk的,内部[size=200%]PLL关闭,nco旁路,所有内插均为1,jesd204B选择模式20。

2023-12-04 06:56:33

在AD9680和AD9690数据手册上,写着它们[size=200%]支持的最小通道线率是3125Mbps,但是在JESD204B标准手册写着最小通道线率是312.5Mbps。

我疑惑这是数据手册的错误,还是AD9680和AD9690这两款芯片支持的最低通道线率确实时3125Mbps

2023-12-01 07:57:58

我们用的 AD9690-500,500M采样速率, 想配置为全带宽模式,2 Lanes, 为啥 ADC的输出通道没反应,K字符都不发送。请问这种配置模式需要寄存器如何配置? 出现这种问题可能的原因? 谢谢!

2023-12-01 07:13:46

你好:使用AD9694的DDC出现以下问题,我配置的480MHz采样率,两倍抽取,JESD204B模式6,real输入,real输出,0_Hz模式。 我不灌信号做fft显示实数,中间有一个60MHz

2023-12-01 06:29:23

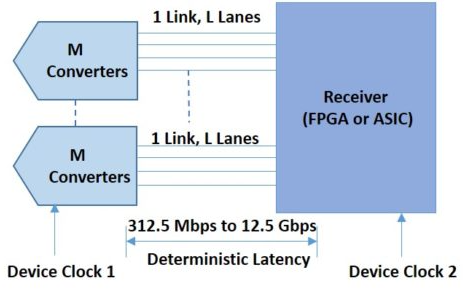

作者:Ian Beavers,ADI公司应用工程师 JESD204B串行数据链路接口针对支持更高速转换器不断增长的带宽需求而开发。作为第三代标准,它提供更高的通道速率最大值(每通道高达12.5

2023-11-28 14:24:47 0

0 德赢Vwin官网

网站提供《JESD204B规范的传输层介绍.pdf》资料免费下载

2023-11-28 10:43:31 0

0 在各种应用中(从通信基础设施到仪器仪表),对系统带宽和分辨率的更高要求促进了将多个数据转换器以阵列形式连接的需求。设计人员必须找到低噪声、高精度解决方案,才能为使用普通JESD204B串行数据转换器接口的大型数据转换器阵列提供时钟和同步。

2023-11-27 17:25:40 0

0 前言TSW14J57EVM数据采集/图形发生器:具有 16 个 JESD204B 通道 (1.6-15Gbps) 的数据转换器 EVM提示:以下是本篇文章正文内容,下面案例可供参考一

2023-11-21 15:05:23

500Msps 14-bit JESD204B 72-Pin VQFN EP TrayProduct Technical SpecificationsEU RoHSCompl

2023-11-07 19:20:52

1.3Gsps 14-bit JESD204B 64-Pin LFCSP EP TrayProduct Technical SpecificationsECCN (US)3A

2023-11-07 19:19:38

14-bit JESD204B 64-Pin LFCSP EP Tray Product Technical SpecificationsECCN (U

2023-11-07 19:17:50

14-bit JESD204B 64-Pin LFCSP EP Tray Product Technical SpecificationsEU RoH

2023-11-07 19:01:53

德赢Vwin官网

网为你提供ADI(ADI)AD9094: 8-Bit, 1 GSPS, JESD204B, Quad Analog-to-Digital Converter Data Sheet相关产品

2023-10-17 19:13:59

德赢Vwin官网

网为你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相关产品参数、数据手册,更有AD9207

2023-10-16 19:02:55

LogiCORE IP JESD204内核实现了一个JESD204B接口,使用GTX、GTH、GTP或GTY(仅限UltraScale和UltraScale+)收发器在1至8个通道上支持1至12.5

2023-10-16 10:57:17 358

358

德赢Vwin官网

网为你提供ADI(ADI)AD9694-EP: 14比特、500 MSPS、JESD204B、“四向数字转换器”强化产品数据表相关产品参数、数据手册,更有AD9694-EP: 14比特

2023-10-09 19:12:15

德赢Vwin官网

网为你提供ADI(ADI)AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次对数字转换器数据表相关产品参数、数据手册,更有AD9694S: 14-Bit

2023-10-08 16:48:36

德赢Vwin官网

网站提供《一种基于JESD204B的射频信号高速采集系统.pdf》资料免费下载

2023-09-14 11:14:07 1

1 AD9144是一款支持jesd204b协议高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的评估板(Evaluation Board),它是主要由AD9144,AD9516,与PIC16F单片机组成的系统。

2023-09-13 09:20:22 996

996

评估板 14位,1.25 GSPS/1 GSPS/820 MSPS/500 MSPS JESD204B,双模数转换器

2023-09-03 10:27:10

和时域应用。AD9213具有16通道JESD204B接口,以支持最大带宽能力。AD921 3实现动态范围和线性性能,同时典型功耗

2023-08-29 16:05:55 0

0 、JESD204B、Serial Rapid I/O*、通用公共射频接口 (CPRI) 和 IEEE 1588 等协议。

2023-07-29 10:41:27 823

823

产品概况: SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7

2023-07-25 17:06:53

本文旨在提供发生 JESD204B 链路中断情况下的调试技巧简介

2023-07-10 16:32:03 802

802

全芯时代,国产好芯不定期推荐。今日为大家介绍一款国产超低噪声时钟调节器,pin to pin替代TI的LMK04828 一、概述 该芯片是高性能时钟调节器,支持JEDEC JESD204B

2023-06-25 10:15:26 324

324 该芯片是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和 SYSREF 时钟时,PLL2 的 14 个时钟输出可配置去驱动 7 个JESD204B 转换器或其他逻辑设备。

2023-06-25 10:13:46 848

848 SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。

2023-06-21 15:11:14 508

508

SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。SYSREF可以使用直流和交流耦合来提供。不仅限于JESD204B应用,14个输出均可单独配置为传统高性能时钟系统输出。

2023-06-21 15:10:58 608

608

SYSREF计时校准▲样片标记时间戳■JESD204B串行数据接口:▲支持子类0和1▲最大通道速率:12.8Gbps▲多达16个通道可降低通道速率■双通道模式下的数字下变频器:▲实际输出:DDC旁路或

2023-06-16 14:37:21

HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考。

2023-05-31 10:47:57 1636

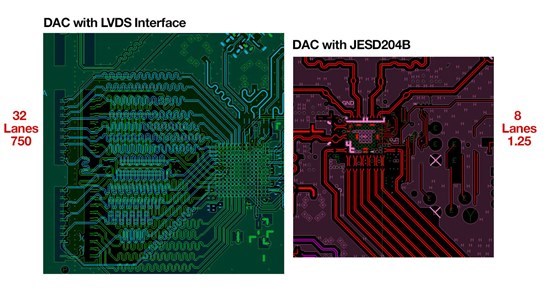

1636 您的PCB可以处理高达12.5Gbps的速度吗,感到惊讶,对吗?JESD204B标准为串行接口提供高达12.5Gbps的比特率。这种升级允许设计人员在FPGA/ASIC上使用更少的收发器,从而减少

2023-05-26 14:50:57 608

608

JESD204B规范是JEDEC标准发布的较新版本,适用于数据转换器和逻辑器件。如果您正在使用FPGA进行高速数据采集设计,您会听到新的流行词“JESD204B”。与LVDS和CMOS接口相比,这一较新的版本具有显著的优势,因为它包括更简单的布局和更少的引脚数。

2023-05-26 14:49:31 361

361

大部分的ADC和DAC都支持子类1,JESD204B标准协议中子类1包括:传输层,链路层,物理层。在少部分资料中也会介绍含有应用层,应用层是对JESD204B进行配置的接口,在标准协议中是不含此层,只是为了便于理解,添加的一个层。

2023-05-10 15:52:55 1373

1373

Cadence Allegro 之一。

4,具有高速数据传输及模数转换设计和经验者优先,包括基于LVDS或JESD204B 接口的高速ADC/DAC 、DDR3\\4 和千兆以太网等模块的设计与布线。

5

2023-04-28 09:38:20

大侠好,阿Q来也,今天是第二次和各位见面,请各位大侠多多关照。今天给各位大侠带来一篇项目开发经验分享“基于JESD204B的LMK04821芯片项目开发”第二篇,这是本人实打实的项目开发经验,希望

2023-04-20 16:59:00

LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们是高性能的双环路抖动清除器,可在具有器件和SYSREF时钟的子类1时钟方案里驱动多达七个JESD204B转换器或逻辑器件。图1是典型JESD204B系统(以LMK04821系列器件作为时钟解决方案)的高级方框图。

2023-04-18 09:25:30 918

918

数模转换器- DAC Dual, 16-b 2.8Gsps DAC,10.6Gbps JESD204B

2023-04-06 17:44:13

我在 avoinics 产品上使用 LS1028A 处理器。当前项目不需要 GPU。我计划使用 PBI 命令关闭 GPU。我的问题是关于验证 GPU 是否真的关闭。你能建议一种我可以用来验证 GPU 是否确实关闭的机制吗?这是认证所必需的。

2023-03-31 07:45:18

JESD207 FOR LATTICEECP3

2023-03-30 12:02:10

Lattice Programmable Products LatticeCORE™ License

2023-03-30 12:02:09

JESD207 FOR LATTICEECP3

2023-03-30 12:01:20

IP INTERFACE DATA-LOGIC ECP3

2023-03-30 12:01:18

EVALBOARDAD9234-1000JESD204B

2023-03-30 11:46:29

德赢Vwin官网

App

德赢Vwin官网

App

评论