摘要

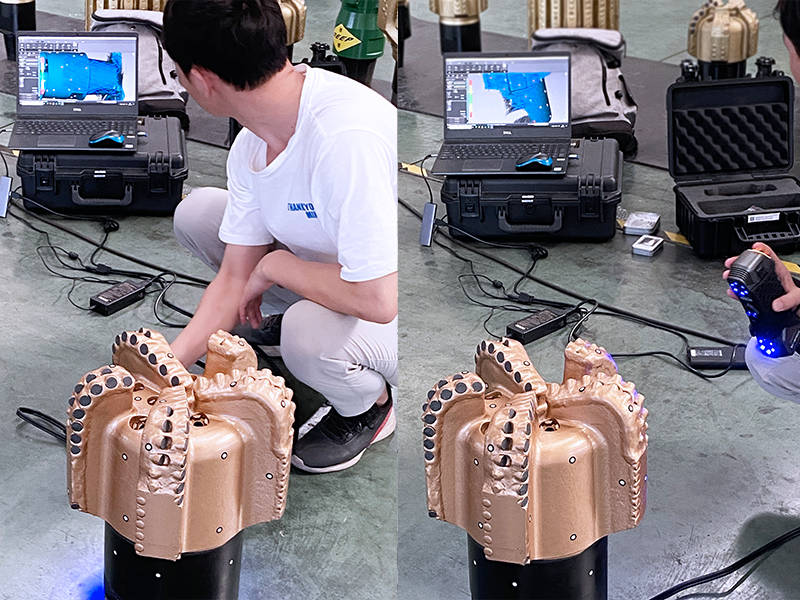

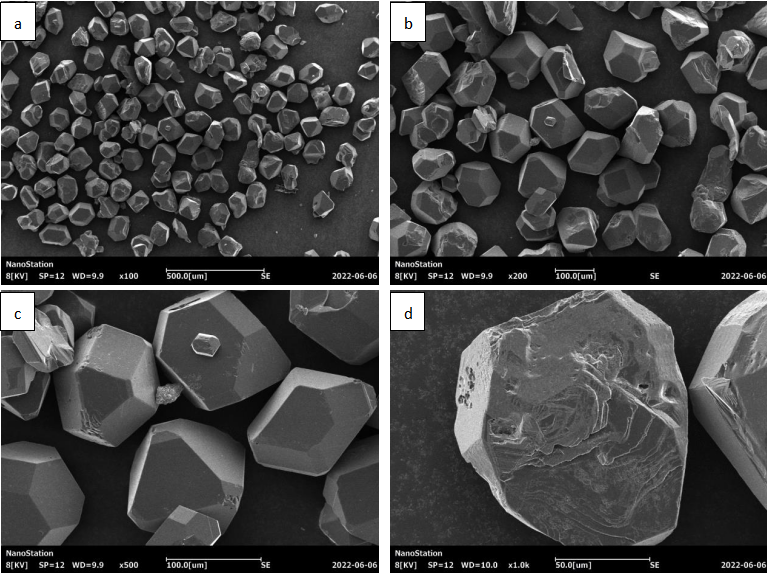

厚度约为1毫米的大面积均匀多晶金刚石薄膜在4英寸的衬底上生长并形成图案。 氧化硅晶片使用集成电路兼容工艺的微系统应用。通过在4英寸上旋转金刚石粉末装载水,实现了密度为2X 1010 /cm2的均匀、可重复的播种。晶圆片。MPCVD系统中采用1.5%甲烷氢气混合物,优化压力和微波功率进行金刚石薄膜生长。4in的厚度变化小于20%。面积使用43托尔压力和2.8kW微波功率。利用六氟化硫/O2/Ar气体进行电子回旋共振ECR辅助微波等离子体反应离子蚀刻,蚀刻速率约为80nm/min,蚀刻速率的蚀刻速率变化小于10%区域的面积。

介绍

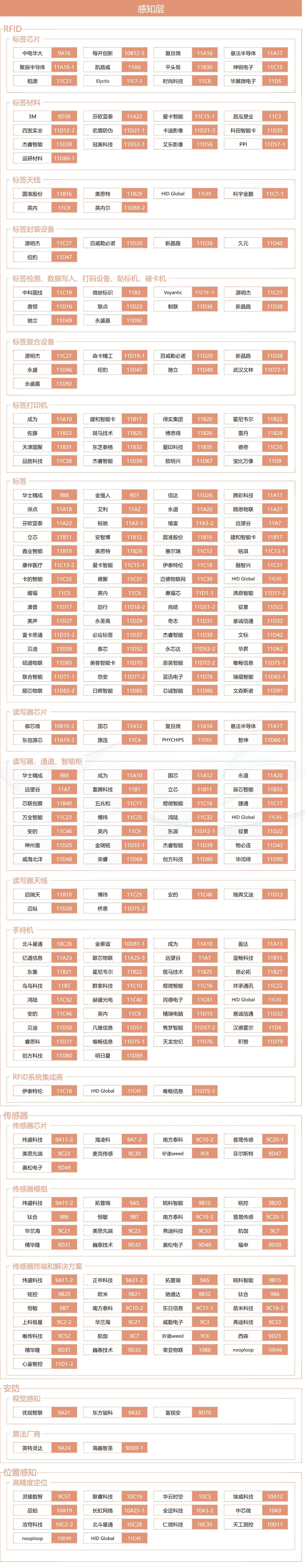

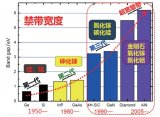

金刚石晶格中sp3C-C键的存在导致了其独特的机械、化学、光学和热性能,这与任何其他已知材料都不匹配。因此,金刚石成为一种独特的材料的应用,包括微系统和微机电系统的MEMSd,特别是在高温和恶劣的环境下。制造sp3C-C键的困难将化学气相沉积CVDd金刚石的生产推迟到1952-53年,现在导致了一种可靠的金刚石微制造技术的发展延迟,该技术与传统的微系统/MEMS技术兼容。由于目前还没有可靠的大面积金刚石热外延技术,许多研究主要集中在廉价的多晶金刚石多晶硅上,主要生长在小于2英寸的硅晶片上。虽然有些研究使用了4英寸。本文着重于所有这些问题,以发展和优化微系统的聚c技术。

聚c微系统技术

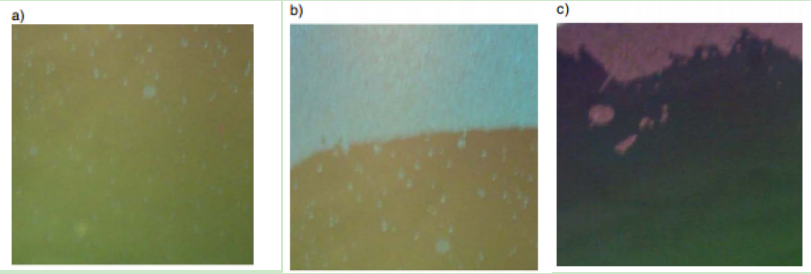

Seeding:本研究开发了一种能更好地控制均匀度和高密度的大面积播种新技术。通过在1000毫升去离子水中混合25克拉平均粒度为25纳米的金刚石粉末,并加入悬浮试剂,制备负载金刚石粉末的水sDPLWd溶液。DPLW,特别适用于清洁亲水表面,例如二氧化硅和氮化硅的表面,使用常规旋转器施加到基底上。使用超声波处理来提高悬浮粉末的均匀性。DPLW技术可在二氧化硅上产生密度在108–1010 cm-2范围内的可再现、无损和均匀的晶种,这是以前在大面积二氧化硅或氮化硅表面上的任何晶种方法都无法实现的。

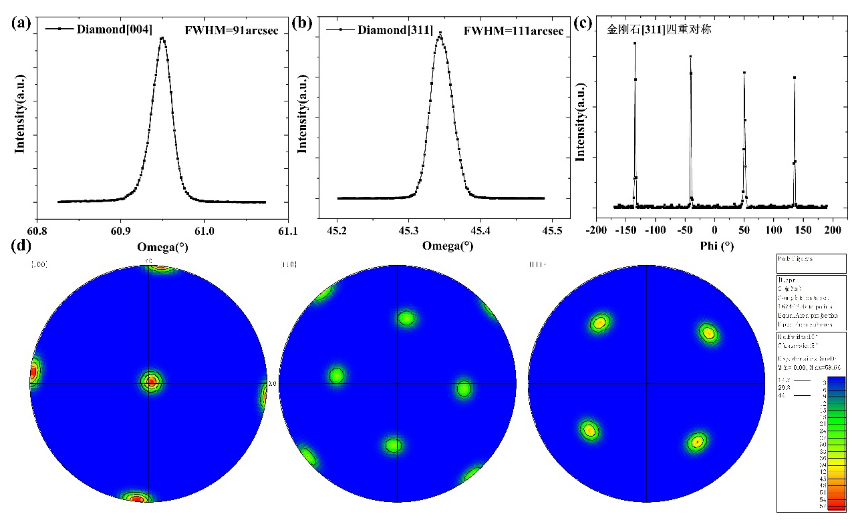

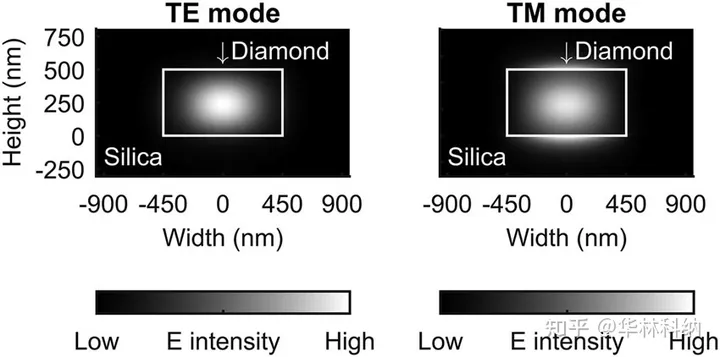

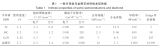

增长:多晶碳可以使用多种化学气相沉积方法生长,包括微波等离子体化学气相沉积、热丝化学气相沉积、射频化学气相沉积和直流电弧喷射化学气相沉积。Ref32如表四所示。然而,MPCVD具有生产高薄膜质量、大基底尺寸、更少的污染和更好的可控性等,是应用最广泛的电子和光学应用技术。

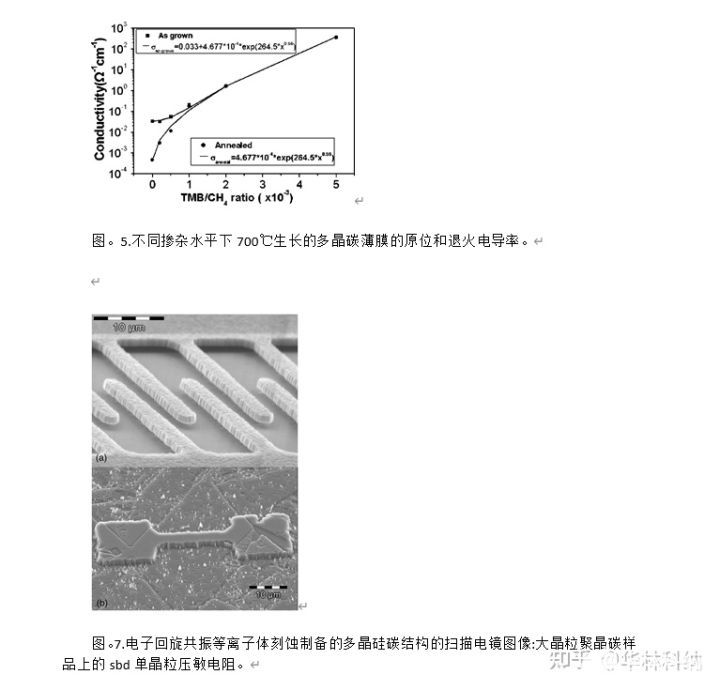

加添加剂:在氢等离子体中生长的化学气相沉积金刚石膜具有薄的氢化表面层,其在暴露于大气后变得导电。在600℃退火可以由于氢解吸效应去除该导电层。在本工作中,研究了多晶碳膜的硼掺杂作为TMB/甲烷气体比、生长温度和生长后温度的函数。

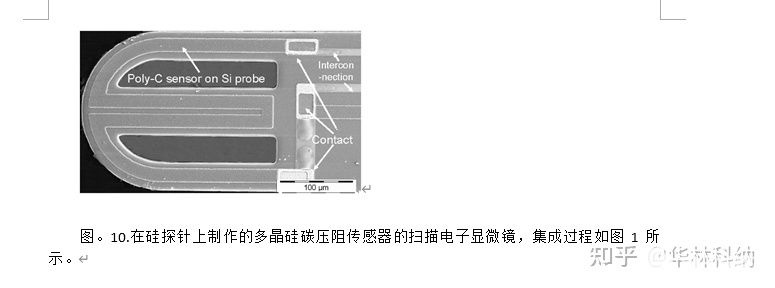

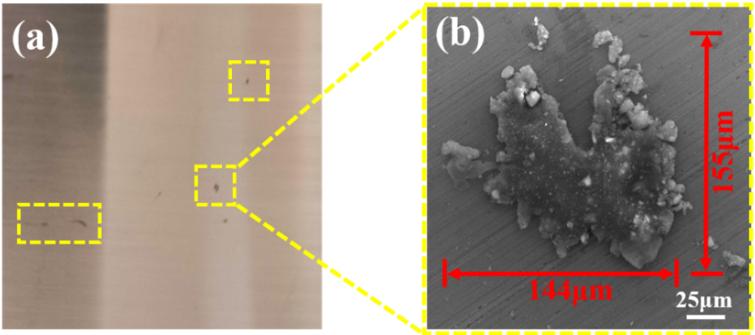

图形:为了在大多数硅基微系统中将聚c器件集成到硅基微系统中,需要使用与典型硅处理相一致的技术来制作聚碳薄膜的图案。由于聚c的湿式蚀刻是不可能的,唯一可用的图案化技术是原位图案化和干式蚀刻。原位图案化技术依赖于选择性播种,这种播种已经使用不同的方法实现,包括使用标准石刻的金刚石粉载光刻胶的DPRd使用二氧化硅作为掩模的选择性播种和直接喷雾书写。

欧姆接触:聚碳和金属薄膜之间的低电阻率欧姆接触对于任何金刚石电子器件的应用都是必不可少的。多晶硅或多晶硅上的金属接触类型不仅取决于金属的选择,还取决于掺杂浓度、退火和其他参数。钛和铬在它们的顶部共沉积金以防止氧化,它们是最广泛使用的金属,因为它们能与聚碳形成碳化物并产生良好的性能退火后的电导率。

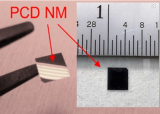

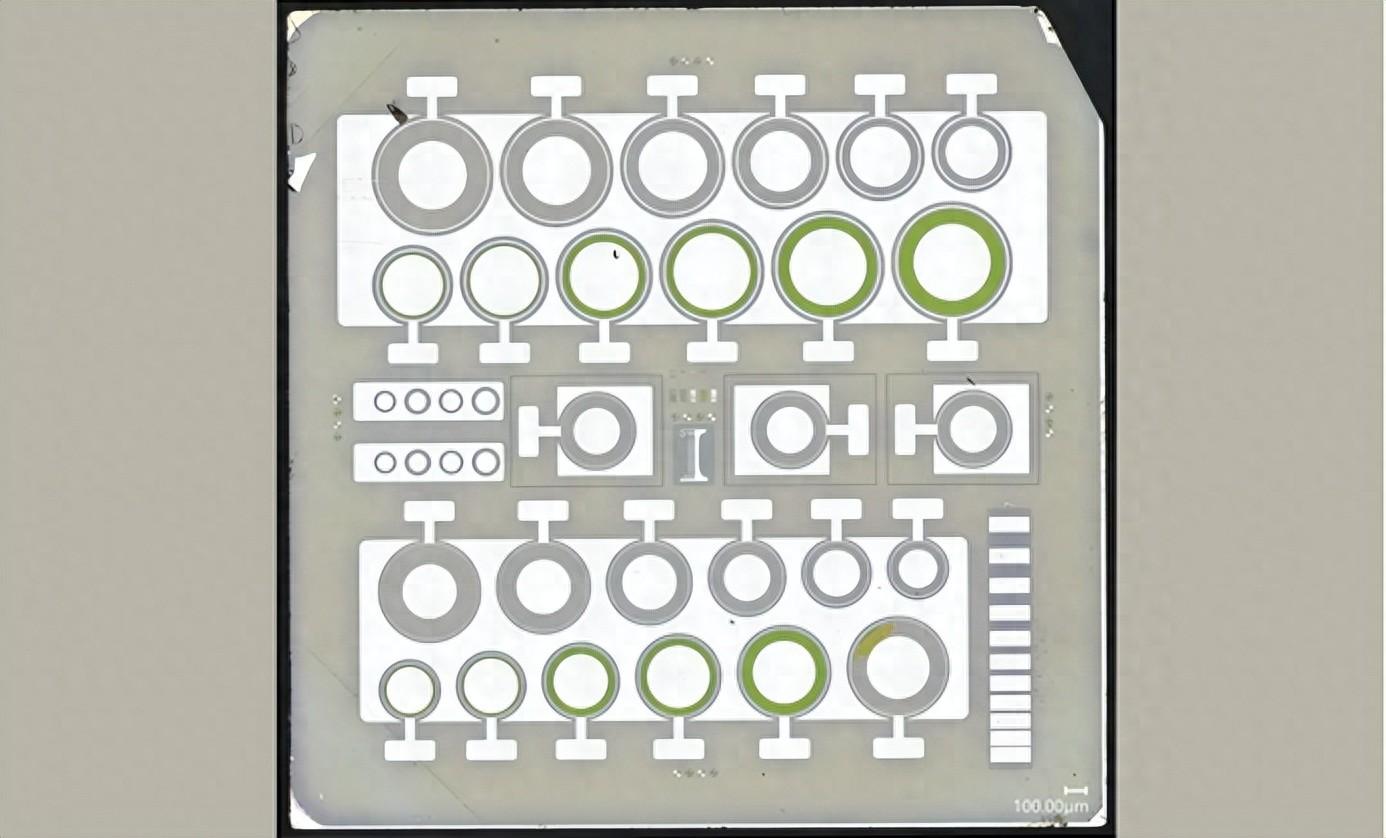

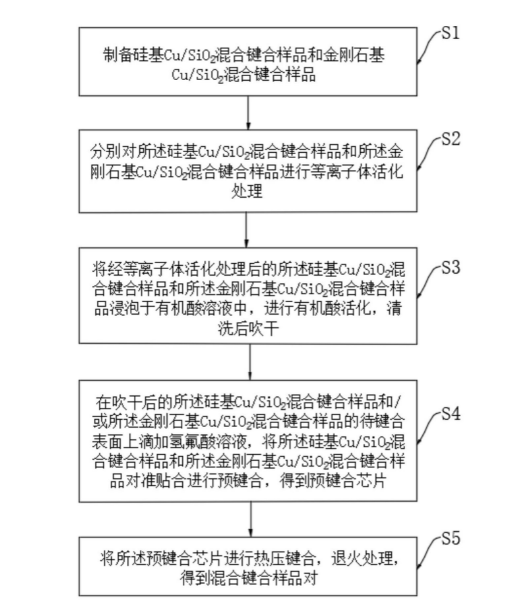

微系统过程集成:由于特殊的籽晶和生长要求,集成是限制多晶碳薄膜传感器发展和应用的重要问题之一。集成电路中的一个常见程序是在多晶硅或金属的上方和下方用电介质层如二氧化硅绝缘有源层,并通过接触孔进行电连接。基于多晶碳压阻位置传感器的设计,我们开发了多晶碳薄膜制造工艺,如图1所示。9将多晶碳技术集成到标准集成电路制造工艺中。该工艺使微米级的连续多晶碳膜与其上下的介电层绝缘,并通过接触孔进行电连接,例如常见的集成电路工艺中的接触孔。这种方法可以在金刚石生长和干蚀刻程序。多晶硅生长温度可以在400℃和900℃之间变化,这取决于多晶硅下面使用的材料。锡含量为1%的铝开关用作互连层,退火后可与碳多晶形成良好的欧姆接触。图10显示了按照图5所示工艺制造的碳多晶压阻位置传感器。在LTO沉积期间,聚碳膜被加热到425℃20分钟,但是所制造的位置传感器的电导率与未构图的膜一致。

结论

本文讲述了在4英寸上实现了IC兼容聚c薄膜的制造工艺。利用DPLW自旋、高功率MPCVD和ECR辅助反应离子蚀刻技术进行氧化硅片。新的DPLW自旋方法可以给出4in以上的均匀播种密度为2X 1010 /cm2。晶圆片。优化后的生长表现出功率高效的大面积增长,比4英寸的厚度变化小于25%。晶圆片。微波等离子体辅助反应离子蚀刻采用六氟化硫/O2/Ar气体,蚀刻速率为80nm/min,与4in相比的变化小于7%。区域的面积。

审核编辑:符乾江

德赢Vwin官网

App

德赢Vwin官网

App

评论