1. 介绍 Vitis是Xilinx新推出的统一软件平台,可实现在 Xilinx 所有芯片(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。Xilinx主要宣传

2020-11-04 12:03:25 5065

5065

从 2019.2 版开始,赛灵思 SDK 开发环境已统一整合到全功能一体化的 Vitis 统一软件平台 中。 马上开始将工程从赛灵思 SDK 移植到 Vitis 吧。 Vivado 工程升级 工程

2020-11-09 16:57:12 2279

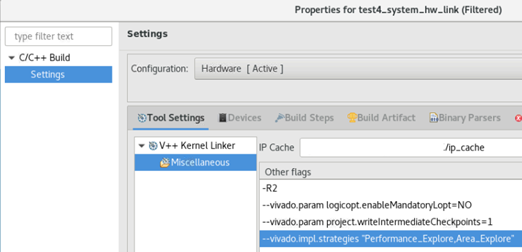

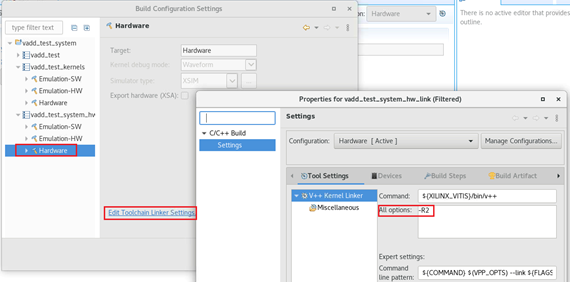

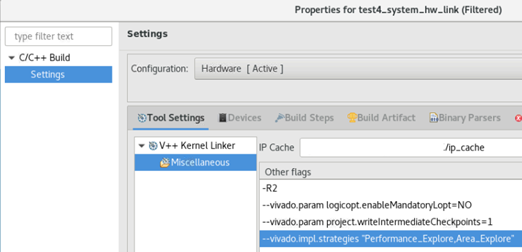

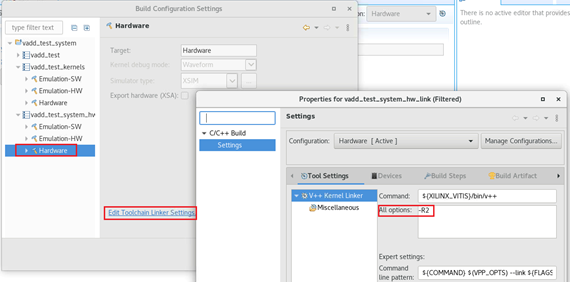

2279 在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分

2022-08-02 08:03:38 1016

1016

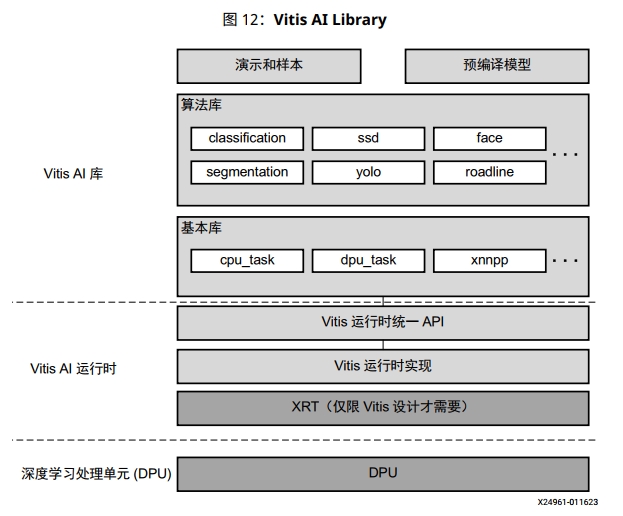

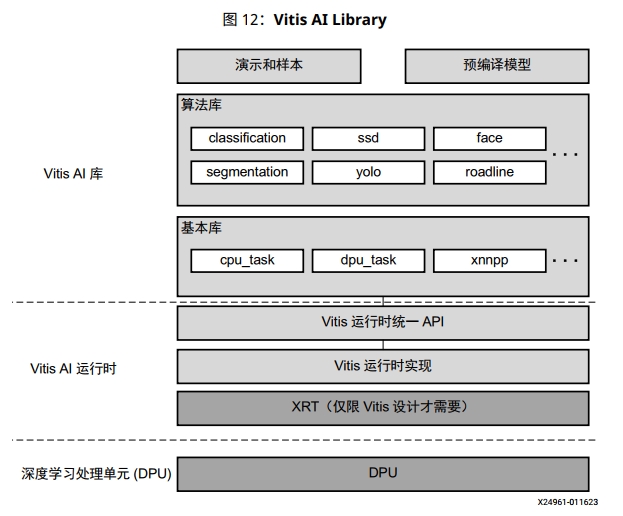

Vitis AI Library是一组高层次库和 API,专为利用 DPU 高效执行 AI 推断而构建。它是基于 Vitis AI运行时利用 Vitis运行时统一 API 来构建的,能够为 XRT 提供完整支持。

2023-10-17 08:23:20 519

519

Vitis AI Model Zone软件平台具备哪些功能?Vitis AI Model Zone软件平台的应用范围包括哪些?

2021-07-09 06:44:28

Vitis准备工程及注意事项

2021-01-25 06:26:20

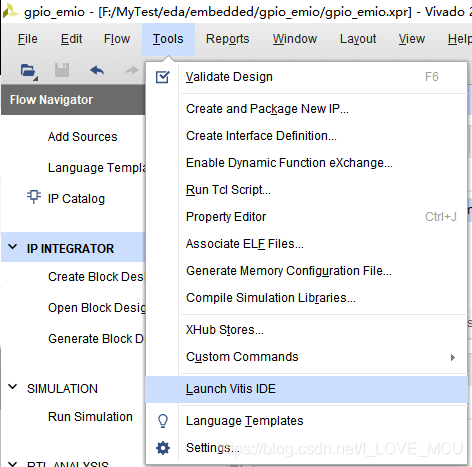

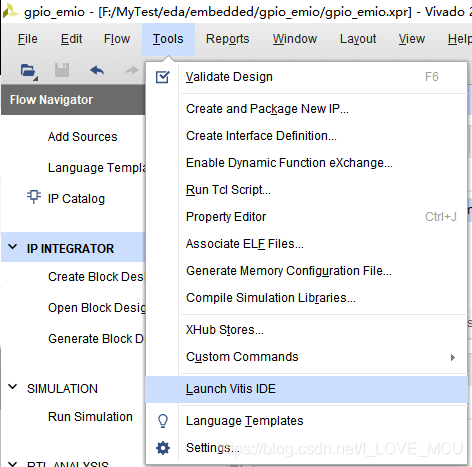

找到vitisvivado->tools->launch vitis ide如果打开失败,说明没有安装vitis,先进行安装安装vitisvivado->help->Add

2020-12-23 17:10:37

在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2021-02-04 07:09:50

RTC介绍中断介绍Vitis程序编写

2021-02-25 07:39:08

vitis和vivado有什么区别和联系呢

2023-10-16 07:55:35

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

,可以使用sp标志和slr标志指定 conn_u200.cfg 配置文件中的DDR和SLR连接方式,按照经验来说,注释掉sp标志和slr标志可以达到更高的时钟频率,但生成的DDR和SLR连接方式不固定

2023-12-31 21:31:32

求助各位高手:如何在OrCAD 16.3中, 设定Wire的宽度和颜色?而不是Line的颜色和宽度.

2012-07-20 20:32:08

源文件,之后Clean,再之后Build(Ctrl + B)。 注:中间会弹出来一个错误的提示,不用理会,等待工程编译完成,错误提示就不存在了。 更改目录后vitis工程需要重新加载平台 在建

2021-01-15 16:46:02

,校验通过 ,但是串口输出停留在 start kernel ... led灯也正常闪烁, 怀疑是kernel中console 配置错误,但是在board-dm385ipnc.h中未找到serial相关的 端口 频率 gpio使能等配置,请问具体配置一般在什么文件下面?

2018-06-23 06:07:54

指针地址调用entry函数,但asm文件指向重启函数。需求:请简要说明如何在移植的main.c中初始化kernel和系统

2020-11-19 12:03:44

:在CentOS 7 和CentOS 8中的操作方式有些差异,需要在配置前注意系统版本,此处以CentOS-7.9为例进行说明。

1. 系统软件安装

Vitis需要一些软件或者依赖库,优先解决该

2023-08-27 21:22:34

翻译成计算机文字的过程;即,针对印刷体字符,采用光学的方式将纸质文档中的文字转换成为黑白点阵的图像文件,并通过识别软件将图像中的文字转换成文本格式,供文字处理软件进一步编辑加工的技术。如何除错或利用

2023-10-16 23:25:11

一、基础环境

硬件:KV260视觉入门套件

摄像头:海康720P USB摄像头(因为部署Vitis AI之后懒得poweroff插MIPI camera了,直接USB上)

软件:Ubuntu

2023-09-10 13:15:24

量化

七、Vitis AI 通过迁移学习训练自定义模型

八、Vitis AI 将自定义模型编译并部署到KV260中

铺垫

Vitis AI 是什么?

Vitis AI 是赛灵思公司推出的一款综合 AI

2023-10-14 15:34:26

本文将介绍如何使用Vitis-AI加速YOLOX模型实现视频中的目标检测,并对相关源码进行解读。由于演示的示例程序源码是Vitis-AI开源项目提供的,本文演示之前会介绍所需要的准备工作。演示之后

2023-10-06 23:32:47

都已编译到预构建的 Vitis AI 开发板镜像中。您可直接运行示例。如有新程序,请在主机侧对其进行编译并将可执行程序复制到目标。

1. 使用 scp 命令将

2023-09-26 16:22:43

是一种模型,旨在同时执行自动驾驶场景中的不同任务,同时实现优异的性能和效率。这些任务包括对象检测、分割、车道检测、可行驶区域分割和深度估算,这些都是自动驾驶感知模块的重要组成部分。

三、代码实现

2023-09-26 16:43:01

车牌的图像进行分析,最终截取出只包含车牌的一个图块的过程。这个步骤的主要目的是降低在车牌识别过程中的计算量,如果直接对原始的图像进行车牌识别,会非常的慢,因此需要检测的过程。

车牌识别是一种通过计算机

2023-09-26 16:28:10

。

三、ADAS目标识别

Vitis AI 提供L了许多实例,其中包括一个ADAS目标识别的demo,在Vitis-AI/examples/vai_runtime/adas_detection中

2023-09-27 23:21:32

%BD-Vitis-AI-Library

从步骤3下载

vitis-ai-runtime-3.0.0.tar.gz

安装位置为/usr/lib 和 /usr/include

这里面包含了所有需要的库。在/usr/bin中还有

2023-08-27 23:35:48

本文首先将会对Vitis统一软件平台和Vitsi AI进行简单介绍,然后介绍如何在KV260上部署DPU镜像,最后在KV260 DPU镜像上运行Vitis AI自带的图像分类示例。通过本文,你将会

2023-09-10 23:01:02

1、使用Vitis HLS创建属于自己的IP高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD

2022-09-09 16:45:27

。3.Vitsi 开始调试在 Vivado 2019.2 中启动 Vitis 的方式 与我现在用的 vivado 2017.4 有些不一样,当然这一点也不清楚是在 2019.2 版本中做的改变还是在2018版本

2020-03-06 22:59:12

里面U-BOOT的版本为“u-boot-2013.01.01-psp06.00.00.00”,看U-BOOT里面设定MPU和DDR的频率的时候,有几点疑问:

1. 在clock.c的文件中(路径

2018-06-21 05:06:58

我希望在设定的扫描上下时间以对数步长从开始扫描到停止频率。我怎么能够? 以上来自于谷歌翻译 以下为原文I wish to sweep from a start to a stop

2019-07-03 09:48:15

如何在Matlab编写一个S函数设定值是把图2的constant代替成图1的函数拜托了~~

2017-05-08 16:37:05

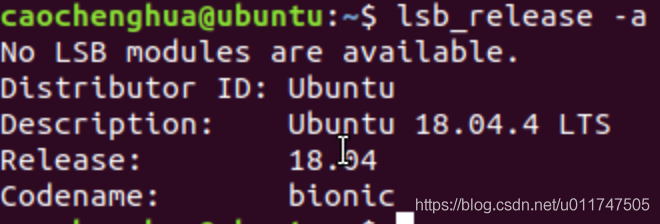

如何在VMware中安装ubuntu 16.04如何安装Vitis AI几个常见的docker指令

2021-02-24 06:24:00

如何在uboot节点提升CPU频率呢?uboot的启动log的信息该怎样去修改呢?

2021-12-29 06:39:52

亲爱的,我想知道如何在动量中为导体表面分配频率相关的表面阻抗。我所拥有的是存储在文件“Re(Zs)和Im(Zs)与频率”中的表面阻抗Zs的列表值,其中Zs是使用更精确模型在别处计算的表面阻抗。谢谢

2019-03-11 06:28:37

小弟新手,求教AD7606例程里数据的采样频率是如何设定的

2019-07-09 08:44:55

我尝试将RTT移植到Vitis2019.2工程中,硬件平台为Zynq Ultrascale+ MPSoC ZU3EG 的自制板子。我已经移植了RTT源码/bsp/zynqmp-r5-axu4ev

2022-09-15 14:11:28

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

如何在编程过程中修改NuMicro®系列芯片的外部晶体(H XT)的设定值?

2020-11-27 06:00:02

如何在PCB下设定不同的铺铜区域安全间距及切铜,有借鉴意义。

2016-12-16 21:54:48 0

0 在这个简短的视频中,您将学习如何在OpenCL 2.0中实现Sierpinski Carpet Kernel。

2018-11-07 06:20:00 2917

2917 在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。

2020-09-13 10:04:19 5961

5961

Vitis 加速库 Vitis 统一软件平台包括一组广泛的、性能优化的开源库,这些库提供了即开即用的加速功能,并且对现有应用实现最小化代码更改或零更改。 常见的 Vitis 加速库(用于数学、统计

2020-11-23 15:45:07 1412

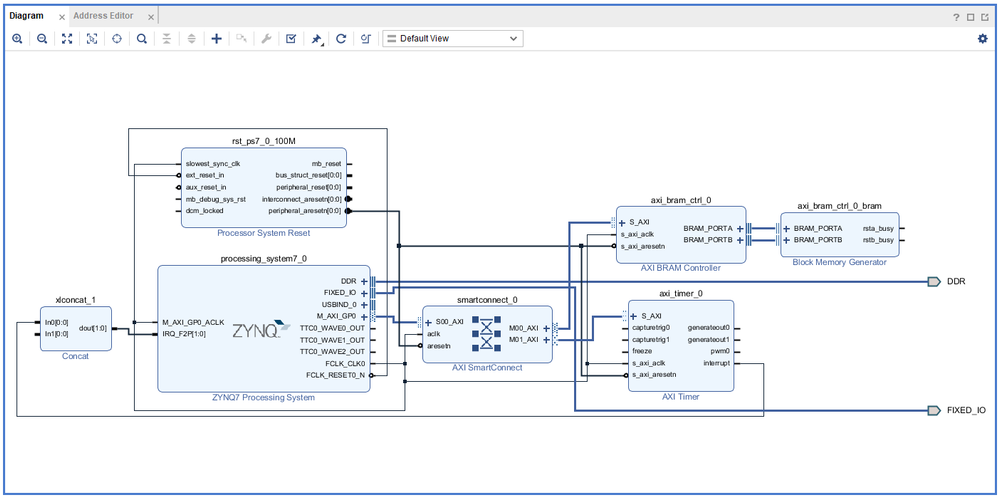

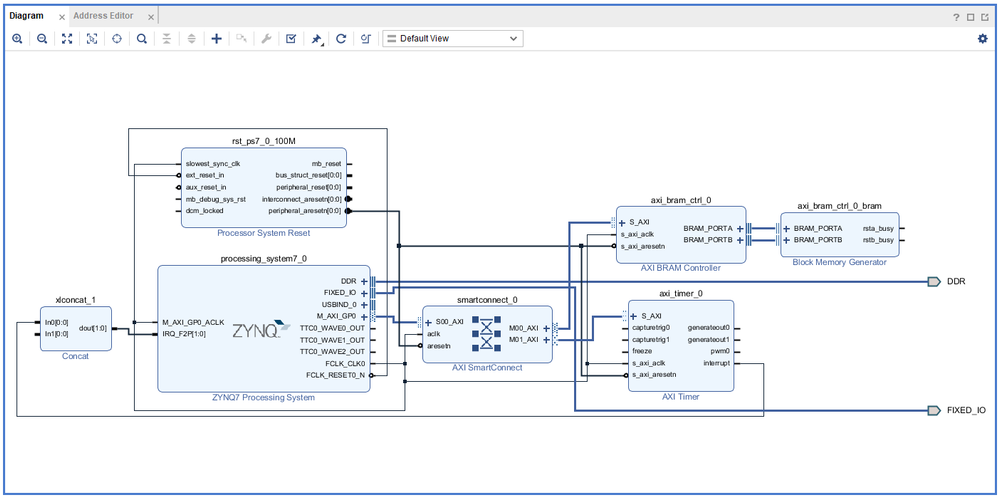

1412 Linux嵌入式设计中最基本的任务之一是创建用户应用程序。 在本篇博文中,我们将探讨如何在 Vitis 中使用 UIO 驱动框架创建简单的 Linux 用户应用。 1 硬件设计 本次

2020-11-20 14:05:34 3840

3840 Vitis迎来了版本更新,Vitis 2020.2 带来更加快捷智能的使用体验。首次引入Vitis™AI Engine( AI引擎)编译器,并提供多个加速功能。

2020-12-09 09:10:25 1284

1284 这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis 中将所有这些工程封装在一起。 在 Vitis 中加速软件

2020-12-26 10:20:54 2465

2465

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3057

3057

赛灵思公司(Xilinx)推出Vitis——这是一款统一软件平台,可以让包括软件工程师和AI科学家在内的广大开发者都能受益于硬件灵活应变的优势。历经5年、投入总计1000人打造而成,Vitis统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。

2022-07-25 18:07:14 13520

13520

在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2022-07-25 18:03:30 3090

3090

第一个Xilinx Vitis IDE入门helloworld程序

2022-07-25 17:37:23 993

993

赛灵思公司(Xilinx)推出Vitis——这是一款统一软件平台,可以让包括软件工程师和AI科学家在内的广大开发者都能受益于硬件灵活应变的优势。历经5年、投入总计1000人打造而成,Vitis统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。

2021-01-31 07:49:37 16

16 本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2021-01-31 08:12:02 8

8 在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2021-02-21 06:48:51 17

17 本博文介绍Vitis AI1.1 系列软件安装教程。

2021-03-01 10:36:55 5

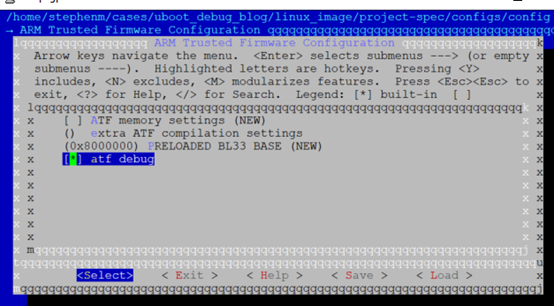

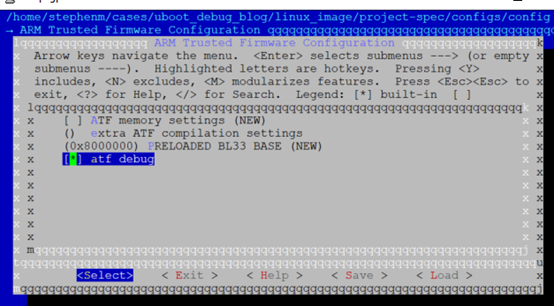

5 在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。 本篇博文乃是系列博文中

2021-06-01 15:35:45 2709

2709

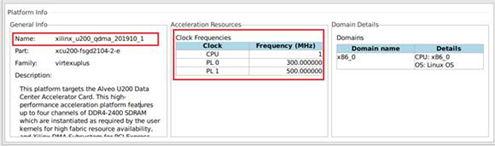

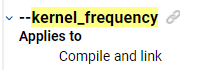

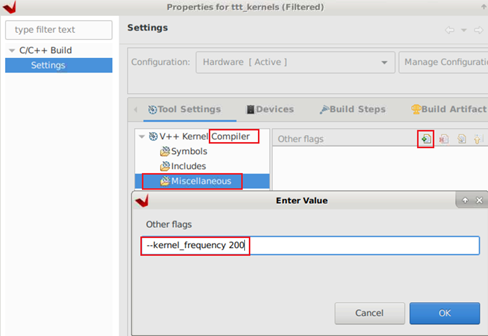

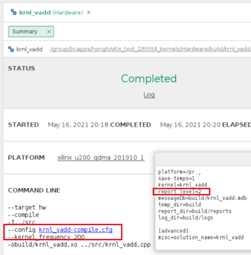

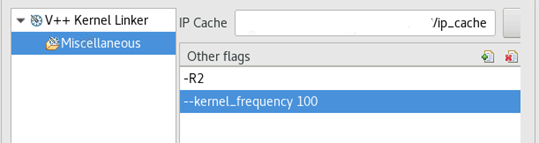

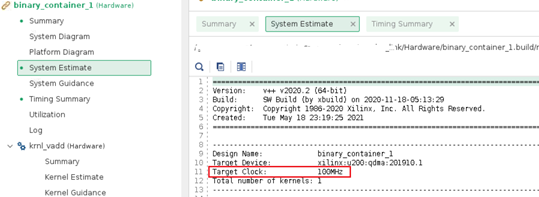

在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率。 以 xilinx_u200_qdma_201910_1 平台

2021-06-12 14:19:00 36855

36855 本文来自赛灵思高级产品应用工程师 Hong Han Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些

2021-06-18 10:15:14 36578

36578 在Vitis 统一软件平台中使用v++ -link命令,可以把各种类型Kernel(C, C++, OpenCL C, 以及 RTL)的对象文件(.XO)整合到目标平台中,最终生成器件的二进制文件

2021-07-28 10:12:47 1758

1758

Q1 HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗? 这下图中,将xo文件作为源文件import时,xo文件显示

2021-08-26 17:03:52 2220

2220 Vitis Vision库是OpenCV和Vision功能的加速库,可在Vitis环境中使用,这些库的L1目录是示例设计。为了适应各种用户环境,从2020.1版本开始,Xilinx不再

2022-02-16 16:21:38 2015

2015

对Kernel进行性能分析需要对其进行仿真,同时还要用到Vitis Analyzer。为便于说明,我们以一个简单的Vitis工程为例。这个工程中有两个kernel,相应的代码如下图所示

2022-03-15 15:30:23 1288

1288 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 生成的 device tree 里 axigpio core 的 driver 是 xilinx driver,我们需要把它替换为我们生成的 kernel module 的 drivername

2022-06-30 09:48:49 538

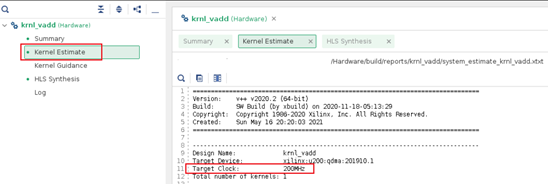

538 在Kernel Estimate报告中,可以看到,Target Clock已经按要求设置成200Mhz. 说明 Vitis_HLS是按照200Mhz的要求来综合Kernel的代码的.

2022-07-01 09:52:53 36129

36129 您是否想创建自己带有 AXI4-Lite 接口的 IP 却感觉无从着手?本文将为您讲解有关如何在 Vitis HLS 中使用 C 语言代码创建 AXI4-Lite 接口的基础知识。

2022-07-08 09:40:43 1232

1232 HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

2022-08-03 11:20:26 2662

2662

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

2022-08-02 10:26:41 711

711

Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些Kernel的逻辑会在分布在DFX设计的动态区域。

2022-08-02 09:38:37 36376

36376

在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。

2022-08-02 10:14:59 2733

2733

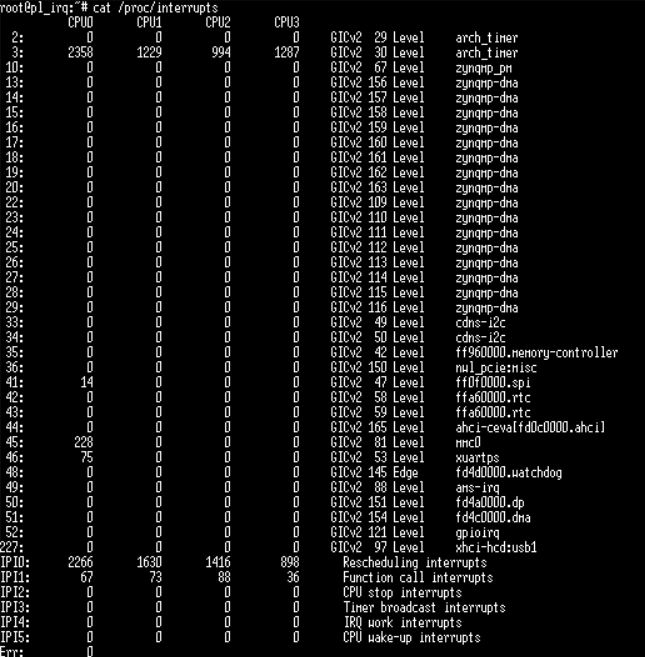

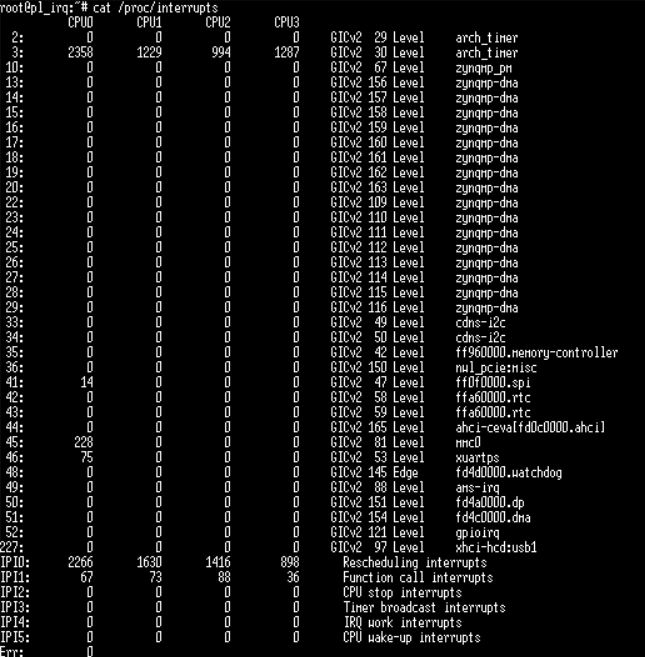

有时我们需要为官方 IP 或者自己创建的 IP 生成 kernel module,然后在 linux kernel space 里使用 kernel module 来控制这个 IP。如果要使用 IP 中断,我们需要在 kernel module 代码里获取设备中断并建立中断服务程序。

2022-08-02 11:35:23 421

421

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP

2022-08-02 09:43:05 579

579

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2856

2856 电源技巧:如何在隔离式电源中测量频率响应

2022-11-04 09:51:39 0

0 德赢Vwin官网

网站提供《Zynq上使用Vitis的双ARM Hello World.zip》资料免费下载

2022-12-14 10:15:40 0

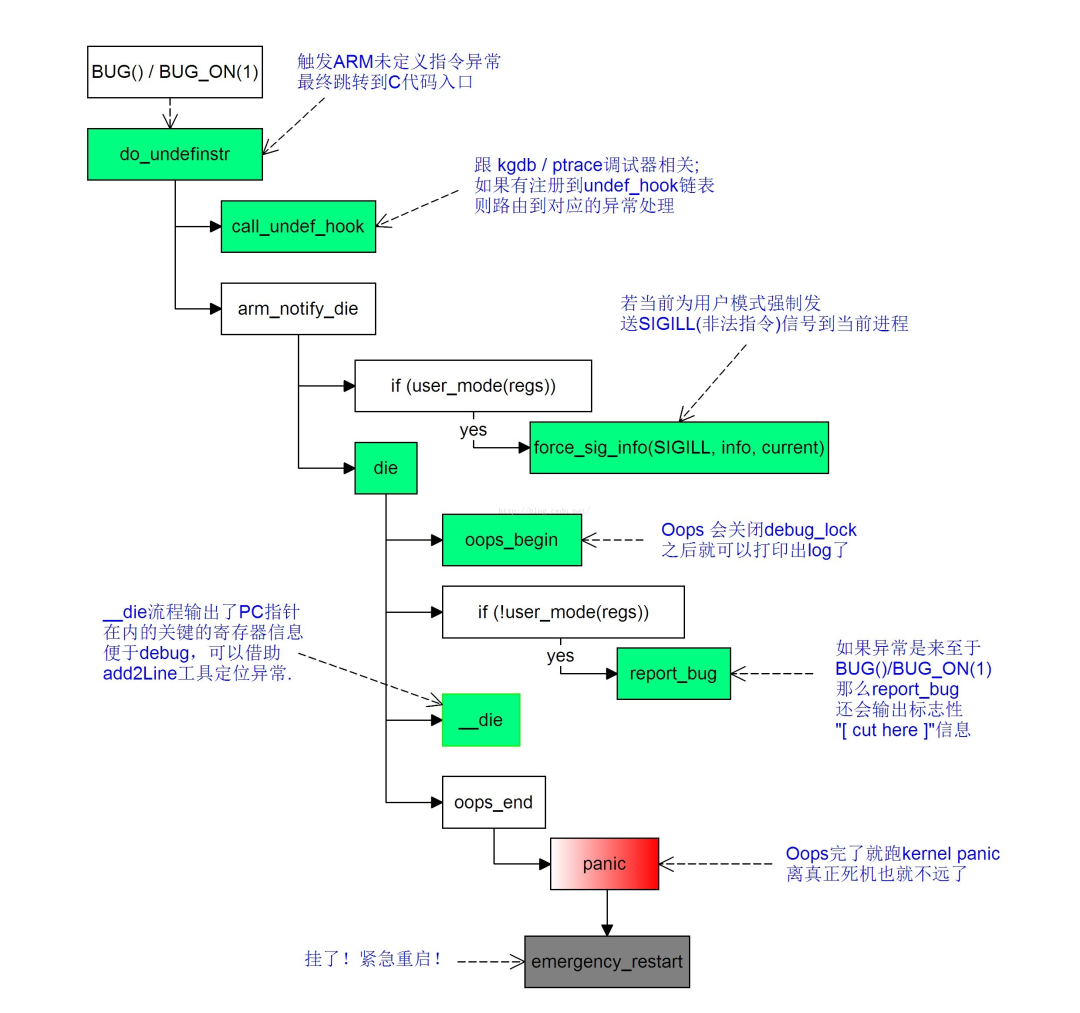

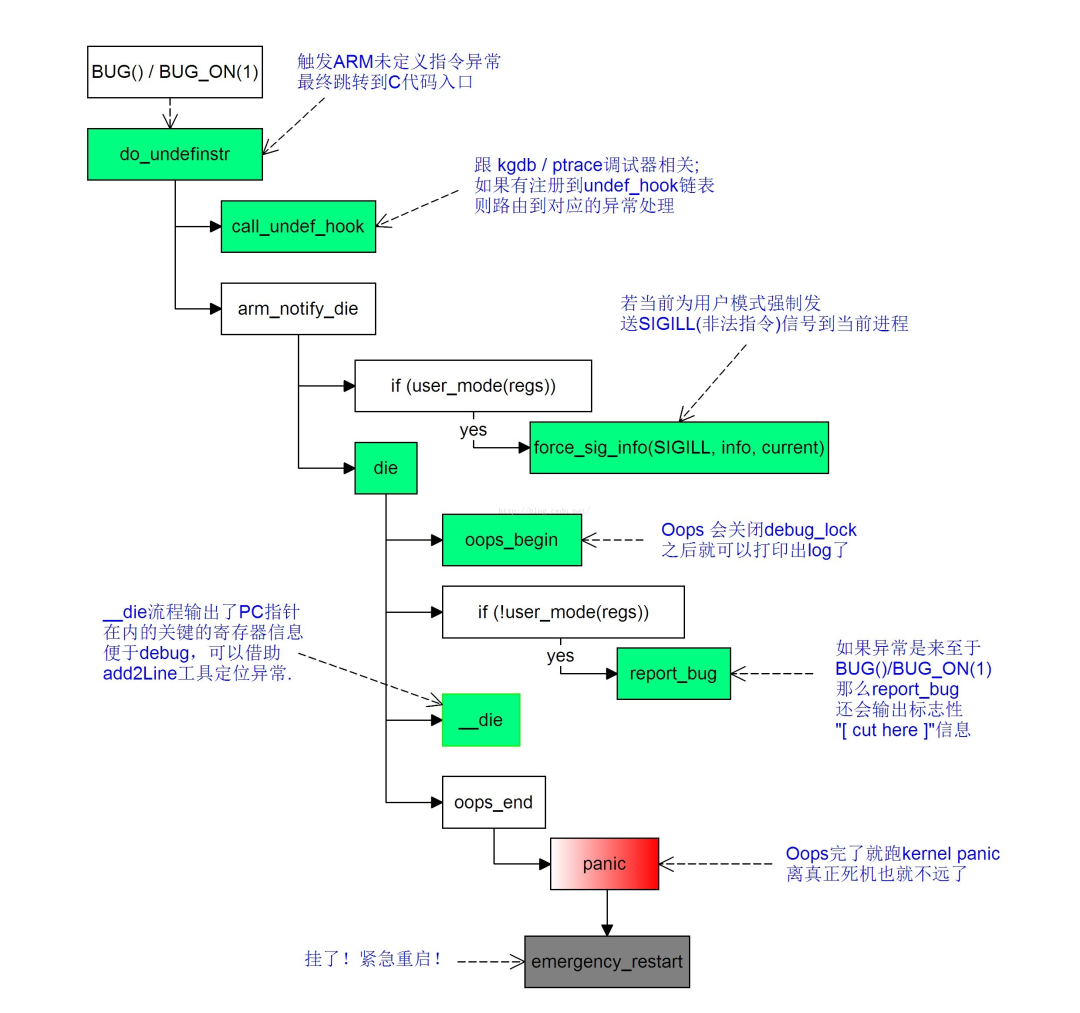

0 我们在项目开发过程中,很多时候会出现由于某种原因经常会导致手机系统死机重启的情况(重启分Android重启跟kernel重启,而我们这里只讨论kernel重启也就是 kernel panic 的情况

2023-01-19 16:14:00 701

701

电机控制中载波频率是非常重要的因素,其值不能设定太高,同样也不能设定太低,通常载波频率设定与五个因素有关:基波频率、硬件限制、谐波电流、内部软件的实现、功率模块温升,这期主要讲讲与这几个因素有关的原因。

2023-01-13 14:58:50 6961

6961

AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 652

652

在本快速入门演示中,将探讨如何在 Vitis 中使用 Git 集成以及如何使用团队操作来共享 Vitis 工程。

2023-05-12 15:01:00 566

566

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

2023-08-16 10:26:16 546

546

本文首先将会对Vitis统一软件平台和Vitsi AI进行简单介绍,然后介绍如何在KV260上部署DPU镜像,最后在KV260 DPU镜像上运行Vitis AI自带的图像分类示例。通过本文,你将会

2023-09-12 10:02:08 968

968

德赢Vwin官网

网站提供《Vitis AI优化器指南.pdf》资料免费下载

2023-09-14 11:04:38 0

0 德赢Vwin官网

网站提供《Vitis Model Composer用户指南.pdf》资料免费下载

2023-09-14 09:59:15 0

0 德赢Vwin官网

网站提供《Vitis Model Composer教程.pdf》资料免费下载

2023-09-14 09:52:29 0

0 德赢Vwin官网

网站提供《Vitis AI用户指南.pdf》资料免费下载

2023-09-13 15:00:21 0

0 德赢Vwin官网

网站提供《Vitis HLS移植指南.pdf》资料免费下载

2023-09-13 09:21:12 0

0 德赢Vwin官网

网站提供《Vitis AI库用户指南.pdf》资料免费下载

2023-09-15 10:46:57 0

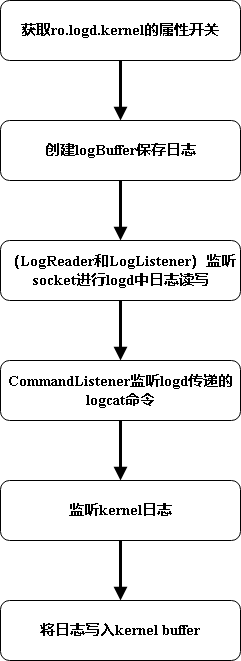

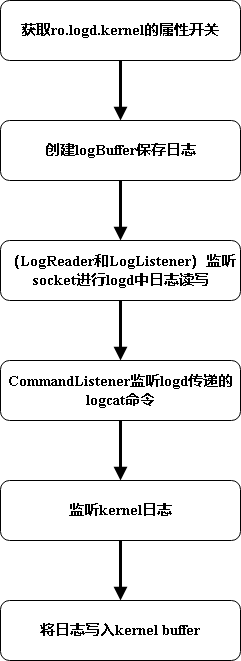

0 kernel日志写入logd介绍 通过logcat命令获取kernel日志比较特殊,故作为一个例子进行梳理。 2.3.1 整体流程 2.3.2 命令打印kernel日志 通过logcat

2023-11-23 17:11:17 208

208

AMD Vitis 软件平台是一款开发环境,主要用于开发包括 FPGA 架构、Arm 处理器子系统和 AI 引擎在内的设计。Vitis 工具与 AMD Vivado ML 设计套件相结合,可为

2023-12-20 10:00:02 154

154

德赢Vwin官网

网站提供《Vitis AI用户指南.pdf》资料免费下载

2024-01-03 10:51:52 0

0

德赢Vwin官网

App

德赢Vwin官网

App

评论