完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

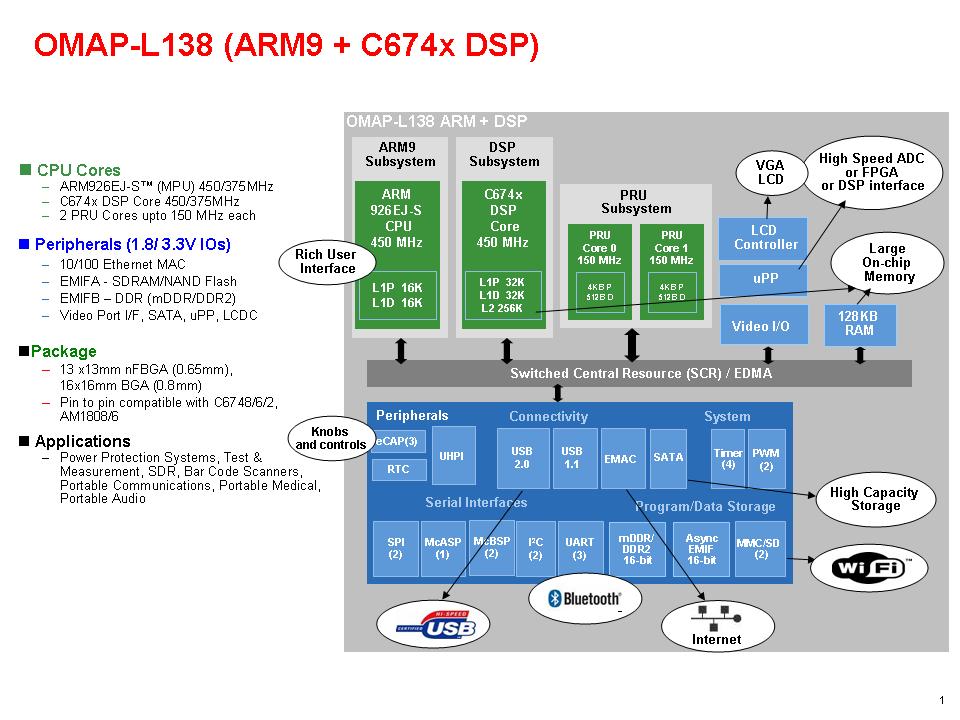

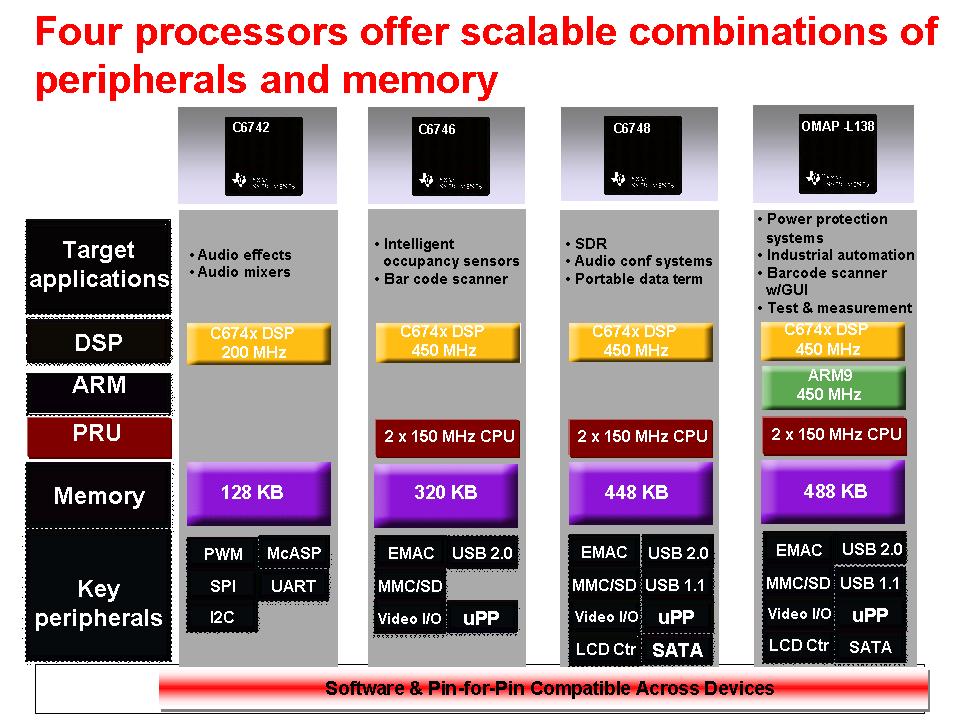

OMAP-L138 C6000 DSP+ARM 处理器 是一款低功耗 应用 处理器,该处理器基于 ARM926EJ-S 和 C674x DSP 内核。该处理器 与其他 TMS320C6000™ 平台 DSP 相比,功耗要小很多。

凭借这款器件,原始设备制造商 (OEM) 和原始设计制造商 (ODM) 能够充分利用全集成混合处理器解决方案的灵活性,迅速将兼具稳健操作系统、丰富用户接口和高处理器性能的器件推向市场。

此器件采用双内核架构(包括一个高性能的 TMS320C674x DSP 内核和一个 ARM926EJ-S 内核),实现了 DSP 与精简指令集计算机 (RISC) 技术二者优势的完美融合。

ARM926EJ-S 是一款 32 位 RISC 处理器内核,可执行 32 位或 16 位指令和处理 32 位、16 位或 8 位数据。该内核采用流水线结构,因此处理器和存储器系统的所有部件能够连续运行。

ARM9 内核配有协处理器 15 (CP15)、保护模块以及具有页表缓冲区的数据和程序存储器管理单元 (MMU)。ARM9 内核配有独立的 16KB 指令缓存和 16KB 数据缓存。这两个缓存均与虚拟索引虚拟标签 (VIVT) 4 路相连。ARM9 内核还配有 8KB 的 RAM(向量表)和 64KB 的 ROM。

该器件的 DSP 内核采用基于 2 级缓存的架构。第 1 级程序缓存 (L1P) 是一个 32KB 的直接映射缓存,第 1 级数据缓存 (L1D) 是一个 32KB 的 2 路组相连缓存。第 2 级程序缓存 (L2P) 包含 256KB 的存储空间,由程序空间和数据空间共享。L2 存储器可配置为映射存储器、缓存或二者的组合。尽管 ARM9 和系统内的其他主机均可访问 DSP L2,但还是额外提供了一个 128KB 的 RAM 共享存储器给其他主机使用,从而避免对 DSP 性能产生影响。

对于支持安全功能的器件,TI 的基本安全启动可为用户保护自主知识产权并防止外部实体修改用户开发的算法。该安全启动流程从一个基于硬件的“信任根”开始,确保代码从一个已知安全的位置开始执行。默认情况下会锁定 JTAG 端口以防止仿真和调试攻击;不过,在应用开发期间的安全启动过程中可以使能 JTAG 端口。启动模块存储在外部非易失性存储器(例如,闪存或 EEPROM)中时处于加密状态,在安全启动期间被装载时会进行解密和验证。加密和解密程序会保护用户 IP,使用户能够安全地设置系统并使器件采用已知可信任的代码开始运行。

基本安全启动使用 SHA-1 或 SHA-256 以及 AES-128 来验证启动映像。另外,基本安全启动使用 AES-128 进行启动映像加密。安全启动流程采用多层加密机制,不但可以保护启动过程,而且能够安全地升级启动和应用软件代码。该器件使用 1 个 128 位的器件专用密钥来保护用户密钥,该 128 位密钥由经过 NIST-800-22 认证的随机数发生器生成,并且仅对该器件是已知的。当需要更新时,客户可使用密钥创建一个新的加密映像。之后,器件可通过外部接口(例如,以太网)来获取该映像并覆盖现有代码。有关支持的安全 特性 或 TI 基本安全启动的更多详细信息,请参见《TMS320C674x/OMAP-L1x 理器安全用户指南》。

外设集包括:1 个具有管理数据输入/输出模块 (MDIO) 的 10Mbps/100Mbps 以太网介质访问控制器 (EMAC);1 个 USB2.0 OTG 接口;1 个 USB1.1 OHCI 接口;2 个 I2C 总线接口;1 个具有 16 个串行器和 FIFO 缓冲器的多通道音频串行端口 (McASP);2 个具有 FIFO 缓冲器的多通道缓冲串行端口 (McBSP);2 个支持多片选的串行外设接口 (SPI);1 个可配置的 16 位主机端口接口 (HPI);多达 9 组通用输入/输出 (GPIO) 引脚(每组包含 16 个引脚,每个引脚均支持可编程的中断和事件生成模式,并且支持与其他外设复用);3 个 UART 接口(均支持RTS和CTS);2 个增强型高分辨率脉宽调制器 (eHRPWM) 外设;3 个 32 位增强型捕捉 (eCAP) 模块外设(可配置为 3 个捕捉输入或 3 个 APWM 输出);2 个外部存储器接口(一个是用于慢速存储器或外设的异步 SDRAM 外部存储器接口 (EMIFA),另一个是高速 DDR2/移动 DDR 控制器)。

EMAC 为器件和网络之间提供了一个高效接口。无论是在半双工模式还是全双工模式下,EMAC 都支持 10Base-T 和 100Base-TX 或者 10Mbps 和 100Mbps。此外,该器件还提供了一个针对 PHY 配置的 MDIO 接口。EMAC 支持 MII 和 RMII 接口。

串行 ATA (SATA) 控制器提供了一个连接至海量数据存储器件的高速接口。SATA 控制器支持 SATA I (1.5Gbps) 和 SATA II (3.0Gbps)。

通用并行端口 (uPP) 提供了一个连接至多种类型的数据转换器、FPGA 或其他并行器件的高速接口。uPP 的两个通道均支持可编程的数据宽度,可编程范围为 8 位至 16 位。另外,还支持单倍数据速率或双倍数据速率传输以及 START、ENABLE 和 WAIT 信号,用以控制各类数据转换器。

视频端口接口 (VPIF) 提供了灵活的视频 I/O 端口。

丰富的外设集提供了控制外设以及与外部处理器进行通信的功能。如需了解每个外设的详细信息,请参见本文档中的有关章节以及相关外设参考指南。

该器件配有一套完整的 ARM9 和 DSP 开发工具。这套工具包括 C 语言编译器,用于简化编程和调度过程的 DSP 汇编优化器以及用于查看源代码执行的 Windows®调试器接口。

All trademarks are the property of their respective owners.

| Applications |

| Operating Systems |

| Arm CPU |

| Arm MHz (Max.) |

| DSP |

| DSP MHz (Max) |

| EMAC |

| Display Options |

| Video Port (Configurable) |

| DRAM |

| Operating Temperature Range (C) |

| USB |

| SPI |

| I2C |

| UART (SCI) |

| On-Chip L2 Cache/RAM |

| Other On-Chip Memory |

| SATA |

| Package Size: mm2:W x L (PKG) |

| OMAP-L138 | OMAP-L132 |

|---|---|

| Communications and Telecom Consumer Electronics Energy Industrial Medical |

Communications and Telecom Consumer Electronics Energy Industrial Medical |

| Linux SYS/BIOS |

Linux SYS/BIOS |

| 1 ARM9 | 1 ARM9 |

| 456 | 200 |

| 1 C674x | 1 C674x |

| 456 | 200 |

| 10/100 | 10/100 |

| 1 | 0 |

| 1 | 0 |

| DDR2 LPDDR |

DDR2 LPDDR |

| -40 to 105 -40 to 90 0 to 90 |

-40 to 105 0 to 90 |

| 2 | 1 |

| 2 | 2 |

| 2 | 2 |

| 3 | 3 |

| 256 KB (DSP) | 256 KB (DSP) |

| 128 KB | 128 KB |

| 1 | 0 |

| 361NFBGA: 169 mm2: 13 x 13(NFBGA) 361NFBGA: 256 mm2: 16 x 16(NFBGA) |

361NFBGA: 256 mm2: 16 x 16(NFBGA) |