完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

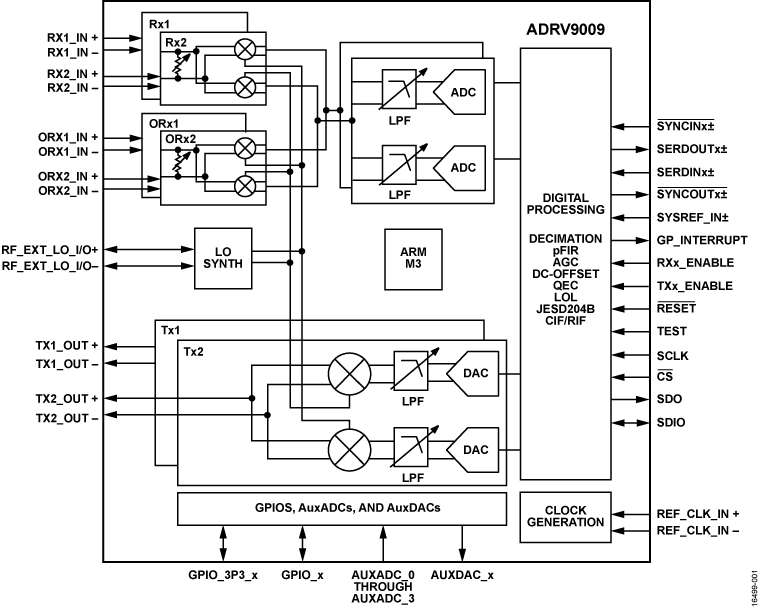

ADRV9009 是一款高度集成的射频 (RF) 捷变收发器,提供双通道发射器和接收器、集成式合成器和数字信号处理功能。此 IC 可实现 3G 和 4G 宏蜂窝 TDD 基站应用所需的多种高性能低功耗组合。

接收路径包括两个具有一流动态范围的独立式宽带宽直接转换接收器。该器件还支持宽带宽分时观察路径接收器,供在 TDD 应用中使用。完整的接收子系统包括自动和手动衰减控制、直流失调矫正、正交误差校正 (QEC) 以及数字滤波,因此数字基带中不再需要这些功能。还集成了多种适用于 PA 和射频前端控制的辅助功能,例如 ADC、DAC 和 GPIO。

除了自主 AGC 外,它还具有灵活的外部增益控制模式,可在动态设置系统级增益的过程中实现出色的灵活性。

接收的信号通过一组四个高动态范围连续时间 Σ-Δ ADC 进行数字化处理,这些 ADC 具有固有的抗混叠特性。直接转换架构不受带外镜像混合影响,由于不存在混叠,因而与传统 IF 接收器相比,放宽了 RF 滤波器的要求。

发射器采用一种创新的直接转换调制器,可以实现高调制精度和极低的噪声。

观察路径包括一个具有一流动态范围的宽带宽直接转换接收器。

发射器采用一种创新的直接转换调制器,可以实现高调制精度和极低的噪声。

完全集成的锁相环 (PLL) 为发射器和接收器信号路径提供高性能、低功耗分数 N 射频合成。另有一个合成器生成转换器、数字电路和串行接口所需的时钟。已采取特别预防措施以提供高性能基站应用所要求的隔离。集成了所有压控振荡器 (VCO) 和环路滤波器元件。

高速 JESD204B 接口支持高达 12.288 Gbps 的线速,因此在最宽带宽模式下,每个发射器有两个线路,每个接收器有一个线路。此接口还支持适用于较低带宽的交错模式,因而将高速数据接口总线数减少到了一个。支持固定和浮点数据格式。浮点格式可使内部 AGC 对解调器器件不可见。有关该格式的详细信息,请参阅器件用户指南。

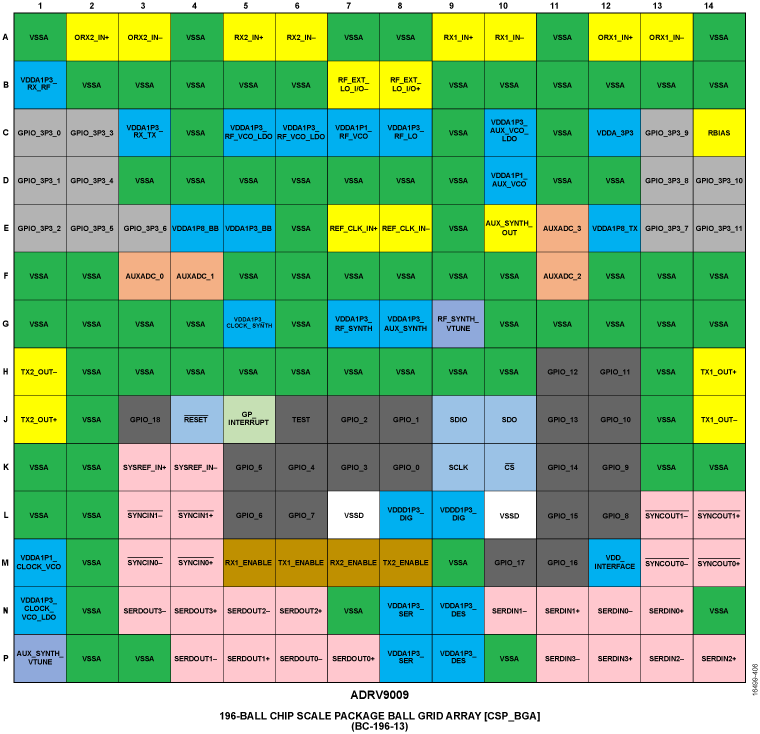

ADRV9009 的内核可以直接由 1.3 V 和 1.8 V 稳压器供电,并通过标准 4 线串行端口进行控制。包括了全面的节电模式,以便在正常使用过程中最大限度地减小功耗。ADRV9009 采用 12 mm × 12 mm、196 球芯片级球栅阵列 (CSP_BGA) 封装。