德赢Vwin官网

网: 本文主要为大家浅析Altera公司 28nm Stratix V FPGA。Altera公司公布了其28nm Stratix V FPGA的性能参数指标,具体参数如下表所示。该款芯片发售日期为2011年一季度。 与Altera St

2012-08-10 10:07:04 7384

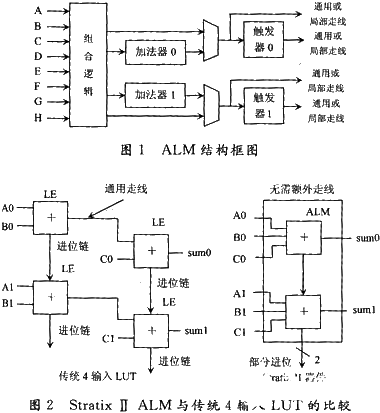

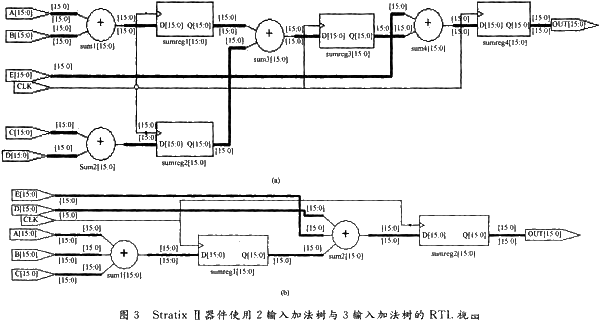

7384 Stratix II是ALTERA公司生产的一款高性能FPGA器件。它采用TSMC的90 nm低k绝缘工艺技术生产,等价逻辑单元(LE)高达180 k,嵌入式存储器容量达到9 MB。该器件不但具有

2020-12-10 11:42:00 1367

1367

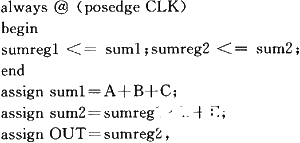

大规模的整数加法在数字信号处理和图像视频处理领域应用很多,其对资源消耗很多,如何能依据FPGA物理结构特点来有效降低加法树的资源和改善其时序特征是非常有意义的。

2023-11-08 09:06:32 636

636

国微思尔芯发布3亿门原型验证系统,采用业界最高容量的 Intel® Stratix® 10 GX 10M FPGAs。

2020-09-08 10:56:20 883

883 加载容量最大可以达到4.125 MB。1]2 从并加载方式的实现以Xilinx 公司Spartan - 6 系列FPGA 为例,与从并加载相关的管脚如表1 所示。表1 从并加载管脚名称由表1 可以看出

2019-06-14 06:00:00

不等。最新器件的速度也大大提高。例如,1.8V Virtex-E器件比前一代产品快了30%,采用源同步数据传输结构,其I/O性能可达到622Mbps。 时间和投资 任何涉足便携式产品设计的人,特别是

2011-02-17 11:21:37

FPGA系列器件汇总目录 1、 MAX7000系列器件 ………………………………………………………………………………………….1 2、 MAX3000A系列器件

2012-08-12 11:51:37

请问一下Stratix 10 MX FPGA是什么?Stratix 10 MX FPGA有哪些功能?

2021-07-09 08:08:06

Stratix III FPGA与Xilinx Virtex-5的体系结构对比Stratix III FPGA与Xilinx Virtex-5的性能对比

2021-05-07 07:00:14

最近弄了个Stratix V GX FPGA开发套件,然后我看那个说明书,发现这个器件好像没有配置芯片。。配置模式只有jtag,和fpp。然后以前自己的板子都是有jic文件下载到配置芯片里,这次

2014-11-20 15:58:02

Stratix系列器件的主要特性是什么?Stratix器件的典型应用有哪些?

2021-04-30 07:00:39

的AD985X系列)。从而为电路设计者提供了多种选择。但在某些场合,专用DDS芯片在控制方式、置频速率等方面与系统的要求仍然有很大差距,在这种情况下,采用高性能的FPGA器件设计符合自己需要的DDS

2019-06-18 06:05:34

1. 为什么要使用FPGA实现在全控型电力电子开关器件出现以后,为了改善交流电动机变压变频调速系统的性能,科技工作者在20世纪80年代开发出了应用脉宽调制(PWM)技术的变压变频器,由于它的优良

2022-01-20 09:34:26

FPGA内部实现一个完整系统功能。本文采用Altera公司提供的SoPC Builder工具将Nios II CPU软核嵌入到Cyclone II系列FPGA内部以控制高性能DDS器件AD9858,并采用

2020-11-24 06:39:52

Altera设计工具辅助系统所提供的强大的高效能工具。采用Cyclone V FPGA,不仅能实现业界最低的总体拥有成本,还可获得型号最全的低成本器件——从25K逻辑单元(LE)到301K LE,以及不到

2015-02-09 15:02:06

OpenCL(Open Computing Language,开放计算语言)开发实现的。本课题是在FPGA上采用OpenCL实现二叉树期权定价算法。实现框架如下:实验过程中发现,虽然OpenCL支持

2017-09-25 10:06:29

延时实现最佳性能。AdvancedIO的产品结合Altera最新28-nm FPGA技术,提供了理想的解决方案。在我们的网络卡中采用Altera Stratix V FPGA后,我们能够在市场上推出

2012-05-14 12:38:53

18 幅图像的速度每秒处理 3,015 幅图像。† 这些数字表明,英特尔 Stratix 10 FPGA 在处理大批量任务时完全可媲美其他高性能计算(HPC)器件(如 GPU), 在处理小批量任务时则比其他器件更快。

2019-07-17 06:34:16

摘要:为了实现对非相干雷达的接收相参处理,基于数字稳定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL编程语言,设计了一种基于FPGA的DSU硬件实现方法。实验结果表明

2019-06-28 08:27:33

处理等方面受到了限制,由于FPGA中关于浮点数的运算只能自行设计,因此,研究浮点加法运算的FPGA实现方法很有必要。

2019-07-05 06:21:42

芯片市场优势 Altera 28nm Stratix V FPGA在高端应用市场中实现了业界最大带宽和最高系统集成度, 非常灵活,降低了成本和总功耗。对于大批量产品,采用Stratix V FPGA

2012-09-21 13:49:05

有着严格的浪涌电流和稳态工作电流限值要求,因此由总线供电的器件应用经常忽视FPGA,而是更愿意采用性能和灵活性都不及 FPGA 的微控制器解决方案。随着赛灵思低功耗系列器件中最新成员Artix-7

2016-07-27 17:14:50

本设计方案采用了一种改进的快速中值滤波算法,成功地在Altera公司的高性能Stratix II EP2S60上实现整个数字红外图像滤波,在保证实时性的同时,使得硬件体积大为缩减,大大降低了成本

2021-04-23 06:00:55

本文基于Viitex-5 LX110验证平台的设计,探索了高性能FPGA硬件系统设计的一般性方法及流程,以提高FPGA的系统性能。

2021-04-26 06:43:55

如何提高VMMK器件的性能?

2021-05-21 06:35:39

元器件的合理布局提高敏感器件的抗干扰性能

2021-02-19 07:05:29

如何采用FPGA提高广播应用的集成度?

2021-04-29 06:04:54

处理等方面受到了限制,为什么研究浮点加法运算的FPGA实现方法很有必要? 因为FPGA中关于浮点数的运算只能自行设计 。

2019-08-15 08:00:45

本文充分利用FPGA高速实时特点,采用并行处理及流水线设计,通过优化CAVLC编码结构和level编码子模块,提高CAVLC编码器的性能。

2021-04-28 06:34:13

复杂器件专业技术相结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。此外,TPACK提供的芯片解决方案可以导入到最新的FPGA中,进一步降低功耗。最终实现

2019-07-31 07:13:26

,输出设备。FPGA具有实现高速并行运算的能力,因而成为高性能数字信号处理的理想器件。此外,与专用集成电路(ASIC)相比,FPGA具有可重复编程的优点。

2019-11-06 08:11:54

对于各种不同的数据中心工作负载,FPGA 可以显著提高性能,最大程度减少附加功耗并降低总体拥有成本 (TCO)。

2019-10-10 07:46:05

的奇怪的ACE程序。我已经在网上阅读了很多文档,但是如果我只是想让FPGA像加法器一样运行(例如),我就不明白为什么ACE文件如此重要。我也磕磕绊绊地想要与董事会沟通。有人可以解释一下我如何将FPGA编程为加法器并使其运行?谢谢!乔纳森

2020-06-08 09:29:46

如何在ALTERA公司的Quartus II环境下用VHDL、Verilog HDL实现设计输入,采用同步时钟,成功编译、综合、适配和仿真,并下载到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

有没有人对如何用参数化加法器树编写Verilog有任何建议,输入参数是操作数的数量?加布里埃尔以上来自于谷歌翻译以下为原文Does anyone have any suggestions

2019-04-25 13:28:42

文中采用Ahera公司最新、具有最佳性能、最大密度和最低功耗的高端FPGA StratixⅢ设计了基于CPCI总线的通用FPGA信号处理板,并在某雷达系统中进行了实际应用。

2021-05-07 06:54:25

介绍一种在FPGA上实现的单精度浮点加法运算器,运算器算法的实现考虑了FPGA器件本身的特点,算法处理流程的拆分和模块的拆分,便于流水设计的实现。

2021-04-29 06:27:09

热量是如何产生并影响LED的?如何提高LED性能?

2021-06-15 09:02:39

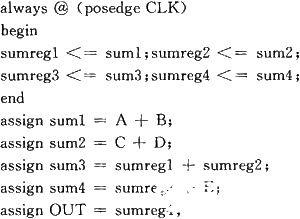

电路为:第一种直接相加的方式会生成一个较长的加法链,而第二种加法方式相当于实现了一个加法树,其在时序收敛上相较于第一种方式更加友好,也往往采用较多。第一种电路的实现方式在《软为硬用,如是而已》中提

2022-08-01 14:29:09

,分频后的时钟波形在时钟的上升沿对信号进行采样,那么就会得到如图1(a)中所表示的等效时间采样。等效时间采样技术的原理作用及采用FPGA器件实现系统的设计图1 等效时间采样示意图2 、基于FPGA的等效

2020-10-21 16:43:20

请问一下高速流水线浮点加法器的FPGA怎么实现?

2021-05-07 06:44:26

IJF编码是什么原理?如何实现IJF编码?采用FPGA和集成器件来实现IJF编码

2021-04-13 06:56:04

实现方案。这就意味着对于多通道或高速系统,用户可以充分利用 FPGA 器件的并行性来最大化性能,而对低速系统,则可以更多采用串行方式完成设计。这样,设计人员就能够根据算法和系统的要求来定制实现方案,不必

2018-08-15 09:46:21

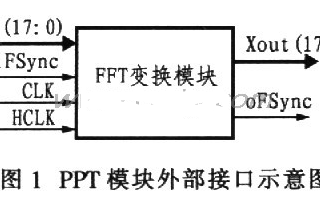

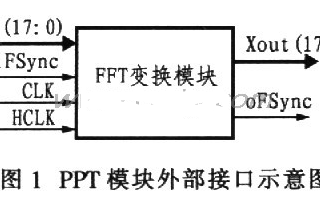

主要介绍基于现场可编程门阵列(FPGA)的微波接力通信中FFT 模块的设计与实现方案。提出一种全并行流水结构,采用新一代大容量的高速Stratix 系列FPGA 可以在N 个系统时钟之内

2009-11-24 12:13:19 19

19 Dini推出业界容量最大的基于Altera Stratix III器件的ASIC

Altera公司日前宣布,Dini集团在其业界容量最大的单板FPGA原型引擎中采用了具有340K逻辑单元(LE)的Strati

2008-11-12 10:36:25 444

444 Altera Stratix IV FPGA助推XDI dbX分析平台

Altera公司日前宣布,XtremeData有限公司下一代dbX系列数据库平台设计采用了高性能Stratix IV FPGA,该系列专门用于对大型数据库进行全

2009-12-04 08:37:02 664

664 Altera推出面向Stratix IV FPGA的最新开发套件

Altera公司近日宣布推出其面向 Stratix IV FPGA 的最新开发套件。Stratix IV E FPGA 开发套件具有业界最高密度、最高性能的 FPGA。该套

2009-12-09 08:45:26 792

792 高速流水线浮点加法器的FPGA实现

0 引言现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操

2010-02-04 10:50:23 2042

2042

Altera Stratix IV FPGA继续广受全球媒体好评

Altera公司今天宣布,40-nm Stratix® IV FPGA系列最近荣获电子编辑媒体的多个奖项。Stratix IV系列因其在密度、性能和功耗上的优

2010-02-24 09:44:20 1198

1198 Stratix IV通过Interlaken通用性测试

Altera公司宣布,Stratix IV FPGA通过Interlaken联盟的器件通用性测试。Altera认证了与使用Interlaken协议的第三方组件的高性能FPGA接口。Stratix IV

2010-03-10 09:26:13 557

557 Altera推出业界带宽最大的28nm Stratix V FPGA

Altera公司近日发布业界带宽最大的FPGA——下一代28-nm Stratix V FPGA。Stratix V FPGA具有1.6 Tbps串行交换能力,采用各种创新技术和前沿28-n

2010-04-22 10:39:54 677

677 28nm Stratix V FPGA突破带宽瓶颈

Altera公司的最新28nm Stratix V FPGA正是为满足高带宽应用设计要求而推出。 移动互联网、高清视频、军事、医疗以及计算

2010-05-10 17:52:04 713

713 Altera公司今天宣布,开始量产发售40-nm Stratix® IV FPGA系列密度最大的器件。Stratix IV E EP4SE820具有820K逻辑单元(LE),非常适合需要高密度、高性能和低功耗FPGA的各类高端应用,包括ASI

2010-06-22 10:50:22 694

694 Stratix V FPGA是目前业界发售的最复杂的半导体。它是利用TSMC的28-nm高性能(28HP)工艺来提高性能和带宽的唯一FPGA。28HP工艺结合最优FPGA设计

2011-04-20 09:02:49 488

488 提出一种 OFDM 高性能数字调制器的FPGA实现方案;采用自顶向下的设计思想,将系统分成FIR滤波器、数控振荡器、移相器、乘法电路和加法电路等5大模块,重点论述了FIR滤波器、数控振

2011-08-15 11:15:53 62

62 Altera公司(Nasdaq: ALTR)宣布,成功实现28-nm Stratix® V GX FPGA与PLX®技术公司(Nasdaq: PLXT) ExpressLane™ PCI Express® (PCIe®) Gen3的互操作

2011-12-14 09:28:09 677

677 Altera公司(NASDAQ: ALTR)今天宣布,在28-nm高性能Stratix® V FPGA中实现了业界第一个单芯片双路100G转发器解决方案。

2012-03-05 09:40:11 665

665 浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计

2012-07-06 15:05:42 47

47 Altera公司 (NASDAQ: ALTR)今天宣布推出Quartus® II软件13.0版,这一软件实现了性能最好的FPGA和SoC,提高了设计人员的效能。28 nm FPGA和SoC用户的编译

2013-05-07 14:30:30 3639

3639 为了缩短加法电路运行时间,提高FPGA运行效率,利用选择进位算法和差额分组算法用硬件电路实现32位加法器,差额分组中的加法单元是利用一种改进的超前进位算法实现,选择进位算

2013-09-18 14:32:05 33

33 基于FPGA的系统提高电机控制性能 。

2016-01-07 15:00:19 24

24 Intel 再次隆重介绍了自家的 Stratix 10 TX FPGA芯片 。 这是地球上最快的FPGA芯片,浮点性能达到10TFLOPS(每秒10万亿次),简单来说,可以在1秒内处理420张蓝光

2018-04-23 05:55:00 7830

7830 观看这一视频演示,了解Stratix® II GX FPGA是怎样帮助您任意改变背板卡的位置,同时全面保持信号完整性不变的。利用Stratix II GX FPGA的即插即用信号完整性技术,您不

2018-06-22 03:56:00 1870

1870 Stratix III FPGAs support SGMII GigE operation on LVDS I/O pins at 1.25 Gbps. With Stratix III

2018-06-22 01:16:00 3138

3138 with Stratix III FPGAs. See how Stratix III FPGAs:

Allow for the lowest possible power consumption without

2018-06-22 03:50:00 1687

1687

关键词:Quartus , FPGA , Stratix 与以前的版本相比,只需要一半的时间就能实现业界性能最好的设计 Altera公司今天宣布推出Quartus II软件13.0版,这一软件实现

2018-09-25 09:12:01 575

575 Stratix II是ALTERA公司生产的一款高性能FPGA器件。它采用TSMC的90 nm低k绝缘工艺技术生产,等价逻辑单元(LE)高达180 k,嵌入式存储器容量达到9 MB。该器件不但具有

2018-10-24 14:45:14 1

1 )。Stratix IV EP4SE820 FPGA是业界同类产品中密度最大、性能最好、功耗最低的FPGA。EP4SE820 FPGA非常适合各种需要大容量FPGA的高端数字应用,包括ASIC原型开发和仿真

2018-10-24 20:40:01 419

419 支持最新一代光纤通道协议(16GFC)的FPGA。背板、交换机、数据中心、云计算应用、测试测量系统以及存储区域网的开发人员采用Altera最新一代28-nm高性能FPGA,能够大幅度提高数据速率,快速进行

2019-05-27 10:33:26 1467

1467 Nios II系列软核处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS,在Altera FPGA中实现仅需35美分。Altera的Stratix 、Stratix GX

2019-09-26 07:00:00 1271

1271

Intel又次隆重介绍了自家的Stratix 10 TX FPGA芯片。浮点性能达到10TFLOPS(每秒10万亿次),具体化的就是可以在1秒内处理420张蓝光碟片的数据信息。

2019-08-07 14:42:09 441

441 英特尔 Stratix 10 设备采用革命性的英特尔 Hyperflex FPGA 架构,结合英特尔嵌入式多芯片互连桥接 (EMIB) 专利技术、高级接口总线 (AIB)和不断壮大的 chiplet 产品组合,性能比前代高性能 FPGA 提升最高两倍。

2019-10-02 15:18:00 1300

1300 对实现FFT的工程,目前通用的方法是采用DSP、FFT处理电路及FPGA。用DSP实现FFT的处理速度较慢,不能满足某些高速信号实时处理的要求;专用的FFT处理器件虽然速度较快,但是价格相对昂贵

2020-07-27 17:52:01 1191

1191

FPGA工艺尺寸的进步和更加灵活的设计配置、以及基于FPGA的系统取得的进步已经使FPGA制造商充满信心地进入了以前由微处理器和ASIC供应商垄断的市场。最近,Xilinx的VirtexTM和Altera的Stratix产品系列分别推出了新器件,进一步缩小了性能差距,再次提高了性能标准。

2020-07-27 18:30:59 363

363 Altera公司推出其面向Stratix® IV FPGA的最新开发套件。Stratix IV E FPGA 开发套件具有业界最高密度、最高性能的 FPGA。该套件为用户提供了全面的设计环境,其中包括迅速开始其高密度原型产品设计所需的硬件和软件。

2020-08-30 08:19:01 826

826 Altera Stratix V FPGA的电源解决方案

2021-04-29 09:41:47 5

5 该器件基于现有的英特尔 Stratix 10 FPGA 架构以及英特尔先进的嵌入式多芯片互连桥接 (EMIB) 技术;

2023-03-14 14:30:19 688

688 proFPGA 四模块英特尔 Stratix 10 GX 10M FPGA 原型设计系统采用 4 个基于英特尔 Stratix 10 GX 10M FPGA 的可插拔 FPGA 模块。

2023-03-17 11:22:30 470

470 有关加法器的知识,加法器是用来做什么的,故名思义,加法器是为了实现加法的,它是一种产生数的和的装置,那么加法器的工作原理是什么,为什么要采用加法器,下面具体来看下。

2023-06-09 18:04:17 3481

3481 FPGA实现加法和减法运算非常简单,实现乘法和除法可以用IP,那实现对数和指数运算该用什么呢?

2023-08-05 09:37:05 810

810

前段时间和几个人闲谈,看看在FPGA里面实现一个Mem加法器怎么玩儿

2023-10-17 10:22:25 279

279

![]()

德赢Vwin官网

App

德赢Vwin官网

App

评论