美国赛灵思(Xilinx)2012年4月5日使用28nm工艺制造的FPGA “Virtex-7 X690T”演示了有线通信系统(背板)。该FPGA配备有80个以最大13.1Gbit/秒的速度工作的高速串行收发器“GTH”,已于2012年

2012-04-09 11:13:59 2848

2848 最大的收发器数量。 图1 Xilinx的7系列FPGA随着集成度的提高,其高速串行收发器不再独占一个单独的参考时钟,而是以Quad来对串行高速收发器进行分组,四个串行高速收发器和一个COMMOM(QPLL)组成一个Quad,每一个串行高速收发器称为一个Channel,以XC7K325T为例,GTX在F

2020-11-20 12:08:15 17712

17712

输入输出端口 从Implemented Design中可以看到FPGA中资源大致分布如下。中间蓝色是CLB可编程逻辑块、DSP或BRAM,两侧的彩色矩形块是I/O接口和收发器,划分的方块是不同的时钟域 Configurable Logic Block (CLB)可编程逻

2022-12-27 15:54:52 1788

1788 。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

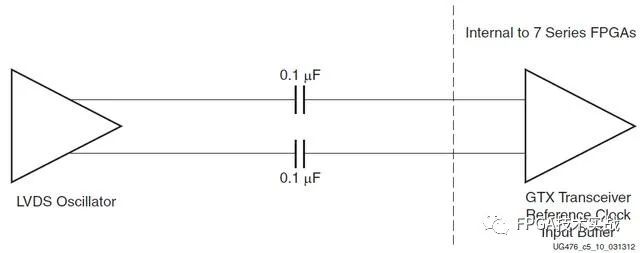

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

你好我尝试使用xilinx 7系列收发器IP生成器示例(Vivdao提供)Thegt0_qplllock_in,gt0_qplloutclk_in,gt0_qplloutrefclk_in

2018-11-05 11:34:22

嗨,我想了解7系列收发器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

本帖最后由 QQ3511836582 于 2017-3-29 15:42 编辑

疑问描述测试表明,Spartan-6 FPGA的GTP收发器有可能受到临近bank中用户管脚的干扰。因此,赛灵思

2017-03-21 14:34:27

FPGA GTP收发器设计指导疑问描述测试表明,Spartan-6 FPGA的GTP收发器有可能受到临近bank中用户管脚的干扰。因此,赛灵思针对bank0和bank2中管脚的使用提出了一些新的建议

2016-08-25 09:46:38

FPGA的任意一个管脚都可以作为时钟输入端口,但是FPGA专门设计了全局时钟,全局时钟总线是一条专用总线,到达片内各部分触发器的时间最短,所以用全局时钟芯片工作最可靠,但是如果你设计的时候时钟太多

2012-02-29 09:46:00

数据访问状态的功能简单地说就是中断监测和数据收发。每次系统复位后 FPGA 会自动配置 PDIUSBD12 器件,配置完成之后设备收发器模块会处于空闲状态(TS_IDLE)。PDIUSBD12 器件

2018-11-27 09:20:08

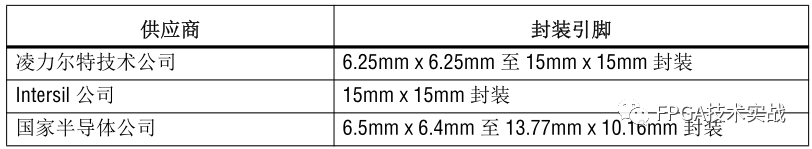

FPGA高速收发器设计原则高速FPGA设计收发器选择需要考虑的因素

2021-04-09 06:53:02

高速收发器(SERDES)的运用范围十分广泛,包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。FPGA高速收发器设计时,我们需要注意哪些事项呢?

2019-08-07 06:26:42

_XCKU060_2FFVA1517E、FPGA_XC7A200T_2FFG1156C)电压主要有VCCINT(内核电压),VCCRAM(RAM块电压),VCCAUX(辅助电压),VCCO(IO电压)以及高速串行收发器GTX Transceiver的供电电压。一般,VCCINT=VCCBRAM=1.0V,VCCO=VCCAUX=VCCAUX_IO=1.8V.高速

2021-12-28 06:38:44

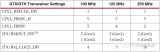

我正在研究使用高速收发器接收部分的定制电路板。所有四个接收器的参考时钟相同,为125 MHz。我从焦平面阵列(FPA)接收数据并使用8 / 10b编码。我可以让FPA重复显示空白行(字符1FFD

2020-05-05 11:39:41

所需的关键信息:管脚编号、管脚名称、管脚DDR内存分组、管脚BANK编号、辅助组(VCCAUX)、超级逻辑域(SLR)、I/O管脚类型(配置、HR、HP、收发器管脚等)以及与器件Pin-to-Pin兼容相关的NC管脚信息。图4、Pinout文件内容举例

2021-05-28 09:23:25

所需的关键信息:管脚编号、管脚名称、管脚DDR内存分组、管脚BANK编号、辅助组(VCCAUX)、超级逻辑域(SLR)、I/O管脚类型(配置、HR、HP、收发器管脚等)以及与器件Pin-to-Pin兼容相关的NC管脚信息。图4、Pinout文件内容举例

2021-07-08 08:00:00

描述 PMP9408 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流

2022-09-21 07:56:06

描述PMP10520 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨(1V/20A、 1.2V/30A

2022-09-27 06:46:35

CAN收发器是连接CAN控制系统与CAN总线网络的桥梁,当选型CAN收发器时应该注意哪些参数?本文将带大家深入的了解收发器的每项参数与其在实际应用中的意义。

2020-12-18 07:16:27

在CAN通信中,收发器起到了十分相当特别的作用。目前市面的收发器型号也是不计其数,本文则是根据收发器的发展,简单介绍几款收发器的特点。很多年前,NXP的CAN收发器几乎在每一个CAN节点上都看的到,当时最常见的型号就是PCA82C250。

2019-09-03 06:04:44

我需要能够使用SFP收发器。我想使用收发器向导,但我不知道选择哪些选项。我不确定我的转账率是多少。我知道我需要使用的时钟大约是600MHz。我还需要能够从此收发器恢复时钟。收发器是否有输出时钟?谢谢你的帮助。

2020-04-07 14:39:32

描述PMP9407 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。此设计采用一个 5V 输入且配有一个

2022-09-26 06:32:49

`描述PMP9408 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流

2015-05-11 10:30:22

`描述PMP10520 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨(1V/20A、 1.2V/30A

2015-05-11 10:27:03

描述PMP10520 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨(1V/20A、 1.2V/30A

2018-09-10 09:02:14

挑战。这些收发器可为模拟RF信号链提供数字接口,允许轻松集成到ASIC或FPGA,进行基带处理。基带处理器(BBP)允许在终端应用和收发器设备之间的数字域中处理用户数据。

2019-09-19 06:20:59

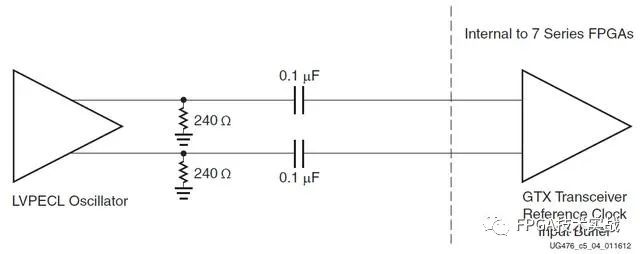

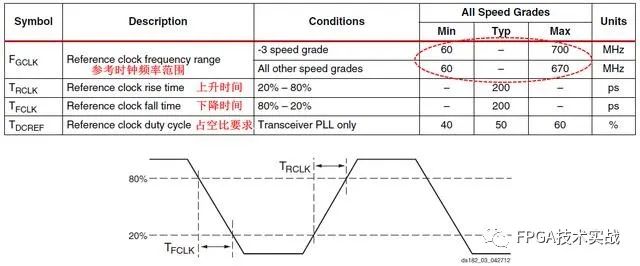

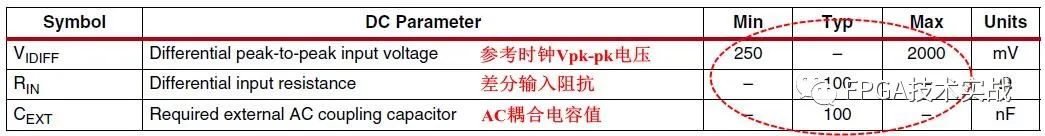

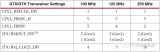

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

嗨,我有2个静态配置的GTX收发器用于HD-SDI操作。我可以使用一个收发器的Txoutclk为两个收发器配备Txusrclock吗?通过这种方式,我可以只用1个Txusrclock为FPGA逻辑

2020-08-19 07:43:50

使用高级校准技术验证收发器FPGA

2019-09-19 09:05:14

我之前在CSDN上查到的资料都显示FPGA需要连接一个独立CAN控制器,如SJA1000再去连CAN收发器。请问我能直接把FPGA的引脚直接连在CAN收发器的TX、RX上吗?如果不能原因又是什么?

2018-10-10 09:25:39

一、概述

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问

2023-06-21 11:23:12

Xilinx FPGA上的JESD204B发送器和接收器框图。发送器/接收器通道实现加扰和链路层;8B/10B编码器/解码器和物理层在GTP/GTX/GTHGbit 收发器中实现。图4. 使用Xilinx

2018-10-16 06:02:44

基于FPGA的通用异步收发器设计

2012-08-18 00:03:20

大家好,我正着手开发我的第一个真正的FPGA PCB。没有更简单的开发板:)我正在试图弄清楚如何使用带有FPGA的1000BASE-T 1.25 GBd小型可插拔收发器。我告诉我需要终止FPGA上

2019-01-22 10:22:55

光纤收发器的优势如何区分单纤收发器与双纤收发器?

2021-01-14 07:26:53

这是我的第一个涉及FPGA的项目,我正在寻找更有经验的用户的好建议,指出我正确的方向。我想实现一个通过以太网端口连接到源的2.4GHz,15Mbps独立通信收发器。我一直在检查SDR系统的实现,但

2019-08-19 10:17:23

,似乎FPGA架构I将获得32位侧并行总线,并且我假设时钟与其频率匹配(5G / 32)。我想将总线宽度从32位改为50位(这很容易)。但是,我要求更宽总线的新时钟是从收发器输出的总线频率的32/50。是否可以在FPGA内部生成此时钟,并将此时钟的副本提供给IO引脚。谢谢

2020-05-11 09:06:46

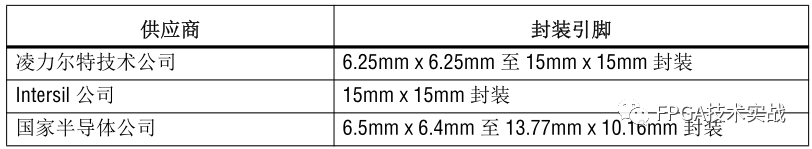

选择合适的千兆位收发器(GT)是通信和实时处理领域尤其需要重点考虑的设计事项,但特定的市场领域可能会存在太多的标准、协议或使用模型。有时针对某一种应用就会涉及到好几种标准,为了选择最适合的千兆位收发器,必须对各种协议的最新发展情况了如指掌。

2019-10-31 06:57:54

引入多个收发器来提升带宽,将是其设计的一个重要组成部分。无论是 SmartNIC、还是密集的服务器互联拓补,都依赖于 FPGA 开展初始部署和调整,然后才会转向 ASIC 。长期以来,Xilinx

2020-09-02 18:55:07

描述PMP9407 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。此设计采用一个 5V 输入且配有一个

2018-08-31 08:59:25

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平输出28.5Gbps的信号要用什么电平?

2014-11-10 09:12:51

描述PMP9463 参考设计提供为 Xilinx Ultrascale™ Kintex® FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流和电压

2018-08-10 09:36:45

如何把故障保护偏置应用于闲置总线?老式收发器与新式收发器的区别在哪里?

2021-05-24 07:03:57

你好我试图在KC705板上使用收发器来生成比特流。我正在使用Vivado 2012.3和7系列FPGA收发器向导v2.3。我之前使用过具有不同传输者名称的IBERT核心。IBERT收发器名称类似于

2020-07-28 10:29:31

我是FPGA设计的新手,但我已经阅读了数据表,应用笔记......几周以来我仍然无法使用收发器。但绝望之后,我只是按照这个示例/教程:http://china.xilinx.com/support

2020-07-24 14:35:18

请问“窄带收发器”和一般的收发器(比如CC1101)有什么区别

2018-06-21 07:54:27

大家好,我想在我的测试板上使用FPGA中唯一的时钟。(FPGA是zynq ultrascale +,时钟来自quad228(GTH收发器)的clk0。)我尝试了各种各样的东西,比如

2020-04-30 08:16:16

我之前在CSDN上查到的资料都显示FPGA需要连接一个独立CAN控制器,如SJA1000再去连CAN收发器。请问我能直接把FPGA的引脚直接连在CAN收发器的TX、RX上吗?如果不能原因又是什么?

2018-10-10 09:05:37

选择合适的FPGA千兆位收发器为什么至关重要?

2021-04-13 06:58:27

`有谁知道这个收发器哪里能买么,有25mm×15mm规格的么`

2013-12-13 11:44:18

FPGA高速收发器设计原则

高速收发器(SERDES)的运用范围十分广泛, 包括通讯、计算机、工业和储存,以及必须在芯片与

2009-04-07 22:26:14 986

986 基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3626

3626

面向收发器(SERDES) FPGA 的PDN 设计对电源有严格的要求,需要干净的电压源。虽然低功耗应用中通常采用低泄漏(LDO) 线性稳压器,但这一方法必须仔细的隔离电压源。电路板设计人员在这

2011-05-11 18:29:41 57

57 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 PMP9407 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。此设计采用一个 5V 输入且配有

2017-02-08 09:14:00 671

671 PMP9463 参考设计提供为 Xilinx Ultrascale™ Kintex® FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。 它利用一个 PMBus 接口来实现电流和电压

2017-02-08 09:22:11 419

419 PMP10520 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨(1V/20A、 1.2V/30A

2017-02-08 15:59:50 789

789 了解如何在您的 UltraScale™ FPGA 设计中部署串行收发器。了解并利用串行收发器模块的特性,如 8B/10B 和 64B/66B 编码、通道绑定、时钟校正和逗点检测。其它专题

2017-02-09 08:04:41 327

327 赛灵思(Xilinx)公司FPGA器件的高速串行收发器类别如下

2017-02-11 11:11:30 5958

5958

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

Xilinx公司业界首款28 nm FPGA Kintex-7 10Gbps 收发器性能演示。

2018-06-01 15:50:00 3960

3960 设计人员呼吁提升10G+ 芯片到芯片和背板性能, 依赖接收机均衡来补偿信号失真。观看视频, 并排比较 Xilinx® Virtex®-7 FPGA GTH 收发器 和 Altera Stratix V GX 收发器的均衡能力。

2018-05-23 15:47:00 3974

3974

每一个收发器拥有一个独立的发送端,发送端有PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)组成

2018-06-20 13:48:00 2709

2709

首次演示新型Xilinx 7系列GTH收发器,通过背板以13.1 Gb / s的速度运行。

2019-01-03 13:25:38 4048

4048 该演示展示了Xilinx SERDES开发的最新成果,首次公开展示了Xilinx 58Gb / s PAM4收发器。

2018-11-29 06:21:00 2048

2048 该视频演示了具有32.75G背板功能的Virtex®UltraScale+™FPGA,功率优化的收发器。

该收发器具有同类最佳的发送抖动和第三代客户验证的自适应接收器均衡功能......

2018-11-28 06:39:00 2161

2161 Xilinx推出全球首款28nm FPGA,展示10Gbps SERDES功能

Xilinx在Kintex-7 K325T FPGA上展示了10Gbps收发器,这是有史以来第一款28nm FPGA。

2018-11-28 06:30:00 3785

3785 Xilinx GTX(12.5 Gb / s)收发器与SFP +和10G背板一起运行。

2018-11-30 06:36:00 9807

9807 spartan-6 FPGA GTP收发器。在本文档中,gtp_dual是gtpa1_dual图块的同义词。

•Dual是两个GTP收发器的集群或集合,共享两个差分参考时钟针对和模拟电源针。

2019-02-15 14:42:47 27

27 本章介绍virtex-6 FPGA GTH收发器向导,并提供相关信息,包括其他资源、技术支持和向xilinx提交反馈。向导自动执行创建HDL包装器的任务,以配置virtex-6设备中的高速串行GTH收发器。

2019-02-20 09:35:45 4

4 7系列FPGA GTP收发器的可定制Logicore™IP Chipscope™Pro集成误码率测试(IBert)内核用于评估和监控GTP收发器。该核心包括在FPGA逻辑中实现的模式生成器和校验

2019-02-20 14:30:00 25

25 和AFCT-701SDZ 10 Gbs以太网SFP +收发器产品与具有自适应DFE的XilinxVirtex®-6FPGA 11.18 Gbps收发器的高速互操作性。 Xilinx产品:Virtex-6 HXT

2021-04-14 11:53:31 4122

4122

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

2021-05-02 22:10:00 5587

5587

引言:本文我们介绍GTX/GTH收发器时钟架构应用,该文内容对进行PCIe和XAUI开发的FPGA逻辑设计人员具有实际参考价值,具体介绍: PCIe参考时钟设计 XAUI参考时钟设计 1.PCIe

2021-03-29 14:53:47 5441

5441

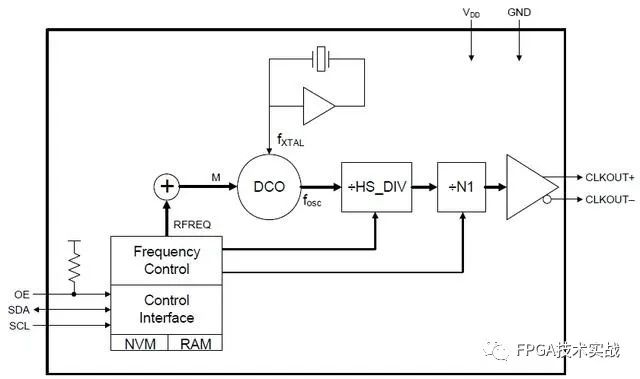

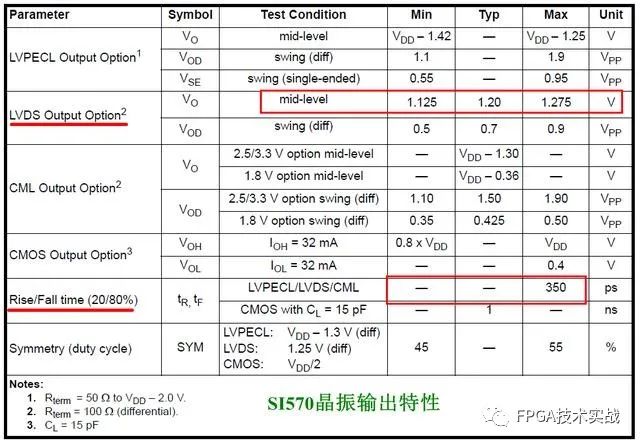

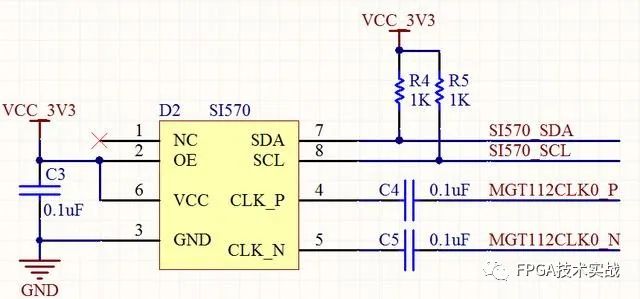

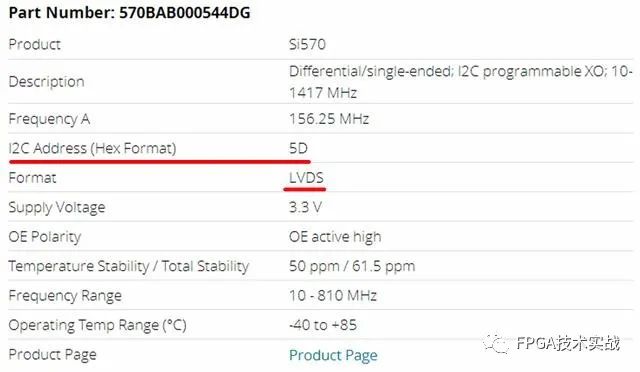

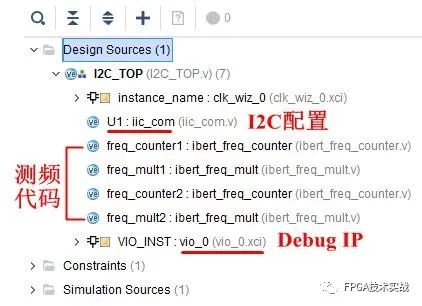

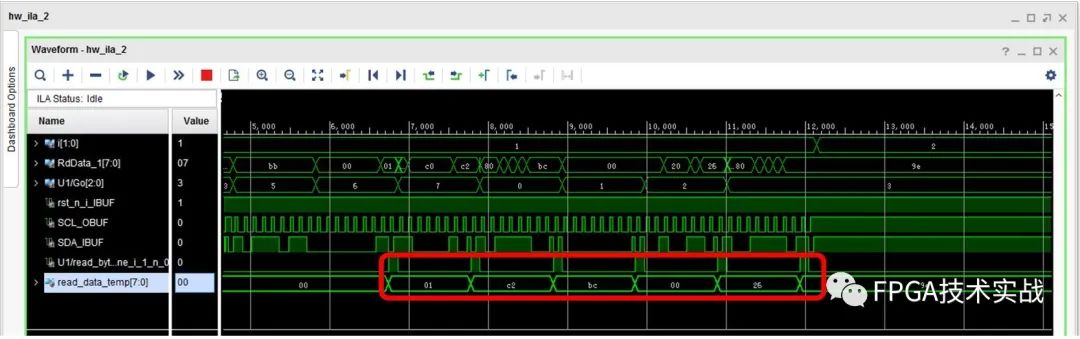

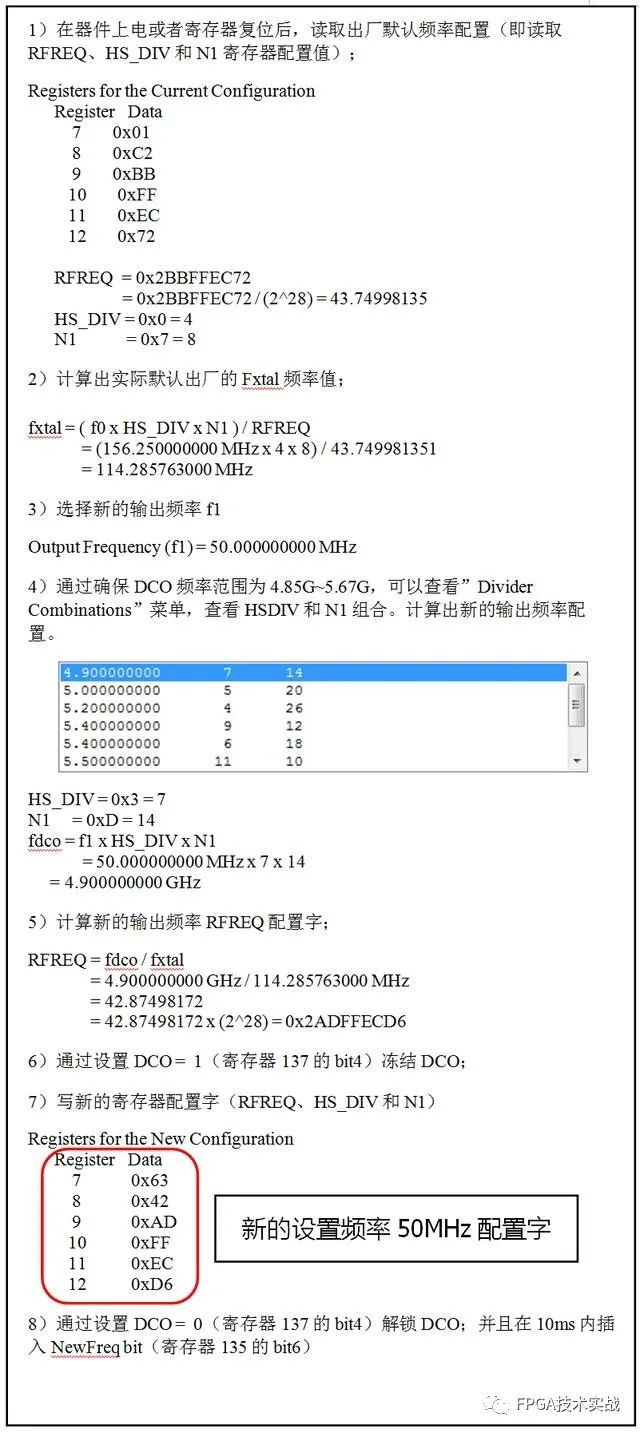

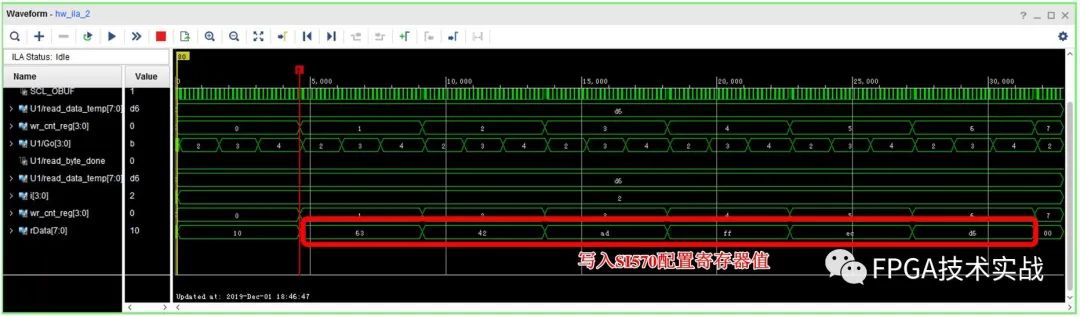

晶振是数字电路设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考。

2021-04-07 12:00:44 3914

3914

面向收发器 (SERDES) FPGA 的PDN设计对电源有严格的要求,需要干净的电压源。虽然低功耗应用中通常采用低泄漏 (LDO) 线性稳压器,但这一方法必须仔细的隔离电压源。

2021-05-02 09:58:00 1527

1527

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述 GTX/GTH收发器时钟

2021-11-06 19:51:00 35

35 xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH、GTZ四种串行高速收发器,可以支持多种协议如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

德赢Vwin官网

App

德赢Vwin官网

App

评论