摘要本文提出了一种基于

FPGA的通用位同步器

设计方案。

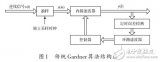

方案中的同步器是采用改进后的Gardner算法结构,其中,内插滤波器采用系数实时计算的Farrow结构,定时误差检测采用独立于载波相位偏差的GA-TED算法,内部控制器和环路滤波器的参数可由外部控制器设置,因而可以适应较宽速率范围内的基带码元。

2013-10-14 13:58:10

5135

5135

本文介绍了集中式插入法帧同步系统的原理,分析了帧同步系统的工作流程。采用模块化的设计思想,利用VHDL设计了同步参数可灵活配置的帧同步系统,阐述了关键部件的设计方法,提出了一种基于

FPGA的帧同步系统

设计方案。

2013-11-11 13:36:01

4359

4359

为了研究数字化γ能谱仪,本文提出一种基于

FPGA的数字核脉冲分析器硬件

设计方案,该

方案采用现场可编程逻辑部件(

FPGA),完成数字多道脉冲幅度分析仪的硬件设计。用QuartusⅡ软件在

FPGA平台上完成了数字核脉冲的幅度提取并生成能谱。

2013-11-21 10:57:26

1948

1948

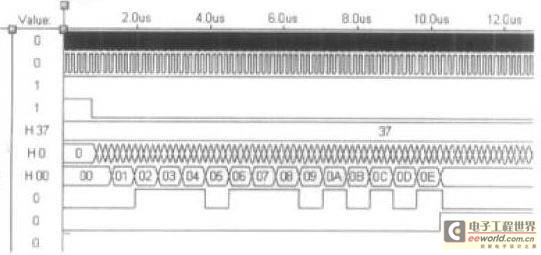

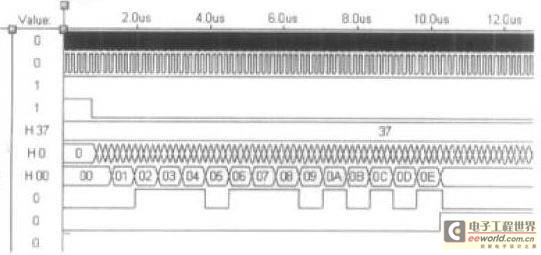

本文以标准的I2C 总线协议为基础,提出了一种基于

FPGA的I2C SLAVE 模式总线的

设计方案。

方案主要介绍了SLAVE 模式的特点。给出了设计的原理框图和modelsim 下的行为仿真时序

2014-02-26 11:39:13

12337

12337

跨

时钟域处理是

FPGA设计中经常遇到的问题,而如何处理好跨

时钟域间的数据,可以说是每个

FPGA初学者的必修课。如果是还是在校的学生,跨

时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01

3278

3278

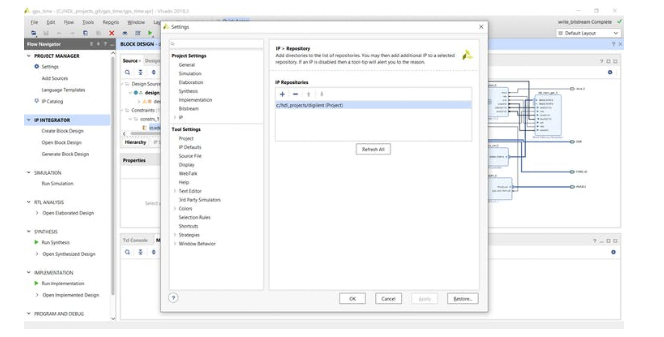

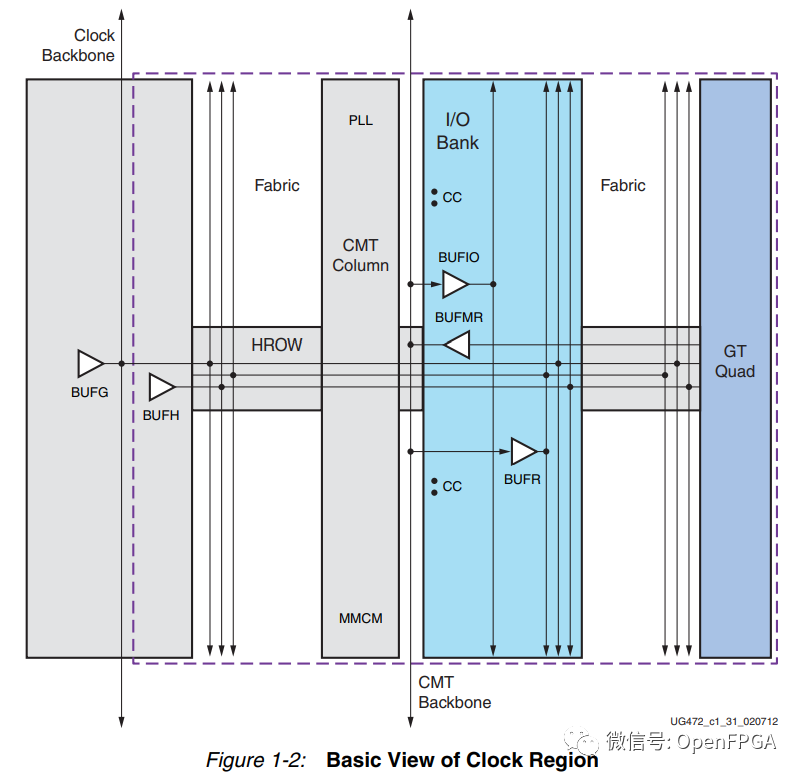

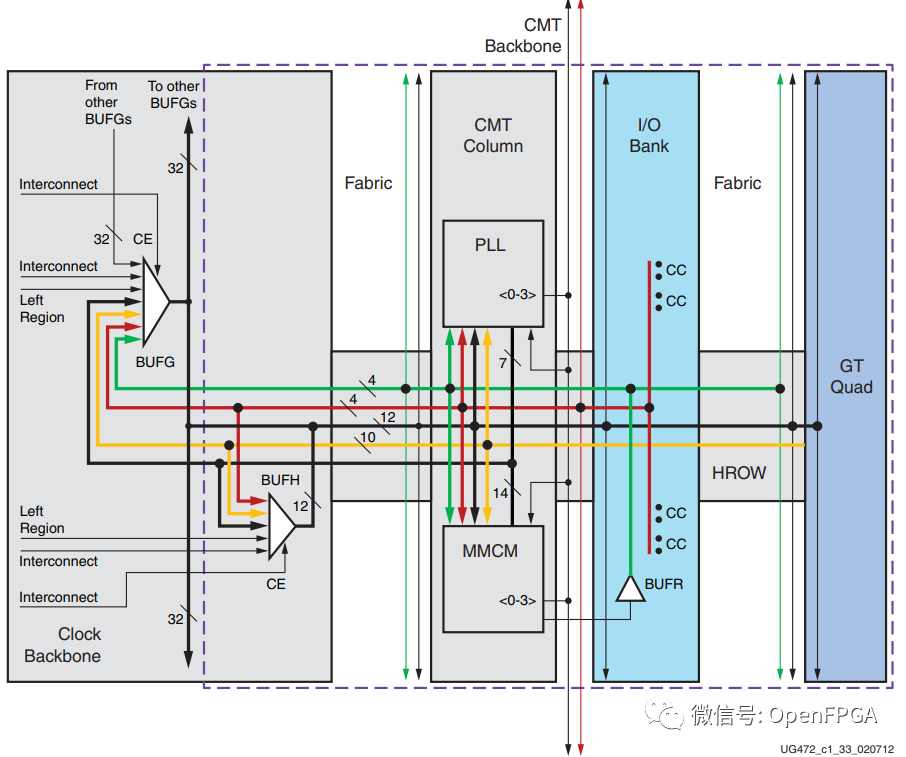

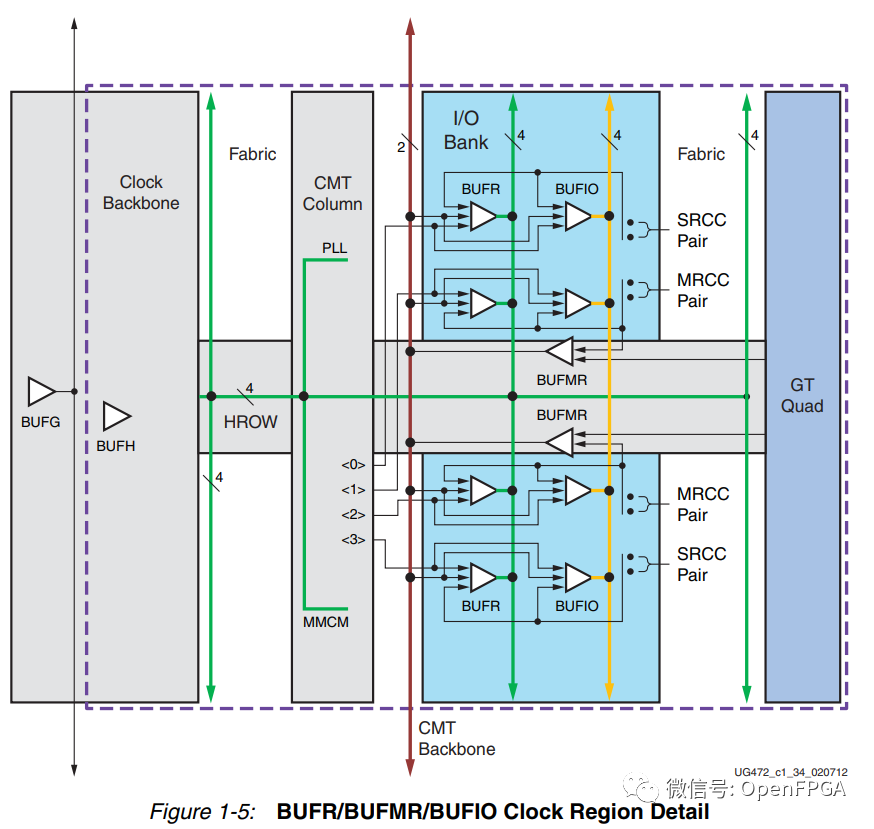

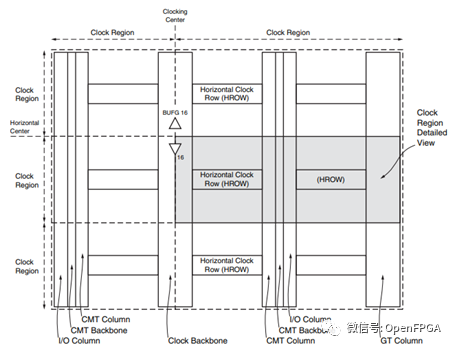

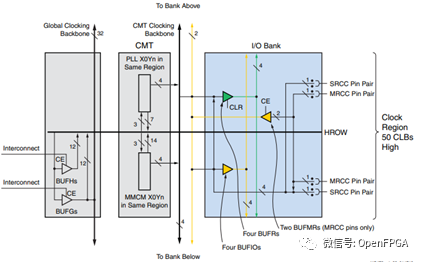

引言:7系列

FPGA具有多个

时钟路由资源,以支持各种

时钟

方案和要求,包括高扇出、短传播延迟和极低的偏移。

2022-07-22 09:46:39

682

682

组合逻辑产生的

时钟可能有毛刺,会被错误地当成有效

时钟边沿,在设计中会导致功能错误。因此,不要使用组合逻辑的输出作为

时钟。

2024-01-22 09:30:50

168

168

FPGA典型

设计方案精华汇总

2012-08-16 16:29:32

TS101和TS201链路口传输的数据形式是一样的,都是

时钟双沿触发的DDR数据,并且每次传输的数据个数都是4个长字(即128bit)的整数倍。鉴于以上两种芯片链路口数据的共同点,所以采用

FPGA与两类芯片

2019-06-21 05:00:04

各位

FPGA设计大赛参赛者注意了:小编这里帮大家解释一下

设计方案提交规则和活动时间安排 自4月23日比赛开始,参赛者报名之后即可提交

设计方案。

设计方案提交的截止日期是活动结束,暨

设计方案评选的最后

2012-05-04 10:27:46

在设计中想用上AD9254作为ADC,在设计过程中发现datasheet内部提供了多种

时钟

设计方案,由于设计的限制,想要省去所有

方案中均推荐使用的AD951x芯片,请问是否有曾经使用过该款AD的同仁,使用直接从

FPGA差分

时钟引脚引出的

时钟信号,是否能够满足设计的要求?

2018-11-02 09:14:32

都是经典项目,建议下载学习STM32

设计方案与示例分享 第一波stm32

设计方案与示例分享第二波STM32计

方案与示例分享 第三波STM32计

方案与示例分享 第四波

2018-09-03 18:52:06

从ASIC到

FPGA的转换系统

时钟

设计方案

2011-03-02 09:37:37

请教下 避障小车 的

设计方案有几种选择? 超声波 避障 如何?有没有其它

设计方案

2012-08-31 11:54:02

一种基于

FPGA的简易频谱分析仪

设计方案,其优点是成本低,性能指标满足教学实验所要求的检测信号范围。

2021-04-30 06:43:21

分享一款不错的采用

FPGA的集群通信移动终端

设计方案

2021-05-25 06:32:04

提出一种基于

FPGA和USB的通用CCD采集系统

设计方案。该系统在不改变硬件的情况下可以采集多种CCD,并上传至PC机,使用软件处理采集到的数据。

2021-04-22 06:23:40

本文以星载测控系统为背景,提出了一种基于 Actel Flash

FPGA的高可靠

设计方案。采用不易发生单粒子翻转的 flash

FPGA芯片,结合

FPGA内部的改进型三模冗余、分区设计和降级重构,实现了高实时、高可靠的系统。

2021-05-10 06:58:47

利用

FPGA的无线通信收发模块

设计方案[hide][/hide]

2009-11-26 10:25:56

压电马达原理压电马达的驱动

设计方案

2021-03-04 07:17:42

基于51单片机的

时钟-跑表

设计方案(程序+仿真)

2018-11-29 12:07:49

本帖最后由 eehome 于 2013-1-5 10:11 编辑 基于

FPGA及VHDL的LED点阵汉字滚动显示

设计方案

2012-08-19 23:20:48

上学时做的变频器

设计方案,利用simulink仿真,基于

FPGA的变频器

设计方案。

2014-09-10 10:40:12

基于

FPGA的数据无阻塞交换

设计方案,不看肯定后悔

2021-04-29 06:48:07

1 引言 在学习《电子线路》、《信号处理》等电子类课程时,高校学生只是从理论上理解真正的信号特征。不能真正了解或观察测试某些信号。而幅频特性和相频特性是信号最基本的特征.这里提出了基于单片机和

FPGA的频率特性测试仪的

设计方案,可使学生在实践中真正观察和测试信号的频率特性。

2019-07-22 08:19:34

多种EDA工具的

FPGA

设计方案

2012-08-17 10:36:17

多种负电源轨的

设计方案

2021-03-11 07:04:30

如何用

FPGA实现DVB码流分析功能的嵌入式

设计方案?

2021-04-28 06:19:10

“玩转

FPGA:iPad2,赛灵思开发板等你拿”活动持续火爆进行中……………………活动得到了广大电子工程师积极强烈的支持,为了回报电子工程师和网站会员,现在只需提交

fpga

设计方案,就有机会获得赛灵

2012-07-06 17:24:41

提高

FPGA的

时钟精度的

方案有哪些,哪位大神告诉一下

2015-10-13 08:22:31

数字电子钟

设计方案数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式

时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。数字钟从原理上讲是一种典型

2009-12-17 11:31:30

本文的创新点是提出了一种基于

FPGA的高速数据中继器

设计方案,并综合分析了ASIC和NP等方法设计的高速网络中继器设计方法,在设计的功能和灵活性两方面做了很好的权衡。

2021-04-29 06:45:51

PCI总线特点及开发现状PCI接口配置空间的实现求一款在PCI总线上利用

FPGA技术设计PCI总线接口的

设计方案

2021-04-15 06:17:20

讨论了一种基于

FPGA的64点FFT处理器的

设计方案,输入数据的实部和虚部均以16位二进制数表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ软件为开发平台对处理器各个的模块进行设计,在Stratix系列中的EP1S25型

FPGA通过了综合和仿真,运算结果正确。

2021-04-29 06:25:54

求一种基于

FPGA的HDLC协议控制器

设计方案

2021-04-30 06:53:06

求一种基于

FPGA的永磁同步电机控制器的

设计方案。

2021-05-08 07:02:07

一种基于

FPGA技术的多按键状态识别系统的

设计方案

2021-05-06 08:44:59

求一种基于

FPGA芯片的嵌入式PLC处理器的

设计方案。

2021-05-06 08:24:19

求一种基于

FPGA的锁相环位同步提取电路的

设计方案。

2021-04-29 06:52:21

本文主要提出一种集中式插入法帧同步的

FPGA的

设计方案。

2021-06-02 06:07:10

用单片机实现电子

时钟

设计方案

时钟电路在计算机系统中起着非常重要的作用,是保证系统正常工作的基础。在一个单片机应用系统中,

时钟有两方面的含义:一是指为保障系统正常工作的基准振荡定时信号,主要由晶振

2009-12-17 11:20:48

针对单片机的

时钟频率电路有哪几种

设计方案?分别有何优缺点?

2022-02-22 06:20:34

介绍了一种基于

FPGA的LED 大屏

设计方案,采用自顶向下的设计思想,设计了基于

FPGA的双口RAM 和扫描控制电路,解决了传统LED 大屏设计中,控制系统复杂﹑可靠性差的问题。关键

2009-06-15 09:34:14

26

26

在介绍了GPS 同步

时钟基本原理和

FPGA特点的基础上,提出了一种基于

FPGA的GPS同步

时钟装置的

设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45

40

40

一种

FPGA

时钟网络中锁相环的实现

方案:摘 要:本文阐述了用于

FPGA的可优化

时钟分配网络功耗与面积的

时钟布线结构模型。并在

时钟分配网络中引入数字延迟锁相环减少

时钟偏差,探

2009-08-08 09:07:22

25

25

DLL在

FPGA

时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对

FPGA的内部资源DLL等直接例化,实现其消除

时钟的相位偏差、倍频和分频的功能。

时钟电路是

FPGA开发板设计中的

2009-11-01 15:10:30

33

33

采用

FPGA的嵌入式系统

设计方案可编程片上系统设计是一个崭新的、富有生机的嵌入式系统设计技术研究方向。本文在阐述可编程逻辑器件特点及其发展趋势的

2010-03-22 11:21:49

16

16

本文阐述了用于

FPGA的可优化

时钟分配网络功耗与面积的

时钟布线结构模型。并在

时钟分配网络中引入数字延迟锁相环减少

时钟偏差,探讨了

FPGA

时钟网络中锁相环的实现

方案。

2010-08-06 16:08:45

12

12

提出了一种基于

FPGA的

时钟跟踪环路的

设计方案,该

方案简化了

时钟跟踪环路的结构,降低了

时钟调整电路的复杂度。实际电路测试结果表明,该

方案能够使接收机

时钟快速准确地跟踪发

2010-11-19 14:46:54

31

31

基于

FPGA的无线通信收发模块

设计方案1 前言 近年来,随着半导体工艺技术和设计方法的迅速发展,系统级芯片SOC的设计得以高速发展,

2009-12-10 10:11:07

1707

1707

基于

FPGA的视频传输流发送系统

设计方案 1 引言 在目前的广播电视系统中ASI接口是使用非常广泛的一种接口形式,该接口随同SPI一起被欧

2009-12-14 09:39:33

1245

1245

基于ADC和

FPGA脉冲信号测量的

设计方案 0引言 测频和测脉宽现在有多种方法。通常基于MCU的信号参数测量,由于其MCU工作频率很低,所以能够达到的精度也

2009-12-21 09:13:23

1501

1501

基于

FPGA的高速定点FFT算法的

设计方案引 言 快速傅里叶变换(FFT)作为计算和分析工具,在众多学科领域(如信号处理、图像处理、生物信息学、计算物理

2010-02-09 10:47:50

992

992

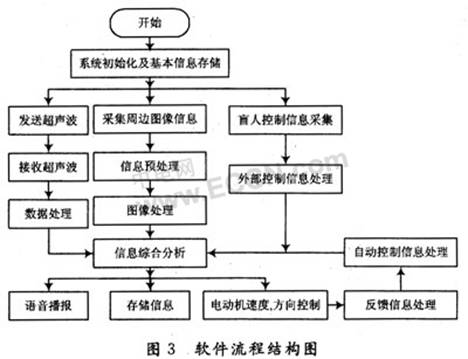

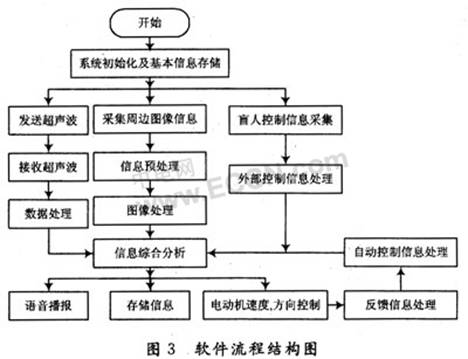

采用

FPGA技术的智能导盲犬

设计方案众所周知眼晴是“心灵之窗”,而对于突然失去或从未拥有过“心灵之窗”的盲人来说,生活上的困难与心理上

2010-03-22 09:40:28

869

869

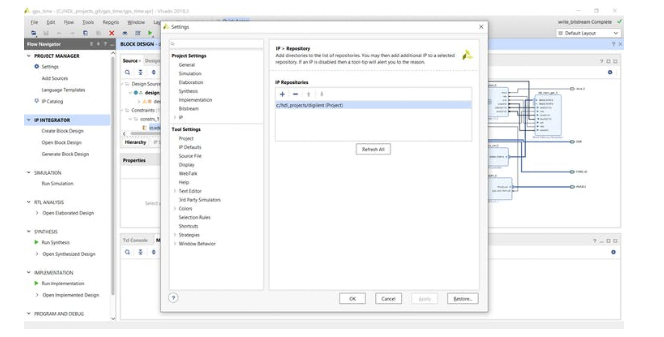

基于Spartan-6的

FPGASP601开发

设计方案Spartan-6是Xilinx公司的

FPGA批量应用有最低成本的

FPGA,采用45nm低功耗铜工艺,在成本,性能和功耗上有最好的平衡.该系

2010-04-02 14:25:28

2268

2268

采用VC++程序的

FPGA重配置

设计方案利用现场可编程逻辑器件

FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据

2010-04-14 15:14:57

580

580

多种EDA工具的

FPGA

设计方案概述:介绍了利用多种EDA工具进行

FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配

2010-05-25 17:56:59

670

670

在

FPGA设计中,为了成功地操作,可靠的

时钟是非常关键的。设计不良的

时钟在极限的温度、电压下将导致错误的行为。在设计PLD/

FPGA时通常采用如下四种类型

时钟:全局

时钟、门控

时钟

2011-09-21 18:38:58

3472

3472

SERDES在数字系统中高效

时钟

设计方案,无论是在一个

FPGA、SoC还是ASSP中,为任何基于SERDES的协议选择一个参考

时钟源都是非常具有挑战性的。

2012-02-16 11:23:43

5384

5384

DLL在_

FPGA

时钟设计中的应用,主要说明DLL的原理,在Xilinx

FPGA中是怎么实现的。

2015-10-28 14:25:42

1

1

耳温枪

设计方案设计耳温枪

设计方案设计耳温枪

设计方案设计

2015-11-13 15:58:16

0

0

基于

FPGA技术的RS232接口时序电路

设计方案

2017-01-26 11:36:55

29

29

基于

FPGA的OLED真彩色显示

设计方案

2017-01-18 20:35:09

25

25

数字电路

设计方案中DSP与

FPGA的比较与选择

2017-01-18 20:39:13

15

15

如何正确使用

FPGA的

时钟资源

2017-01-18 20:39:13

22

22

介绍了精密

时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的

时钟同步系统

方案。该

方案中,本地

时钟单元、

时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在

FPGA

2017-11-17 15:57:18

6196

6196

基于

FPGA三相正弦波pwm控制器的

设计方案

2018-04-08 17:33:39

30

30

基于

FPGA的调焦电路

设计方案资料下载

2018-05-07 15:53:08

9

9

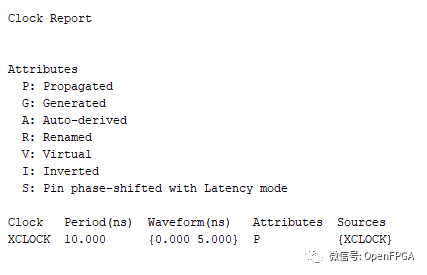

时钟是

FPGA设计中最重要的信号,

FPGA系统内大部分器件的动作都是在

时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18

5065

5065

引言:从本文开始,我们陆续介绍Xilinx 7系列

FPGA的

时钟资源架构,熟练掌握

时钟资源对于

FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列

FPGA

时钟,比较了7系列

FPGA

时钟

2021-03-22 10:25:27

4326

4326

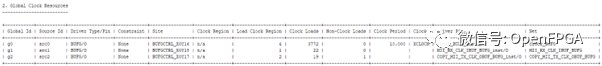

对于一个设计项目来说,全局

时钟(或同步

时钟)是最简单和最可预测的

时钟。只要可能就应尽量在设计项目中采用全局

时钟。

FPGA都具有专门的全局

时钟引脚,它直接连到器件中的每一个寄存器。这种全局

时钟提供器件中最短的

时钟到输出的延时。

2021-04-24 09:39:07

5827

5827

基于

FPGA的二进制相移键控

设计方案

2021-05-28 09:36:50

11

11

基于

FPGA的嵌入式信号处理系统

设计方案

2021-06-02 11:04:33

0

0

基于

FPGA的嵌入式信号处理系统

设计方案

2021-06-02 11:04:33

0

0

基于CPLD/

FPGA的半整数分频器

设计方案

2021-06-17 09:37:02

21

21

时钟

设计方案在复杂的

FPGA设计中,设计

时钟

方案是一项具有挑战性的任务。设计者需要很好地掌握目标器件所能提供的

时钟资源及它们的限制,需要了解不同设计技术之间的权衡,并且需要很好地掌握一系列设计实践

2021-06-17 16:34:51

1528

1528

基于

FPGA的伪随机数发生器

设计方案

2021-06-28 14:36:49

4

4

基于STM32单片机的

时钟树

设计方案

2021-08-04 16:37:06

38

38

(29)

FPGA原语设计(差分

时钟转单端

时钟)1.1 目录1)目录2)

FPGA简介3)Verilog HDL简介4)

FPGA原语设计(差分

时钟转单端

时钟)5)结语1.2

FPGA简介

FPGA

2021-12-29 19:41:38

5

5

(30)

FPGA原语设计(单端

时钟转差分

时钟)1.1 目录1)目录2)

FPGA简介3)Verilog HDL简介4)

FPGA原语设计(单端

时钟转差分

时钟)5)结语1.2

FPGA简介

FPGA

2021-12-29 19:41:48

10

10

本

方案是一个基于

FPGA的二进制

时钟,使用GPS作为时间参考。

2022-05-13 17:41:31

1786

1786

xilinx 的

FPGA

时钟结构,7 系列

FPGA的

时钟结构和前面几个系列的

时钟结构有了很大的区别,7系列的

时钟结构如下图所示。

2022-07-03 17:13:48

2592

2592

ASIC 和

FPGA芯片的内核之间最大的不同莫过于

时钟结构。ASIC设计需要采用诸如

时钟树综合、

时钟延迟匹配等方式对整个

时钟结构进行处理,但是

FPGA设计则完全不必。

2022-11-23 16:50:49

686

686

本文详细描述了

FPGA实现图像去雾的实现

设计方案,采用暗通道先验算法实现,并利用verilog并行执行的特点对算法进行了加速;

2023-06-05 17:01:45

862

862

德赢Vwin官网 网站提供《基于

FPGA的PCI硬件加解密卡的

设计方案.pdf》资料免费下载

2023-10-18 11:18:03

0

0

德赢Vwin官网 网站提供《基于CPLD/

FPGA的多串口扩展

设计方案.pdf》资料免费下载

2023-10-27 09:45:17

2

2

德赢Vwin官网 App

德赢Vwin官网 App

评论