赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19707

19707

以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

9177 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

FPGA 如何估算程序所需的资源?是不是要把输出接到FPGA的PIN上后build,才算是程序所需的资源?因为我有个比较复杂的程序,没有output到FPGA上,LUT使用为8000+一旦output到FPGA上,LUT使用为8W+.是不是此时的LUT使用量才是程序真正所需的?

2017-01-19 09:09:19

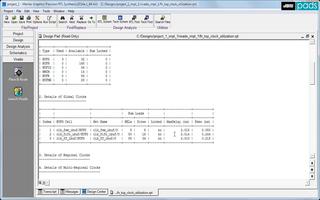

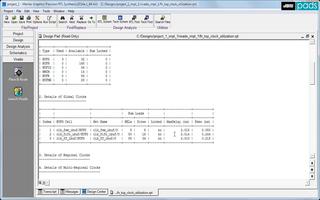

)传输到 PCB 设计。在 PCB 布局或布线开始前,I/O 优化可使用 PADS 项目数据进行叠层规划以及优化初始分配。用户可将结果导出到 Layout,并在项目级别或企业库级别管理 FPGA 元件

2018-09-20 11:11:16

各位大神,小弟最近在做一个项目,由于之前选用的FPGA资源不够,现在需要将程序的资源占用率降下来。经过我的冥思苦想,也找不到好的方法,不知道各位大神平时工作中降低资源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

情况下,FPGA可以被用作ASIC的原型验证平台,帮助设计师验证和优化ASIC的设计。然而,由于FPGA的灵活性和可重构性,它的资源使用效率通常低于专门为特定任务优化的ASIC。

2024-02-22 09:52:22

嗨,我想知道通过使用c ++代码是否存在使用FPGA资源的肮脏,快速且非常粗糙的想法?我的任务是在FPGA上实现一个非常复杂的c ++算法。 c ++代码非常复杂,需要几周或几个月才能理解,但同时

2019-03-26 06:42:03

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

在Quartus中怎样在工具在设置使得代码可以被映射到FPGA上的指定区域?在书上看到要进行位置约束,不知怎么弄!本人刚接触这个,求大神解答

2017-06-10 22:25:21

求FPGA内部资源{:soso_e100:}相关资料,发lishenghhuc@126.com,谢谢

2012-09-27 16:55:44

`各位大神,请问FPGA去耦电容如何布局、布线?1.根据文档,一般去耦电容的数量都少于电源引脚,那么去耦电容要放到哪些管脚旁边呢?2.以下三种方案哪种好?2.1电容放在PCB top层FPGA外围

2017-08-22 14:57:10

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的开发流程一般包括功能定义、设计输入、功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真与验证、板级仿真

2023-12-31 21:15:31

对FPGA学习好的资源有哪些?从入门到精通,大家可以分享一起学习呀

2024-01-28 17:00:27

布局加载到实际的FPGA上。这个过程通常通过向FPGA发送一个特定的二进制文件来完成。一旦FPGA被正确地编程,它就可以开始执行所设计的功能。

FPGA的工作原理依赖于可编程的逻辑块、丰富的互连资源和灵活的输入/输出接口。通过编程,用户可以将FPGA配置为实现各种复杂的数字系统功能。

2024-01-26 10:03:55

请问FPGA的资源使用如何评估?

2024-02-22 09:55:53

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

生成的逻辑连接,使层次设计平面化,以便用FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级

2020-11-30 16:22:59

FPGA 设计优化主要分为编码风格、设计规划和时序收敛三大部分,这 些因素直接决定了 FPGA 设计的成败。 编码风格直接影响 FPGA 设计的实现并最终影响设计的性能。尽管综合 工具集成

2022-09-29 06:12:02

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

首先要指出的是,高 WNS 是指多于1ns 的失败时序的余量值。对于此类设计,我们有5个诀窍分享给大家!和一般认知相反的是,成功优化设计并不是很设计技巧关系很大,而是与下列原因息息相关:计算资源

2018-06-11 16:11:07

基于SRAM的FPGA结构是怎样构成的?FPGA连线资源的优势有哪些?

2021-05-06 07:04:23

`FPGA面积优化1.对于速度要求不是很高的情况下,我们可以把流水线设计成迭代的形式,从而重复利用FPGA功能相同的资源。2.对于控制逻辑小于共享逻辑时,控制逻辑资源可以用来复用,例如FIR滤波器

2014-12-04 13:52:40

嗨,我在Windows 8.1上使用ADS 2014。我定义参数化布局并为其创建EM模型和符号。我想在原理图上优化其参数。当我将其符号放在原理图上并更改其参数并运行模拟时,EM模拟运行但结果与我在

2018-09-10 17:09:49

帮助找到延时最长的关键路径,以便设计者改进设计。对于结构固定的设计,关键路径法是进行速度优化的首选方法,可与其他方法配合使用。 在FPGA设计中,面积优化实质上就是资源利用优化,面积优化有多种实现方法

2008-06-26 16:16:11

的,但是想要得道我想要的指令要求的话资源就超出了,因为我做这个液晶屏控制板最终是想用单片机通过这个cpld来控制液晶屏显示的。有什么资源需要优化的方案,其他人做的同样的题目都没有超出资源。所以小弟请各位大侠来帮帮忙,只有20钱了全送了

2019-03-08 00:26:55

学习引擎主要关注时序、资源占用率、能耗。最终的优化结果呈现收敛趋势。InTime运行流程传统FPGA开发经过设计输入、设计综合、布局布线阶段,并依据综合编译结果选择是否再次进行时序优化。人工修改设计代码

2017-07-05 11:00:48

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

表),并根据约束条件优化生成的逻辑连接,输出edf和edn等文件。4)实现实现可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能连接的布线通道进行连线,并

2021-05-27 09:28:40

数据中心。这一应用模式的转变需要具备快速扩展能力的计算节点来满足视频内容制作和分发的各个不同高计算强度阶段的需求,如转码需求和水印需求。

我们近期使用赛灵思SDAccel™开发环境来编译和优化专为FPGA

2019-06-19 07:27:40

NoC 去替代传统的逻辑去做高速数据传输和数据总线管理。· 增加了 FPGA 的布线资源,对于资源占用很高的设计有效地降低布局布线拥塞的风险。· 实现真正的模块化设计,减小 FPGA 设计人员调试

2020-09-07 15:25:33

其在设计思路和编程风格等方面也存在差异,这些差异会对系统综合后的电路整体性能产生重要的影响。在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源

2019-06-18 07:45:03

FPGA加速卡是如何产生的?主要的FPGA加速卡产品有哪些?基于加速卡的FPGA生态系统布局是怎样的?

2021-06-17 06:07:15

的布线资源,对于资源占用很高的设计有效地降低布局布线拥塞的风险。实现真正的模块化设计,减小FPGA设计人员调试的工作量。本文用了一个具体的FPGA设计案例,来体现上面提到的NoC在FPGA设计中的几项

2020-10-20 09:54:00

作为可进行完全配置的片上系统(SoC),FPGA 在其30年的历史中发展迅猛。像 FPGA 这样的可编程器件的问题在于它十分需要布局资源。虽然说将逻辑块散开可以避免布局拥塞,但是为了性能,紧密联系

2018-06-26 15:19:23

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析

2019-06-17 09:03:28

请问各位学友,站内有没有FPGA视频学习资源,,以及下载quartus具体指南,,,谢谢

2015-08-03 16:11:02

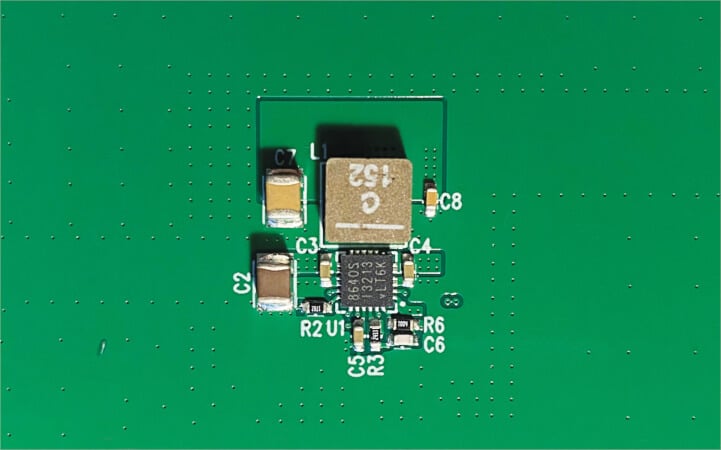

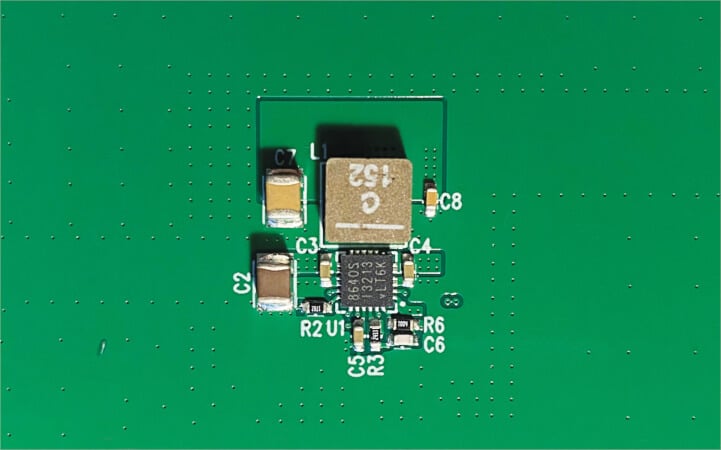

本文从电源PCB的布局出发,介绍了优化SIMPLE SWITCHER电源模块性能的最佳PCB布局方法、实例及技术。

2021-04-25 06:38:31

求大神告知目前资源最丰富的CPLD/FPGA的详情!万分感谢!!!

2013-03-24 17:01:22

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

为使DSP芯片有充裕的资源和时间用于复杂的导航计算,输出高频率的解算结果,论文通过资源优化,只采用FPGA逻辑电路实现了GPS信号的捕获、跟踪、帧同步、卫星自动搜索、伪距信息生

2011-09-01 14:32:51 73

73 本内容详细介绍了高速PCB设计的布局布线优化方法,欢迎大家下载学习

2011-09-27 16:22:33 0

0 本文简要的分析FPGA芯片中丰富的布线资源 。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。

2012-12-17 17:28:41 3491

3491 在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的

2013-01-06 16:12:44 1587

1587 基于FPGA的SM3算法优化设计与实现的论文

2015-10-29 17:16:51 4

4 高级FPGA设计 结构、实现和优化,适合于FPGA的进阶学习。

2016-05-11 16:40:55 15

15 高级FPGA设计 结构、实现和优化,适合于学习FPGA的进阶学习。

2016-05-11 16:40:55 14

14 电子专业单片机相关知识学习教材资料——FPGA片内资源设计指导

2016-08-23 15:55:35 0

0 基于FPGA的可堆叠存储阵列设计与优化

2017-01-07 21:28:58 0

0 基于FPGA的高速固态存储器优化设计_杨玉华

2017-01-13 21:40:36 1

1 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 DSP在线升级与资源优化再配置

2017-10-20 09:53:27 5

5 复用长点数的累加器。本文着重研究基于FPGA的二级相关算法的优化设计方法,通过分析各个关键设计参数对处理器资源消耗的影响,得出能够使系统的资源消耗和时序性能都达到最优的一组参数组合,即最优化结构设计准则。

2017-11-03 10:19:29 0

0 资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 4873

4873 布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 在云制造服务环境中,为了进一步降低需求者的服务成本,提出了一种团购模式下云制造服务资源组合优化模型与算法。在云制造平台发展的初期阶段,以服务需求者的视角分析云制造服务资源组合优化管理问题,通过

2018-01-04 15:17:15 0

0 传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

2018-02-26 10:09:04 0

0 这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

2018-03-21 14:48:00 4672

4672

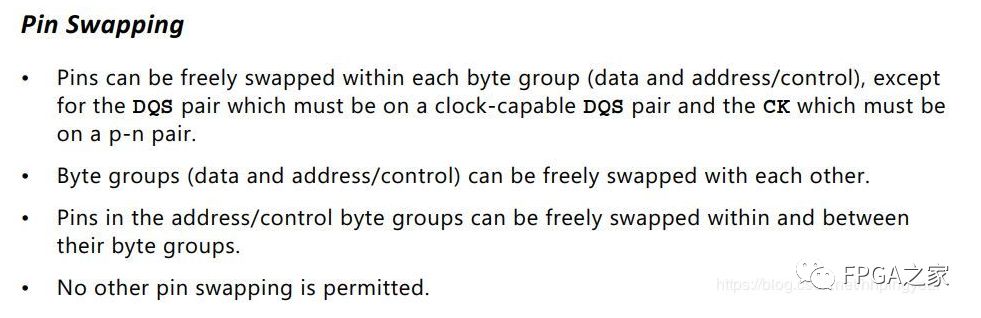

对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O引脚分配是必须面对的众多挑战之一。 由于众多原因,许多设计人员发表为大型FPGA器件和高级BGA封装确定I/O引脚配置或布局方案越来越困难。 但是组合运用多种智能I/O规划工具,能够使引脚分配过程变得更轻松。

2019-06-03 08:06:00 2312

2312 了解如何描述Spartan-6 FPGA中可用的基本片和I / O资源。

2019-01-04 10:32:00 3056

3056 Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 12305

12305

在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 3580

3580 在一个环境中实施从合成到塑封式布局和布线以及比特流生成的全套 FPGA 设计。界面中内置了用于运行布局和布线的常用选项,并在与合成结果相同的位置提供所有报告。

2019-05-17 06:06:00 2586

2586

管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。

2019-06-28 14:34:07 3703

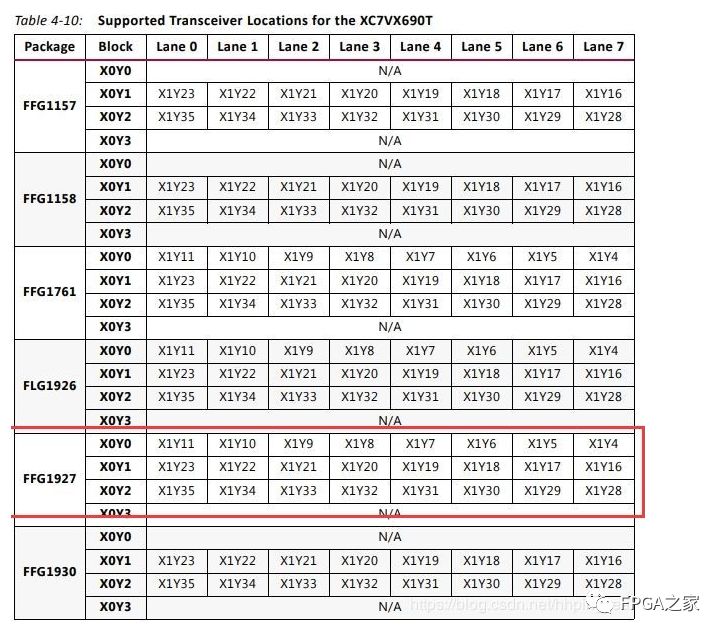

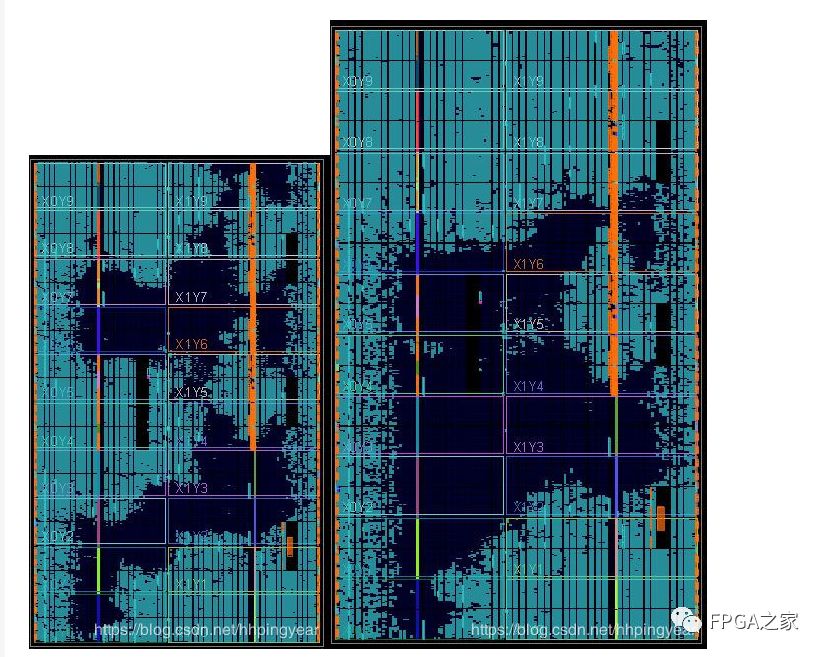

3703 结构配置到FPGA具体的哪个位置。需要说明的是,FPGA里任何硬件结构都是按照横纵坐标进行标定的,图中选中的是一个SLICE,SLICE里面存放着表和其他结构,它的位置在X50Y112上。不同的资源的坐标不一样,但是坐标的零点是公用的。 在FPGA里布局需要考虑的问题是,如何将这些

2020-10-25 10:25:31 7659

7659

在使用 FPGA 过程中,通常需要对资源做出评估,下面简单谈谈如何评估 FPGA 的资源。 FF 和 LUT 的数目:这个在写出具体代码之前,初学者通常没法估算,但资深 FPGA 工程师会估算

2020-12-28 07:59:00 8

8 。Artix-7系列针对成本敏感、高容量应用,针对每瓦最高性能和每瓦带宽进行了优化。Kintex-7系列是一种创新的FPGA产品,针对最佳性价比进行了优化。Virtex-7系列针对最高的系统性能和容量进行了优化。

2020-12-09 14:49:00 24

24 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 。Artix®-7系列针对成本敏感、高容量应用,针对每瓦最高性能和每瓦带宽进行了优化。Kintex-7系列是一种创新型FPGA,针对最佳性价比进行了优化。Virtex-7系列针对最高的系统性能和容量进行了优化。

2020-12-09 15:31:13 9

9 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 。Artix-7系列针对成本敏感、高容量应用,针对每瓦最高性能和每瓦带宽进行了优化。Kintex-7系列是一种创新型FPGA,针对最佳性价比进行了优化。Virtex-7系列针对最高的系统性能和容量进行了优化。

2020-12-10 14:20:00 18

18 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 DDR3。 2.FPGA架构设计问题 我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各模块之间的数据交织情况,这样可以避免

2021-01-07 10:15:31 4645

4645

(06)FPGA资源评估1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA资源评估5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 1099

1099 FPGA基础资源之IOB的应用 1.应用背景 在我们做时序约束时,有时候需要对FPGA驱动的外围器件进行input_delay/output_delay进行约束。不知道,大家有没有被以下这种

2022-12-25 16:30:02 2884

2884 本文介绍了实现优化电路板布局的基础,这是开关模式电源设计的一个关键方面。

2023-03-08 15:01:00 402

402

FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流

2023-04-06 09:39:45 691

691 包体积优化中,资源优化一般都是首要且容易有成效的优化方向。资源优化是通过优化APK中的资源项来优化包体积,本文我们会介绍得物App在资源优化上做的一些实践。

2023-07-24 09:00:48 422

422

FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 949

949

德赢Vwin官网

网站提供《基于FPGA的神经振荡器设计及优化.pdf》资料免费下载

2023-11-10 09:39:29 0

0 如何优化晶振布局与连接 晶振是电子设备中常见的元件之一,用于提供时钟信号和稳定的频率参考。在进行晶振布局和连接时,需要考虑一系列的因素以确保其工作稳定可靠。本文将详细介绍如何优化晶振布局和连接,从而

2023-12-18 14:09:22 257

257 任务是将逻辑元件与连接线路进行合理的布局和布线,以实现性能优化和电路连接的可靠性。然而,FPGA布局布线的过程通常是一项繁琐且耗时的任务,因此加速布局布线算法的研究具有重要意义。本文将详尽探讨FPGA布局布线算法加速的方法与技术,分析其理论基础和实践应用。 FPGA布局布

2023-12-20 09:55:13 200

200

德赢Vwin官网

App

德赢Vwin官网

App

评论