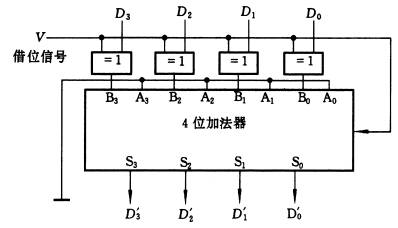

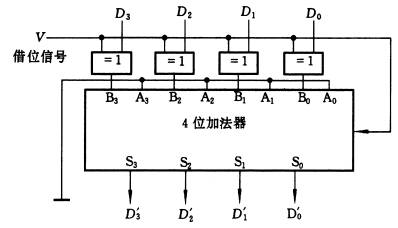

多位二进制减法器,是由加法电路构成的;在加法电路的基础上,减法与加法采用同一套电路,实现加减法共用。

2020-09-01 16:02:09 20233

20233

运算放大器之所以被称为运算放大器,没有叫A放大器或者B放大器,那是因为这种结构可以做运算,比如积分,微分,加法,减法呀等等。

2022-07-13 14:16:14 4389

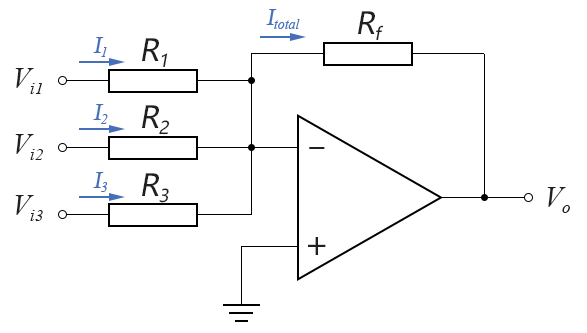

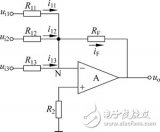

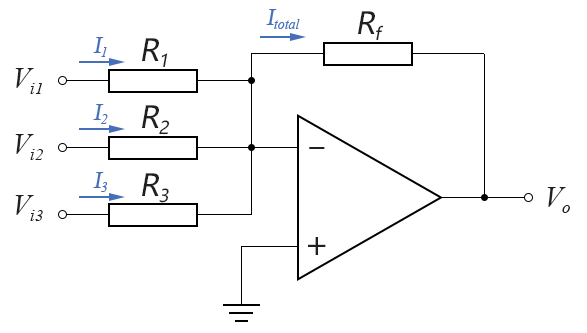

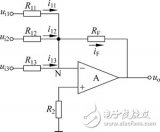

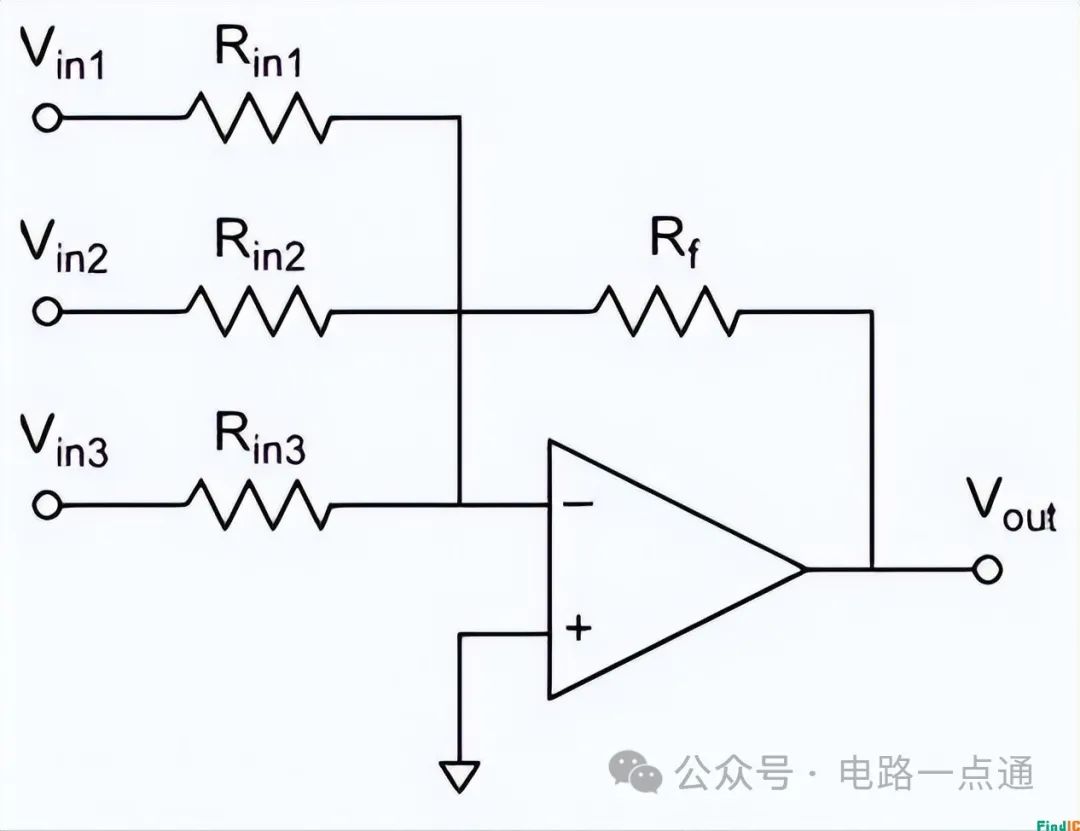

4389 运算放大器构成加法器 可以分为同相加法器和反相加法器

2022-08-05 17:17:38 22398

22398

理想运算放大器特性如下:(1)开环增益 Aud=∞;(2)输入阻抗 Ri = ∞;(3)输出阻抗 Ro = 0;(4)带宽Fbw = ∞;(5) 失调与漂移为零。

2022-09-06 16:40:44 12407

12407

前面的反相放大器和同相放大器可以实现乘法运算的功能,这一小节我们来看如何用运放实现加减法运算。

2023-02-02 14:12:24 22816

22816

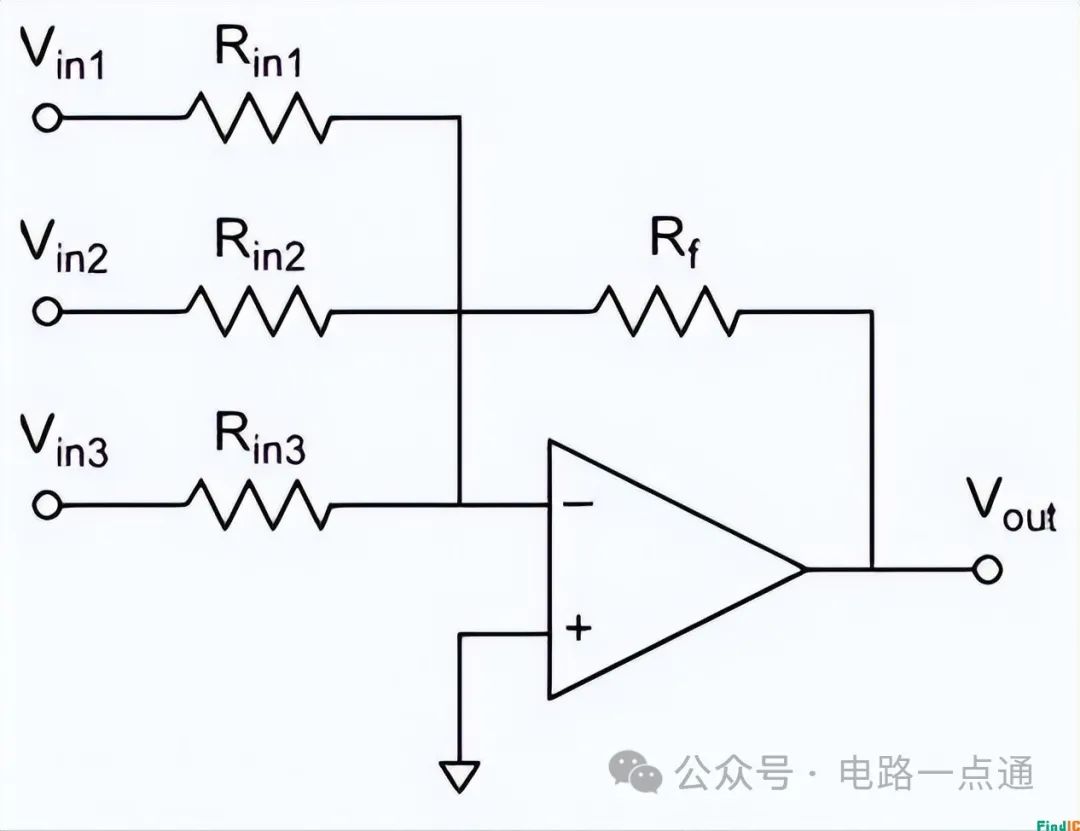

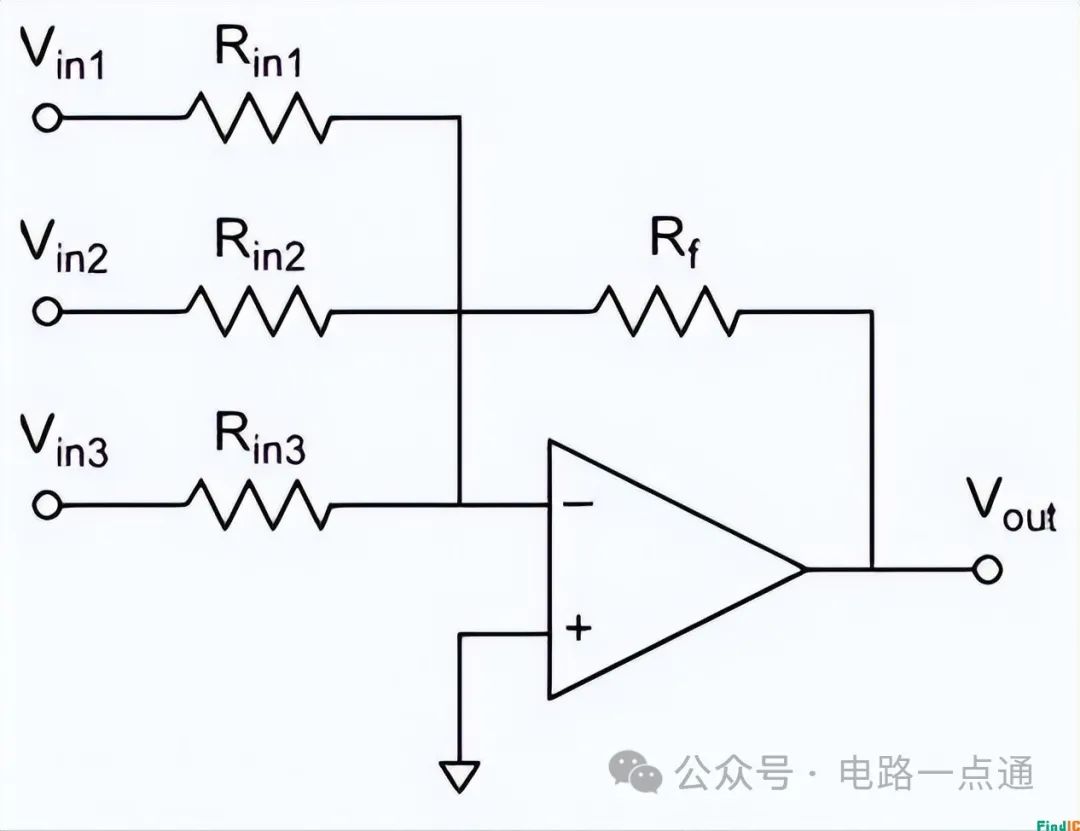

可看出输出值与输入值的和成反比关系,所以叫反相加法运算电路。

2023-08-08 15:41:56 3817

3817

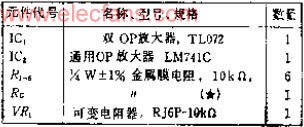

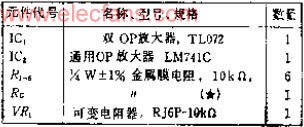

掌握用集成运算放大器组成的比例、加法、减法、积分等运算电路的性能及其测试方法。

2023-10-10 16:23:22 3558

3558

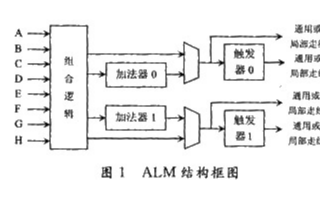

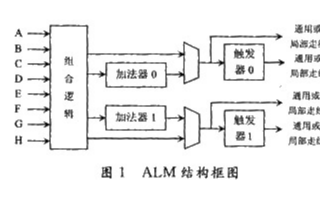

大规模的整数加法在数字信号处理和图像视频处理领域应用很多,其对资源消耗很多,如何能依据FPGA物理结构特点来有效降低加法树的资源和改善其时序特征是非常有意义的。

2023-11-08 09:06:32 636

636

减法器是一种电路,它可以实现二进制数字的减法运算。减法器的工作原理基于位运算和进位/借位机制。

2024-02-19 09:36:37 563

563

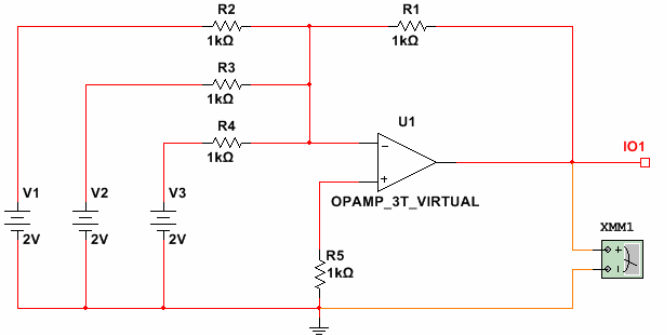

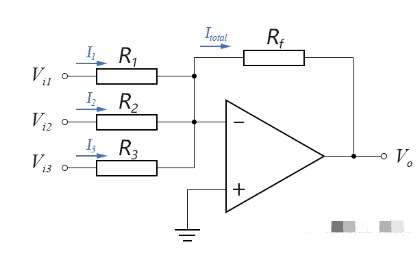

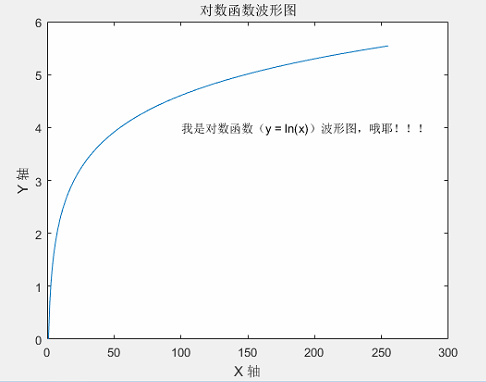

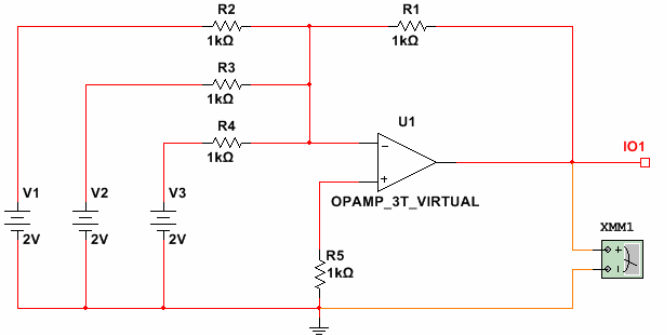

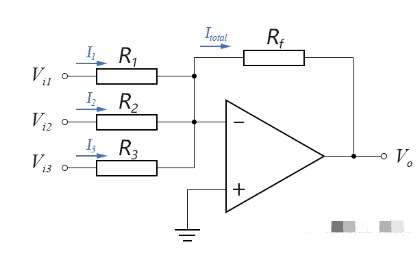

加法运算的电路如下图所示,输出电压为若干个输入电压的比例和

2024-02-19 09:52:06 713

713

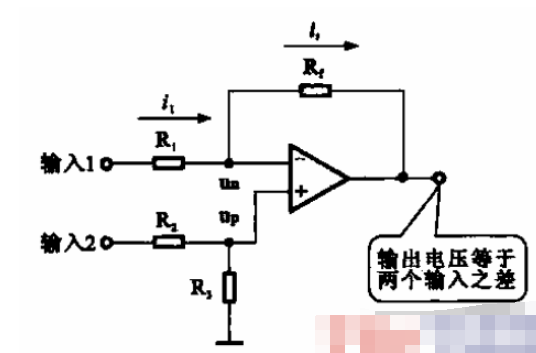

减法电路是基本集成运放电路的一种,算术运算电路主要包括数字**加法器电路、数字减法器电路、数字乘法器电路和数字除法器电路。

2024-02-19 10:00:17 311

311

如何用multisim软件仿真双时钟加/减计数器CT74LS192和译码器CC4511和译码器SM4205构成的30进制加法计数器和30进制减法计数器,求仿真接线图。PCB打样找华强 http://www.hqpcb.com/3 样板2天出货

2012-10-07 21:13:28

前段时间动手做了个小项目,跟大家分享一下!可实现4位带进位加法/减法计算。目前负值无法显示,只显示负数绝对值。对实例1中的显示部分有优化。目前已实现计算器功能,但程序有待优化。遥控板测试说明(红外):—:表示减法+: 表示加法EQ:表示计算/等于

2015-01-20 17:15:24

刚学汇编看加法有点糊涂求个最简单的加法汇编程序像直接写36+37=73 这样直接运算的并且可以在数码管显示的 最好有注释新手求看懂

2013-04-20 04:02:18

,51单片机处理浮点数会浪费大量时间。2、本例使用单片机的P0口和P1口分别显示两个无符号字符型数据的加法和减法的运算结果3、在kei c51中新建工程文件ex6,输入如下的程序代码,编译并生成

2012-03-21 16:55:33

在FPGA中一般减法是怎么处理的呢?比如A-B是采用A+B的补码,还把A和B都定义成有符号的类型,直接进行减法运算呢?

2014-12-24 09:46:57

/ C51中的复合赋值运算符 /变量 复合运算符 表达式先把变量与后边的表达式进行某种运算,然后将运算的结果赋给前面的变量。+= 加法赋值 ?+ 减法赋值*= 乘法赋值 /= 除法赋值%= 取模赋值 &= 逻辑与赋值|= 逻辑或赋值 ~=逻辑非赋值 >>= 右移位赋值

2021-12-07 08:09:34

第21章 DSP矩阵运算-加法,减法和逆矩阵本期教程主要讲解矩阵运算中的初始化,加法,逆矩阵和减法。目录第21章 DSP矩阵运算-加法,减法和逆矩阵21.1 初学者重要提示21.2 DSP基础运算

2021-08-17 08:10:29

第21章 DSP矩阵运算-加法,减法和逆矩阵本期教程主要讲解矩阵运算中的初始化,加法,逆矩阵和减法。目录第21章 DSP矩阵运算-加法,减法和逆矩阵21.1 初学者重要提示21.2 DSP基础运算

2021-08-10 07:04:46

嗨,我正在尽可能使用压缩逻辑来执行加法或减法。我有两个8位数据,我想有时添加或有时减去这两个数字。它看起来像是Elelment有一个叫做“CYINIT”的输入,根据它的值,它可以执行加法或减法。我

2019-03-28 06:07:39

请教大家怎么用VHDL语言实现减法运算?在FPGA设计时又该怎么操作呢?

2012-05-17 20:07:12

Windows -编程-数值运算Rust 支持所有数字类型的基本数学运算:加法、减法、乘法、除法和余数。以下代码显示了如何在let语句中使用每一个:诚接Windows驱动开发外包文件名:src

2021-08-24 14:36:35

20以内加减法训练机基于单片机实现 20 以内整数加减法训练,要求具有加法、减法(结果不出现负数)、加减法三种训练模式,每次训练随机产生题目。可以选择每次训练题目的数目,可分为每组 5 题、10 题

2021-07-15 07:51:35

matlab 矩阵运算矩阵运算MATLAB对矩阵的运算包括算术运算,关系运算和逻辑运算。算术矩阵运算矩阵的基本算术运算(当然标量是矩阵的特殊情况)有:+ 加法- 减法* 乘法/ 右除\ 左除^ 取幂

2009-09-22 15:32:42

处理等方面受到了限制,由于FPGA中关于浮点数的运算只能自行设计,因此,研究浮点加法运算的FPGA实现方法很有必要。

2019-07-05 06:21:42

第21章 DSP矩阵运算-加法,减法和逆矩阵本期教程主要讲解矩阵运算中的初始化,加法,逆矩阵和减法。目录第21章 DSP矩阵运算-加法,减法和逆矩阵21.1 初学者重要提示21.2 DSP基础运算

2021-08-17 07:11:32

处理等方面受到了限制,为什么研究浮点加法运算的FPGA实现方法很有必要? 因为FPGA中关于浮点数的运算只能自行设计 。

2019-08-15 08:00:45

为通用计算机的算法单元,本文特别关注嵌入式系统的实践。在介绍章之后,该出版物分为两部分。第一部分,数学方面和算法,包括数学背景,数字表示,加法和减法,乘法,除法,其他算术运算和有限域中的操作。第二部分,算法

2018-12-20 16:14:53

fpga:Spartan-6 xc6slx150-3fgg484我在资源密集型处理系统中使用了几百个8位加法器,因此资源使用很重要。用于加法器减法器的核心生成器为具有2个8位输入和8位输出,0延迟

2019-04-03 15:55:35

介绍一种在FPGA上实现的单精度浮点加法运算器,运算器算法的实现考虑了FPGA器件本身的特点,算法处理流程的拆分和模块的拆分,便于流水设计的实现。

2021-04-29 06:27:09

的加法树里我们定义的是将两个电路对象相加,当然你也可以用来实现其他的方法,只要符合op方法定义即可。levelBridge: (T, Int) => T 树层级间的调用方法,该方法依赖两个

2022-08-01 14:29:09

矩阵运算中的初始化/加法/逆矩阵和减法,看完你就懂了

2021-11-19 07:02:39

一:算术运算符算术运算符非常地简单,就是小学数学里面的一些加减乘除操作。不过呢,还是有一些语法细节需要注意的。1.加法运算符 + 1 在第3行利用加法运算符 + 进行了加法运算,再将和赋值给了变量b

2021-11-30 06:09:47

FPGA如何实现32位减法运算

2019-02-28 04:59:09

运算放大器一般是用来做反向放大用吗?除了做这个放大之外,它做加法与减法、积分运算的场合多不多?

2019-05-16 06:08:44

hValue = (u16)(-Theta);hValue = 0x166-hValue;//我想在这一步实现减法运算,但是使用ST-link 进行仿真的时候发现,hValue 的值并没有发生变化?请教大家一下,在STM32中,如何实现减法运算呢?

2019-01-17 01:04:46

请问一下高速流水线浮点加法器的FPGA怎么实现?

2021-05-07 06:44:26

8位单片机能够实现超长数计算吗?我说:"只要存储器够大,按照下面的方法设计的加减法运算器及指令,就能够编写程序完成。"1。用全加器搭建一个8位加法器;2。将最低下进位前连接一个1位寄存器,输入端连接

2014-09-22 03:09:55

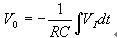

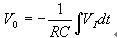

集成运算放大电路实验实验目的1. 了解集成运算放大器的特点。2. 掌握集成运算放大器在信号运算方面的应用。实验原理集成运算放大器按照输入方式可以分为同相、反相、差分三种接法,按照输入电压与输出电压的运算关系可以分为比例、加法、减法、积分、微分等,输入方式和运算关系组合起来,可以构成各种运算放大器。

2008-12-11 23:27:49

集成运算放大电路实验实验目的1. 了解集成运算放大器的特点。2. 掌握集成运算放大器在信号运算方面的应用。实验原理集成运算放大器按照输入方式可以分为同相、反相、差分三种接法,按照输入电压与输出电压的运算关系可以分为比例、加法、减法、积分、微分等,输入方式和运算关系组合起来,可以构成各种运算放大器。

2008-09-22 12:18:59

。二、框图三、加减乘除加法:因为FPGA硬件资源里有加法器,所以我们就直接用加了。减法:我们都知道二进制数的负数就是它的补码,所以A减B就可以写成加法的形式乘法:首先,判断操作数B(乘数)是否为零,不为

2016-09-01 09:03:33

介绍了用VHDL 语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera

公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13 85

85 高精度的乘除法和开方等数学运算在FPGA实现中往往要消耗大量专用乘法器和逻辑资源。在资源敏感而计算时延要求较低的应用中,以处理时间换取资源的串行运算方法具有广泛的应

2010-07-28 18:05:14 37

37 集成运算放大器是一种高增益的直流放大器。它有两个输入端,一个输出端。外接负反馈电路后能够完成反相比例,同相比例,加法、减法、乘法,微分、积分等运算功能。现

2008-09-24 22:07:42 18609

18609

加法运算放大器电路包含有

2008-09-27 17:33:18 27291

27291

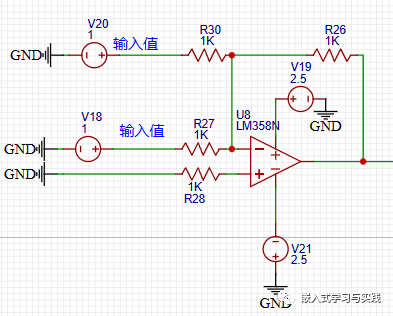

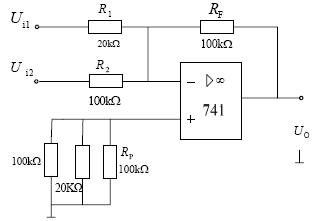

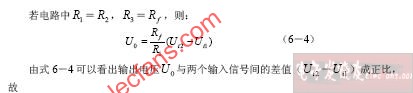

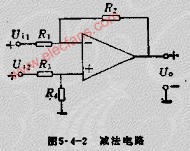

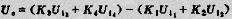

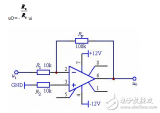

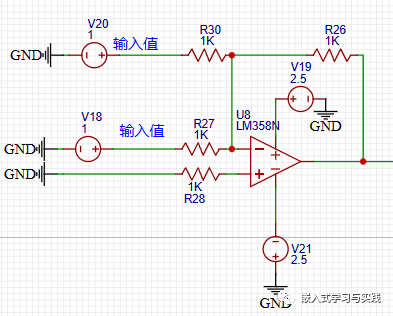

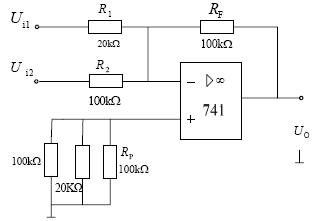

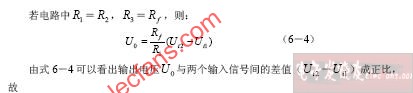

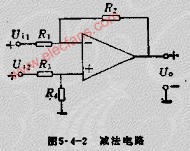

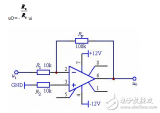

减法运算电路

图6-4 减法运算电路

2009-03-09 10:11:43 5254

5254

减法运算

同加法运算一样,减法运算可采用减法器来实现。半减器和全减器的设计方法和步骤与设计加法器相同。实用上,为了简化系统结构,通常不另外设计减

2009-04-07 10:38:39 12841

12841

高速流水线浮点加法器的FPGA实现

0 引言现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操

2010-02-04 10:50:23 2042

2042

本的二进制加法/减法器,本的二进制加法/减法器原理

两个二进制数字Ai,Bi和一个进位输入Ci相加,产生一个和输出Si,以及一个进位输

2010-04-13 11:11:55 5132

5132 多功能算术/逻辑运算单元(ALU) ,什么是多功能算术/逻辑运算单元(ALU)

由一位全加器(FA)构成的行波进位加法器,它可以实现补码数的加法运算和减法运算。但是这种加法/

2010-04-13 11:24:11 26139

26139 补码加法,补码加法计算原理 负数用补码表示后,可以和正数一样来处理。这样,运算器里只需要一个加法器就可以了,不必为了负数的加法运算,再配一个减

2010-04-13 11:41:28 17214

17214 补码减法,补码减法原理是什么? 负数的减法运算也要设法化为加法来做,其所以使用这种方法而不使用直接减法,是因为它可以和常规的加法运算使用同一

2010-04-13 11:45:46 6326

6326 减法电路

减法电路和加法电路实质相同,在求和电路中预先将某些信号倒相就可以成为求差电路或混合电路。

差动输入运算放大器

2010-04-22 17:46:36 19723

19723

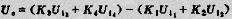

加减法电路

利用一个差动输入的运放就可同时实现加减法运算,这种运算电路如图5.4-3所示。

2010-04-22 17:50:08 9986

9986

由输入端选择运算方式的加、减法运算电路

电路的功能

这是一种配

2010-05-08 11:32:23 1518

1518

高输入电阻减法运算电路(A-B)

电路功能

因为输入电阻高,所以信

2010-05-08 13:16:38 5357

5357

加法运算是数字系统中最基本的算术运算。为了能更好地利用加法器实现减法、乘法、除法、码制转换等运算,提出用Multisim虚拟仿真软件中的逻辑转换仪、字信号发生器、逻辑分析仪

2011-05-06 15:55:07 82

82 德赢Vwin官网

为您提供了运算放大加法器电路图!

2011-06-27 09:28:50 7732

7732

该ALU采取层次化设计方法,由控制模块、逻辑模块、加减法模块、乘法模块和除法模块组成,能实现32位有符号数和无符号数的加减乘除运算,另外还能实现9种逻辑运算、6种移位运算以

2012-02-09 15:24:55 80

80 浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计

2012-07-06 15:05:42 47

47 8位加法器和减法器设计实习报告

2013-09-04 14:53:33 133

133 为了缩短加法电路运行时间,提高FPGA运行效率,利用选择进位算法和差额分组算法用硬件电路实现32位加法器,差额分组中的加法单元是利用一种改进的超前进位算法实现,选择进位算

2013-09-18 14:32:05 33

33 基于FPGA的开方运算实现 ,的技术论文

2015-10-30 10:59:01 5

5 加法运算电路能实现多个模拟量的求和运算。图1所示为一个3个输入信号的反相加法运算电路。

2017-05-15 09:41:34 195023

195023

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。减法电路是基本集成运放电路的一种,减法电路可以由反相加法电路构成,也可以由差分电路构成。基本集成运放电路有加、减、积分和微分等四种运算。一般是由集成运放外加反馈网络所构成的运算电路来实现。

2017-08-16 11:09:48 159697

159697

集成运算放大器是一种具有高电压放大倍数的直接耦合多级放大电路。当外部接入不同的线性或非线性元器件组成负反馈电路时,可以灵活地实现各种特定的函数关系。在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。

2017-08-18 17:26:18 22855

22855

针对一类乘同余运算,提出了一种快速算法。采用1个32位乘法、2个32位加法、少量移位操作和一个最高位分离操作方法,避免了连续减法和除法运算。

2017-09-07 20:10:57 3

3 运算电路是集成运算放大器的基本应用电路,它是集成运放的线性应用。讨论的是模拟信号的加法、减法积分和微分、对数和反对数(指数)、以及乘法和除法运算。

2017-11-27 15:55:10 0

0 结构复杂,采用DSP实现会增加系统负担,降低系统速度。在某些对速度要求较高的情况,必须采用专门的浮点运算处理器。 EDA/FPGA技术不断发展,其高速、应用灵活、低成本的优点使其广泛应用数字信号处理领域。在FPCA技术应用的初期,

2018-04-10 14:25:53 17

17 本文是基于FPGA实现Cordic算法的设计与验证,使用Verilog HDL设计,初步可实现正弦、余弦、反正切函数的实现。将复杂的运算转化成FPGA擅长的加减法和乘法,而乘法运算可以用移位运算代替

2018-07-03 10:18:00 2349

2349

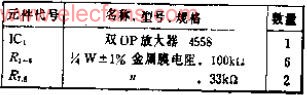

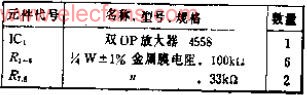

4.1.3加法和减法运算电路

2019-04-18 06:03:00 15197

15197

我通常会喜欢简洁化。有些人设计喜欢做加法,我们设计喜欢做减法。

2019-03-21 15:52:45 3718

3718 本文档的主要内容详细介绍的是模拟电路实验教程之基本运算电路的详细资料说明。一。实验目的1.掌握反相比例运算、同相比例运算、加法、减法运算电路的原理,设计方法及测试方法。2.能正确分析运算精度与运算电路中各元件参数之间的关系。

2019-05-27 17:26:51 22

22 图2列出了和传统的4输入LUT结构的FPGA相比较,采用ALM的StratixⅡFPGA器件例化3输入加法器的优势。从图2中可以清楚地看出,对于同样3个2 b数据相加的逻辑结构,传统4输入LUT结构

2020-03-03 10:45:37 1015

1015

开方运算作为数字信号处理(DSP)领域内的一种基本运算,其基于现场可编程门列(FPGA)的工程实现具有较高的难度。本文分析比较了实现开方运算的牛顿-莱福森算法,逐次逼近算法,非冗余开方算法3种算法

2020-08-06 17:58:15 6

6 所示是减法运算电路,讹通过Ri加到运算放大器的反相输入端,蚰通过R2、R3分压后加到同向输入端,而抽通过Rf反馈到反相输入端。为了使运算放大器两输入端平衡,则}Rl/,RrRzllR3。

2020-09-10 11:07:12 31519

31519

1、集成运算放大器是一种电压放大倍数极高的直接耦合多级放大电路。当外部接入不同的线性或非线性元器件组成负反馈电路时,可以灵活地实现各种特定的函数关系。在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。

2020-11-16 08:00:00 26

26 (1) 标号: BCDA 功能:多字节BCD码加法 给大家介绍一个单片机汇编语言写的多字节BCD码加法减法子程序 入口条件:字节数在R7中,被加数在[R0]中,加数在[R1]中。出口信息:和在[R0]中,最高位进位在CY中。

2020-12-06 17:31:00 8019

8019 有些FPGA中是不能直接对浮点数进行操作的,只能采用定点数进行数值运算。对于FPGA而言,参与数学运算的书就是16位的整型数,但如果数学运算中出现小数怎么办呢?要知道,FPGA对小数是无能为力

2021-08-12 09:53:39 4504

4504 一:算术运算符算术运算符非常地简单,就是小学数学里面的一些加减乘除操作。不过呢,还是有一些语法细节需要注意的。1.加法运算符 + 1 在第3行利用加法运算符 + 进行了加法运算,再将和赋值给了变量

2021-11-20 20:06:09 2

2 FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成。因此FPGA实现除法运算并不是一个“/”号可以解决的。

2022-04-27 09:16:03 6098

6098 指针的加法操作我们见过很多,但是减法操作遇到的好像很少。

2023-03-29 10:12:35 388

388 本文是本系列的第二篇,本文主要介绍FPGA常用运算模块-加减法器和乘法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:13:57 2625

2625

真空衰减法是一种无损、定量的检测非多孔、刚性或柔性包装泄漏的方法。压力衰减测试是一种用于检测无孔、刚性或柔性包装中泄漏的定量测量方法。如果加压气体的引人导致包装壁或密封件破裂,则该测试是破坏性

2023-07-27 15:21:41 732

732

,浮点加法器是现代信号处理系统中最重要的部件之一。FPGA是当前数字电路研究开发的一种重要实现形式,它与全定制ASIC电路相比,具有开发周期短、成本低等优点。 但多数FPGA不支持浮点运算,这使FPGA在数值计算、数据分析和信号处理等方

2023-09-22 10:40:03 394

394

前段时间和几个人闲谈,看看在FPGA里面实现一个Mem加法器怎么玩儿

2023-10-17 10:22:25 279

279

在电子技术的海洋中,有一种电路如同数学中的加法器一样,能够将不同的信号进行相加处理。这就是被广泛应用于信号处理领域的反相加法运算电路。

2024-02-17 15:34:00 378

378

反相加法运算电路利用运算放大器(通常简称为Op-Amp)的特性来实现多个输入信号的加法运算。每个输入信号都通过一个电阻连接到运算放大器的反相输入端,而运算放大器的同相输入端则接地或虚拟接地。输出电压

2024-01-31 15:53:51 270

270

异或门可以用于实现二进制数的加减法。例如,我们可以使用异或门来实现两个二进制数的加法,如果两个相应的输入端上输入的数相同时则进行减法运算。

2024-02-04 14:47:09 740

740

元器件的限制。当时,计算机的电路设计主要采用位操作(二进制)来实现。为了能够有效地表示负数,人们引入了反码的概念。使用反码可以使计算机系统在进行加法和减法运算时使用相同的逻辑电路,从而降低了硬件成本和复杂度。 2.

2024-02-19 15:10:32 147

147

德赢Vwin官网

App

德赢Vwin官网

App

评论